基于AD574A的脑电信号采集及在线仿真

FPGA/ASIC技术

描述

一、引言

脑电信号EEG(Electroencephalogram)是一种微弱的低频生理信号。它由脑部神经活动产生的自发性电位活动,含有非常丰富的大脑活动信息,是进行临床脑疾病诊断的一种重要方法,因此获取脑电信号具有重要的现实意义。目前的大多数脑电信号采集系统均采用单片机作为控制器,由于脑电信号是毫伏级或微伏级的信号,精度较低。本文根据脑电信号的特点,将电极采集到的模拟信号经信号调理后,采用FPGA芯片EP2C8Q208C8来控制AD574A的转换,给出了硬件连接电路和软件实现,并且在QuartusII9.0中进行仿真验证,从而提高系统的可靠性和通用性,具有实际应用参考价值。

二、脑电信号采集系统概述

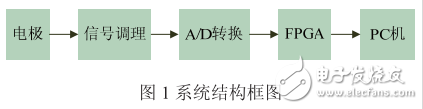

脑电信号监测在临床疾病诊断中具有一定的应用价值。系统首先采用电极获取大脑皮层的电信号,再通过信号调理电路进行处理,然后以FPGA为核心控制AD574A进行模数转换与存储,最后对采集的信号作进一步的算法分析,并实现与上位机的通信从而实现在线监测。系统的结构框图如图1所示。

三、系统硬件设计

系统的硬件电路包括信号放大和滤波电路,A/D转换电路,FPGA控制电路,FPGA与PC机通信电路构成。本文主要介绍采用FPGA来控制AD574A的采样过程。

1、AD574A简介

AD574A是一种高速12位逐次比较型模数转换器,它由美国AD公司推出,内置混合集成转换芯片,具有外接元器件较少、低功耗、高精度等优点,还具有自动校零和极性转换功能。其主要特性表现为:分辨率12位;非线性误差小于±1/2LBS或±1LBS;转换时间25μs;模拟输入电压有0~10V、1~20V、0~±10V和0~±5V四种;电源电压为±15V和15V;数据输出12位或8位;可工作在全速工作和单一工作两种模式下。

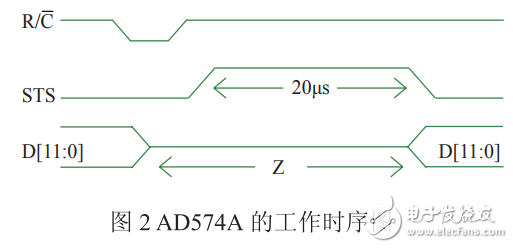

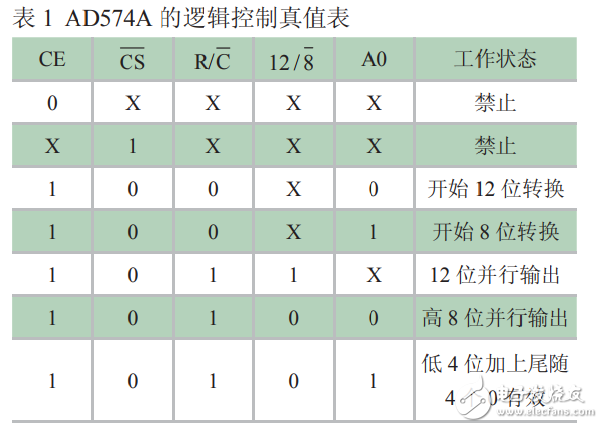

AD574A的逻辑控制真值表和工作时序图分别如表1和图2所示。由图表可知AD574A的工作过程包括:启动转换和读出数据。

进行启动转换时,先令CS/=0、CE=1,根据所需转换的位数A0取1或0,然后使R/C=0,转换开始。转换完成时,STS由高电平变为低电平。通过读入STS的状态,判断转换是否完成。进行数据输出时,先根据输出数据的方式,来确定是接高电平还是低电平;接着令CE=1、CS/=1、R/C=1,确定A0的取值。如果分两次输出12位数据,A0为0时输出高8位,A0为1时输出低4位;如果是12位并行输出,A取值任意。

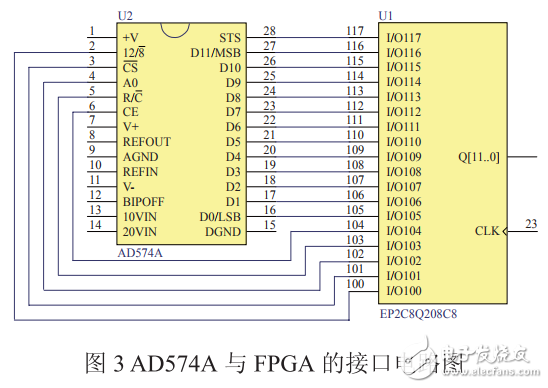

2、AD574A与FPGA的接口电路

系统采用FPGA来控制AD574A的工作时序,进行A/D转换,然后将转换后的数据以十六进制的数据显示出来。选择的FPGA芯片为Altera公司CycloneII系列的EP2C8Q208C8,其与AD574A的硬件连接图如图3所示。首先FPGA输出使CS/、CE有效,处于转换工作状态,然后使R/C启动转换。转换结束,FPGA在STS由高电平变为低电平之前不能读取转换数据。当STS变成低电平之后,FPGA便可将输出信号拉高,这样转换的数据就会呈现在数据线上,FPAG读入该数据后,在数码管上显示出来。

四、软件实现

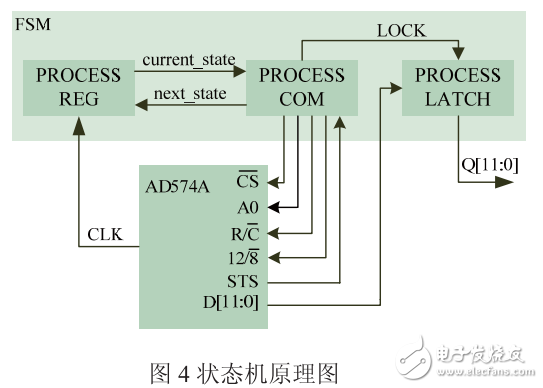

根据AD574A的工作原理,在QuartusII9.0中采用VHDL进行程序设计。针对系统的高速和可靠性要求,软件设计采用有限状态机FSM控制,其原理图如图4所示。包括主控时序进程(REG),主控组合进程(COM)和辅助进程(LATCH)。

其中主控组合进程的VHDL如下:

COM1: PROCESS(c_st,STS)

BEGIN CASE c_st IS

WHEN s0=> n_st <= s1;

WHEN s1=> n_st <= s2;

WHEN s2=> IF (STS='1') THEN n_st<= s2;

ELSE n_st <= s3;

END IF;

WHEN s3=> n_st <= s4;

WHEN s4=> n_st <=s0;

WHEN OTHERS => n_st <= s0;

END CASE ;

END PROCESS COM1 ;

COM2: PROCESS(c_st)

BEGIN

CASE c_st IS

WHEN s0=>CS<='1';A0<='1';RC<='1';LOCK<='0'; --初始化

WHEN s1=>CS<='0';A0<='0';RC<='0';LOCK<='0'; --启动转换

WHEN s2=>CS<='0';A0<='0';RC<='0';LOCK<='0'; --等待转换

WHEN s3=>CS<='0';A0<='0';RC<='1';LOCK<='0';--12 位并行输出有效

WHEN s4=>CS<='0';A0<='0';RC<='1';LOCK<='1'; --锁存数据

WHEN OTHERS =>CS<='1';A0<='1';RC<='1';LOCK<='0'; -- 返回初始态

END CASE ;

END PROCESS COM2 ;主控时序进程的 VHDL 如下:

REG: PROCESS (CLK)

BEGIN

IF (CLK'EVENT AND CLK='1') THEN c_st <= n_st;

END IF;

END PROCESS REG ;

采样后的数据可在FPGA中进一步处理,并进行实时控制,也可送至计算机进行处理。

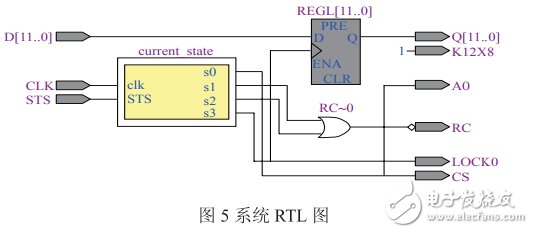

在QuartusII9.0中选择Tools菜单中的RTLViewer项,可以打开系统的RTL电路图,如图5所示。通过双击有关模块,可以逐层了解各模块的电路结构。

五、仿真结果

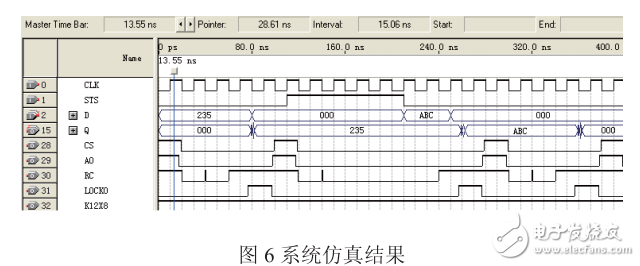

系统的仿真结果如图6所示,首先初始化CS《=‘1’,A0《=‘1’,RC《=‘1’,LOCK《=‘0’;接着启动转换CS《=‘0’,A0《=‘0’,RC《=‘0’;然后保持该状态直到RC《=‘1’时,转换好的数据输出,在STS由高电平变为低电平之后读取转换数据。图中,转换好的数据235送到输出端Q[11:0]。

六、结语

脑电信号采集可以为医生提供可靠的诊断信息,有助于病人的准确治疗。而在脑电信号的获取中的一个关键环节是采集的高效性。基于FPGA在高速数据采集方面的优点,通过对AD574A的研究,设计了硬件连接电路,并进行仿真验证。实践证明系统具有较高的可靠性和通用性,具有一定的实际应用价值。

-

基于FPGA和高速串门A/D转换器实现脑电信号数据采集系统的设计2021-04-14 6466

-

使用ADS1299进行脑电信号采集时采集不到脑电信号,怎么解决?2024-11-13 471

-

使用两片ADS1299搭建电路,为什么采集不到脑电信号?2024-11-14 385

-

使用ADS1299采集心电和脑电信号,采集人体信号都是工频,应该如何改进?2024-11-22 507

-

基于PSoC脑电信号采集系统2012-11-22 5277

-

基于labview的脑电信号处理2017-04-10 7473

-

怎么处理基于DSP Builder的脑电信号?2019-08-23 2721

-

怎么设计基于ADS1298与FPGA的高性能脑电信号采集系统?2019-09-27 3775

-

怎样去设计一种脑电信号采集与传输系统?2021-05-18 2175

-

基于MSF的脑电信号消噪2010-01-27 1040

-

AD977A在脑电信号采集系统中的应用2010-12-25 678

-

脑电信号(EEG)分类方法2011-01-07 1493

-

基于SOPC的脑电信号实时处理2012-06-04 1146

-

基于小波分析的脑电信号处理2013-01-10 880

-

关于MCU与虚拟仪器的脑电信号采集系统2018-04-27 1321

全部0条评论

快来发表一下你的评论吧 !