基于FPGA的ADS1256芯片控制器设计

控制/MCU

描述

模数转换即将模拟信号进行数字化处理,得到与原始信号近似的离散的数字量,用数字信号以bit位单位编码量化表示原始信号,这种量化目前由ADC(模数转换)芯片的硬件实现,对芯片的控制可以根据系统特占通过DSP(数字信号处理器)、ASIC(专用集成电路)和FPGA(现场可编程门阵列)三种不同方式完成。[2]采用FPGA的方式适合与对速率要求较高的可编程环境,本设计使用Xilinx公司Spartan3E的FPGA通过对TI的ADS1256芯片控制并完成模数转换功能。

ADS1256芯片介绍

ADS1256芯片是一种高速低噪声的24位模拟-数字(A/D)转换器,能够提供完整的高分辨率模拟信号测量解决方案。ADS1256内部具有利用滤波器稳定的缓冲区和可编程的增益放大器进一步降低了信号噪声,信号采样率高达30Ksps可以满足卫生和植物检疫标准。在外部接口方面,ADS1256具有SPI兼容的5V串行接口,模拟信号的输入电压为5V,数字信号的输出电压为1.8V~3.6V。标准工作模式下功耗为38mW,待机模式下的功耗为0.4mW。

总体及接口设计

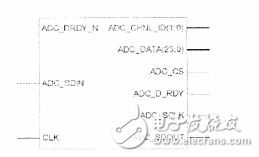

利用FPGA完成的控制系统输入输出接口如图3所示,其一端可以与ADS1256芯片相连,另一端可以将芯片输出的数字信号组合成24bit精度的数据送出,用以连接设计者需要此数据的其它器件。

控制系统输入输出接口

输入端:

(1)CLK:连接外部20MHz系统主时钟,用来驱动主控FPGA工作;

(2)ADC_DRDY_N:A/D数据转换准备好信号,连接ADS1256的/DRDY引脚,用来通知主控FPGA本次模数转换完成;

(3)ADC_SDIN:主控FPGA的SPI串行数据输出信号,连接ADS1256的DIN引脚,配置ADS1256芯片寄存器;(4)ADC_CHNL_ID(1:0):为A/D转换后的数字信号的输入通道,连接ADS1256的D0、D1。

输出端:

(1)ADC_CS:ADS1256的芯片的使能信号,连接ADS1256的/CS引脚;

(2)ADC_DATA(23:0):为最终数据的并行输出引脚,可连接其它所需器件;

(3)ADC_D_RDY:与ADC_DATA配合使用,指示ADC_DATA有效;(5)ADC_SCLK:利用系统主时钟CLK分频出的SPI时钟,连接ADS1256的SCLK;

(4)ADC_SDOUT:主控FPGA的SPI串行数据输入信号,与ADS1256的DOUT相连。

功能实现

整体模块的设计应该包含以下子功能模块:

(1)时钟模块“clk_gen”对20MHz的主时钟分频产生供SPI使用的占空比为50%的2MHz时钟和4MHz的时钟;(2)延迟模块“delay_n”在系统上电后延迟一段时间,等待供电稳定后再初始化A/D启动A/D转换,减少系统上电时对模拟信号输入的瞬时影响,保证ADC转换时可输出稳定的数据;

(3)初始化模块“adc_initial”,它的功能是通过SPI接口对ADS1256进行初始化,根据芯片使用说明按步骤设定它进入工作状态;

(4)AD转换控制模块“adc_xchange“,它的功能是产生ADS1256需要的时序,把控制字通过SPI发送到ADS1256,并最终根据芯片指示读出A/D转换后的数字信号。

在FPGA上完成的ADS1256芯片控制系统的RTL结构图如下图所示:

SRL16E的应用

系统中采用Xilinx原语SRL16E构成的16位移位寄存器进行时钟控制,可以通过以下公式进行计算:

数据输出位数=8*A3+4*A2+2*A1+1*A0+1例如本系统采用20Mhz的系统主时钟,要进行5分频得到4M的SPI接口工作时钟,只需将A3,A2,D1,D0设置为0,1,0,0(8*0+4*1+2*0+1*0+1=5)即可。

本设计中使用SRL16E而没有采用锁存器(PLL)进行时钟的分频,可以进一步节省FPGA的硬件资源。

因为FPGA中每个查找表LUT能够构成一个16位的移位寄存器,它可以通过对Xilinx定义的系统宏SRL16E的调用来实现。由于LUT中能够提供一个16位的同步RAM。利用SRL16E这种存储的能力设计递归的延迟线(RDL),再根据RDL抽样个数倍减而速率倍增的特点与时分复用技术相结合,构成递归折叠结构。最终以提高主工作时钟频率的代价,增大了采样速率以及相关运算单元的吞吐率,并且极大的降低了资源的使用。

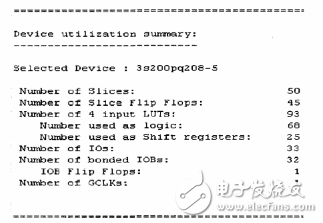

本设计中采用了1/4的递归折叠结构,资源消耗仅为优化前的1/3。如下图所示,为FPGA的资源使用情况。

FPGA的资源使用。

-

ADS1256模数转换器的驱动设计与实现2022-12-07 7429

-

ADS1256芯片用SPI控制,这个SPI的时钟要怎么设置?2024-12-20 651

-

ADS1256支持菊花链连接吗?2024-12-24 510

-

ADS1256有什么优势呢?2025-01-16 415

-

ADS1256选型参考资料精华选集2018-08-29 5102

-

介绍一下ADS1256的初始化2022-01-21 4529

-

ADS1256/ADS1256 pdf datasheet(2008-07-31 1551

-

8通道24位∑型模数转换器ADS1256原理及特点2016-06-06 1552

-

ads1256中文资料汇总_功能原理图及说明_ads1256驱动程序源代码2017-12-20 78955

-

ADS1256在高精度数据采集系统的应用2017-12-21 9940

-

ADS1255,ADS1256和陶瓷谐振器的评估方法及其最终报告的详细资料概述2018-05-18 1973

-

ADS1256应用模块资料包2022-06-17 1101

-

带有ATmega32U4的定制ADS1256板2022-08-04 1052

-

ADS1256+STM32F103RCTx示例程序2023-09-07 1247

-

STM32驱动ADS1256串口输出-AD转换2025-07-01 2499

全部0条评论

快来发表一下你的评论吧 !