74ls192工作原理详解_使用说明_内部逻辑图及应用电路

应用电子电路

965人已加入

描述

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能。

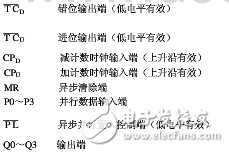

74ls192工作原理

74ls192使用说明

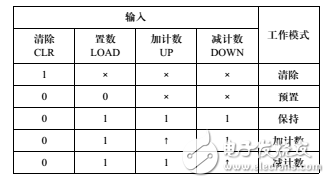

74LS192是同步十进制可逆计数器,具有同步预置数端和异步清零端,可以直接级联而无需外接电路,借位和进位两输出端可级联递增计数和递减计数,使用方便。功能表如下表所示。

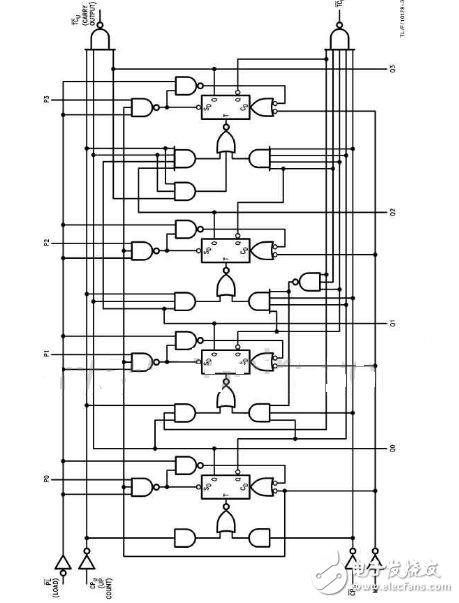

74ls192内部逻辑图

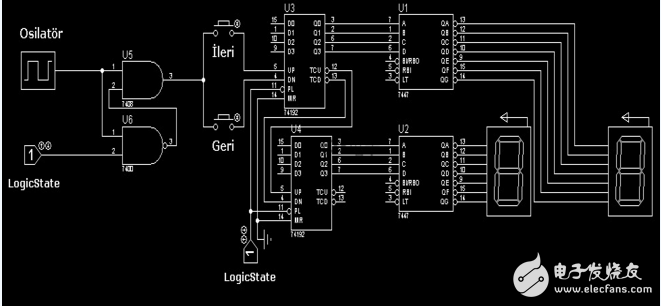

74ls192应用电路

本电路复杂程度为55个等效门。本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。

本工作方式避免了一般用异步(行波时钟)计数器所带来的计数输出的尖峰脉冲。四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。计数方向在其它计数输入端为“高”时,由脉冲的计数输入端所定。本电路为全可编程的,当置数输入为“低”时,把所希望的数据送入数据输入端上,来把每个输出端预置到两电平之一。输出将符合独立于计数脉冲的数据输入的改变。

该特点可使电路以预置输入而简单地更改计数长度,用作N模数分频器(除法器)。清零输入在加高电平时,迫使所有输出端为低电平。清零功能独立于计数输入和置数输入。清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。本电路都设计成可被直接级联而勿需外接电路。借位和进位两输出端可级联递增计数和递减计数两功能。借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时,产生宽度等于递加计数输入的脉冲。

推荐详细资料>>>>>>>74LS192中文资料pdf

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 7

-

74ls192的功能及原理2024-01-22 34088

-

74ls192加减无法正常工作的原因2021-12-07 6857

-

74ls92中文资料汇总(74ls92引脚图及功能表_逻辑图及工作原理)2018-05-29 52810

-

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)2018-05-28 148373

-

74ls162中文资料汇总(74ls162引脚图及功能_逻辑图_特性参数及应用电路)2018-05-08 109706

-

74ls86中文资料汇总(74ls86引脚图_内部逻辑图及应用电路)2018-04-28 261336

-

74ls153管脚及功能表_真值表逻辑图及应用电路2018-01-26 613390

-

74ls192和74ls160的区别有哪些2017-12-21 35626

-

74LS192英文手册2016-11-21 1689

-

74LS192 英版数据手册2016-08-31 2075

-

74ls138译码器内部电路逻辑图功能表简单应用2009-07-13 67863

-

74LS192 pdf datasheet2008-08-06 2343

-

74LS192中文资料pdf2008-03-18 7642

-

74ls192真值表2007-11-29 21184

全部0条评论

快来发表一下你的评论吧 !