从模拟电路的角度谈谈静电保护

描述

这期文章,作者君想从模拟电路的角度,给大家讲讲一个对于模拟工程师来说,既熟悉又有点陌生的内容:ESD Electrostatic discharge, 也就是所谓的“静电保护”。

Wikipedia里面是这样定义的:Electrostatic discharge (ESD) is the sudden flow of electricity between two electrically charged objects caused by contact。翻译过来呢,就是指两个储存有电荷的物体相互接触时候产生的瞬时电流。

最近作者君做的项目呢,对于ESD的要求比较严格,就经常和一个ESD部门的哥们讨论学习一下。他告诉我说,ESD可以在任何地方发生,无论是制造,生产,装配,测试,甚至运输及现场应用。当时我就有一种想放弃治疗的想法。。。。

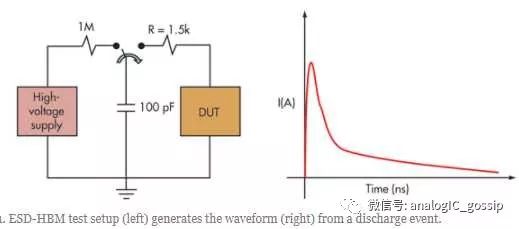

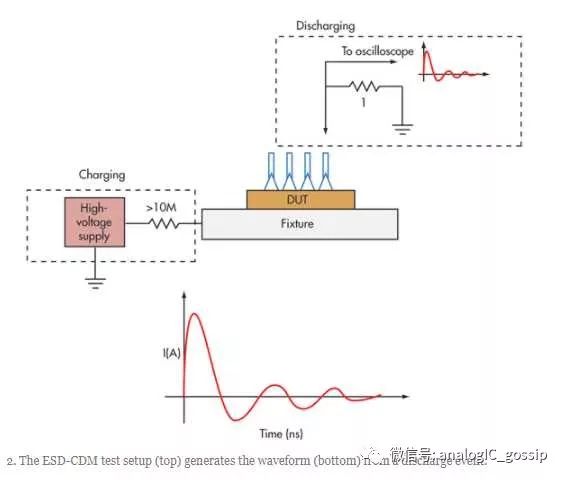

那么,问题来了,我们怎么在电路中对其进行模拟并仿真呢?一般我们熟悉并且在电路仿真里面需要用到的模型有两种:CDM和HBM.

CDM就是所谓的Charge Device Model,HBM就是所谓的Human Body Model。

两者对比可以看出,一般来说CDM的电流比HBM的电流大一些、也快一些,因为并无较大的电阻在放电通路上面限制放电的过程。

因此,在ESD的仿真中,需要在supply上添加这样一个pulse电压。例如在某个工艺情况里:CDM情况下,supply上面需要加入一个高达15V的pulse,上升沿和下降沿都是200ps,持续4ns。而在HBM的情况下,这个pulse的peak电压仅仅只是6V,上升沿和下降沿是2ns,持续时间400ns。

这里插入一句那个哥们的话:“我们就是计算这种 secondary 的ESD的相关数值给你们用的啦。”说罢,事了拂衣去,深藏身与名。。。(说白了就是不告诉你怎么算,气死你……)

等等,为什么上来就说到了secondary ESD protection呢?既然有secondary ESD protection,那primary ESD protection在哪里呢?

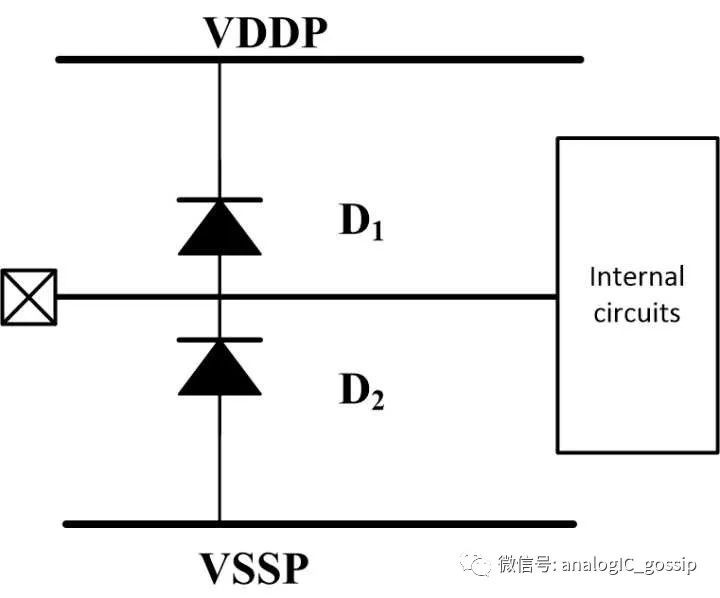

我们熟悉的IO结构,那种上下各有一个diode的pad,就是primary esd protection:

通用型的带ESD保护的IO

比如HBM模型里面,IO被加上一个+2000V的高压,则上面的diode D1就自然导通了,外界的高压顺着VDDP被迅速导走。同理,若是加上一个-2000V的高压,D2就导通了,大电流从VSSP快速流向IO,也未伤及内部的电路。

在这里,作者君想问大家一个问题:VDDP和VSSP都是给IO的diode们提供偏置的supply。那么VDDP和VSSP的IO 又当是怎么样的呢?还能上下各放一个diode吗?

快速思考一秒后……

肯定不能是这样的嘛!感觉就是不能这样……

那没有了上下两个diode,要如何保护VDDP和VSSP的IO呢?

嘿嘿,不如去看看VDDP和VSSP的IO电路好了!

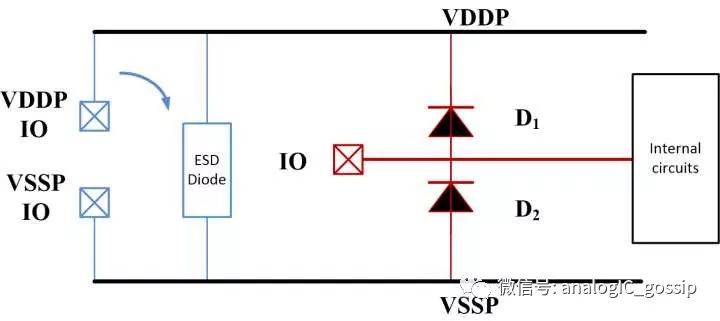

包括了IO的ESD protection的pad模型

因此,此处应当有另外的ESD保护电路在VDDP的IO和VSSP的IO之间。比如VDDP被加上+2000V的高压时,通过这个ESD diode快速导走高压电流。而当VDDP是0,而VSSP被加上+2000V的高压时,这个……

等等,容在下先想想,这里有两个方向相反的diode吗?

……

一秒后。

如果VSSP被加上了+2000V,那么岂不是所有的IO都挺热闹了?

为什么这么说?

嘿嘿,所有的nwell都是被VDDP给biased成为0V,而substrate因为VSSP变成了2000V,那么,岂不是所有的nwell和sub之间的寄生diode都被打开了?

哇!想想看,听起来好欢乐的场景啊!

然后,作者君听说,还有一个所谓的“1 Ohm”原则,据说是从IO到那些esd diode之间的导通电阻必须要小于1 Ohm,以免寄生电阻太大,影响了快速放电的效果,避免有些“漏网之鱼”流到内部电路里面去了。所以大家若是仔细看看IO的版图,会发现那里metal真是密密麻麻的,“无所不用其极”。

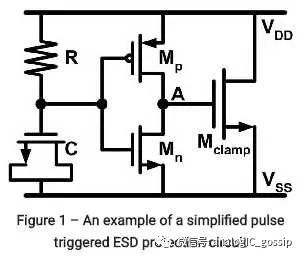

最后,再多说一个小的电路(懒得画图,所以拿来借用一下):

这也是一个ESD的保护电路。为什么要说这个呢?因为作者君昨天刚刚被要求在自己内部的电路上面加一个nmos的switch,这个nmos的gate就是图中A点。而且被人告知,这也是secondary ESD protection。(请大家注意,这个fig.1是io的一部分,那个大的nmos Mclamp并不是内部电路。这里是在说内部电路可以使用io的内部节点进行控制)

我们简单分析一下:如果VDD上面有高压pulse的时候,因为电容的电压滞后作用,电容上面的电压并没有跟着VDD迅速提高。因此此时Mp的gate电压值比source小了不少,导致Mp导通,A点也被连到了VDD上面,巨大size的Mclamp被打开,VDD和VSS通过Mclamp连在了一起。这样一来,VDD上面的pulse就这样被巨大的Mclamp给导走了,因此,我们脆弱的内部电路也就被保护了起来。

再回到作者君被要求加switch的地方。那个nmos的switch其实类似于一个power down的功能,只是被图中的A点控制着。当出现很严峻的ESD event的时候,内部电路能关断的赶紧关断,千万不能给ESD的大电流有可乘之机。

最后推荐大家一篇博士论文:http://www-tcad.stanford.edu/tcad/pubs/theses/ShuqingCao.pdftp://http://www-tcad.stanford.edu/tcad/pubs/theses/ShuqingCao.pdf

这篇论文里面还很详细的讲了随着工艺的缩小,所谓的ESD Design Window是如何越来越小的。因为gate oxide的尺寸越来越小,gate的击穿电压也会变小,ESD protection的可以使用的范围也越来越小。听起来真是很可怜!

据作者君的比较,0.18um的IO和28nm的IO大小并无很大区别(甚至28nm的似乎看起来更大一些)。花了那么多力气减小工艺尺寸,即使内部电路变小,却被IO的面积给瓶颈了。这真是个悲伤的故事啊!

最后多说一句:ESD经常跟leakage之间需要tradeoff。esd diode太大,protection变好,leakage却会变得比较恶劣,影响正常工作时的性能。需要使用的时候权衡利弊。

-

eSATA静电保护方案上海雷卯电子科技有限公司 2023-04-19

-

快速触发的静电保护电路及方法2009-11-24 3595

-

mosfet有内部静电保护吗?2011-10-21 2069

-

ESD静电保护器的选型及应用2016-05-26 2786

-

ESD静电保护器件的特点2018-01-26 4907

-

选择ESD静电保护元件的参考因素2020-12-15 2979

-

HDMI接口静电保护解决方案2020-12-31 5245

-

电路设计中如何进行静电保护2021-01-21 1606

-

一种常见的ESD静电保护器件2021-03-11 3273

-

电路设计静电保护的几种方法?2021-03-17 2188

-

CAN静电保护方案2023-10-09 778

-

ESD静电保护管的工作原理2022-09-22 8397

-

静电保护器件ESD是什么?如何选型?2023-02-27 7885

-

K课堂丨ESD静电保护管的工作原理2023-06-05 3742

-

物联网中常见的静电保护电路设计方案_ESD静电保护管2024-09-29 2194

全部0条评论

快来发表一下你的评论吧 !