如何克服裸芯片动态特性表征中的挑战,实现高效测量?

描述

功率半导体器件以多种形式使用——封装为表面贴装器件(SMD)或功率模块——广泛应用于各种场景。功率半导体中包含的裸芯片必须在被放入封装或功率模块之前进行特性表征,以加速开发。然而,裸芯片的尺寸小、结构脆弱,以及探针引起的寄生效应,使得这一过程面临多重挑战。

功率半导体器件最初在晶圆上制造,之后进行切割和封装,才能用于实际的电力电子电路。在制造过程的早期阶段进行特性表征,有助于加速器件的开发。对于功率模块开发工程师来说,了解功率半导体裸芯片的行为,有助于加快开发进程并辅助故障排查。

功率半导体裸芯片动态特性表征的挑战

功率半导体裸芯片的静态特性表征相对简单。芯片被牢固地固定在电导性台上以进行漏极接触,而源极和栅极则通过探针从芯片的顶部探测。与固定装置相关的寄生效应不会显著影响测量性能。可以使用曲线追踪仪或阻抗分析仪进行静态特性表征。

然而,功率半导体裸芯片的动态特性表征极为困难。首先,测试电路中的寄生效应会显著降低动态特性表征的性能,尤其是对于宽带隙功率半导体,其速度非常快。例如,探针针头引入额外的寄生效应,导致振荡和尖峰,从而使测量波形失真。这些探针针头在高电压信号下测试时还可能引发电弧。

SiC MOSFET、垂直GaN器件、Si MOSFET和IGBT具有垂直的器件结构,电流从芯片的顶部流向底部。这使得从上下两侧探测芯片变得极为困难。因此,必须对芯片的一侧进行焊接。然而,将芯片焊接和拆焊到印刷电路板(PCA)上既不方便,又加速了电路板的磨损,这使得测试变得不理想。

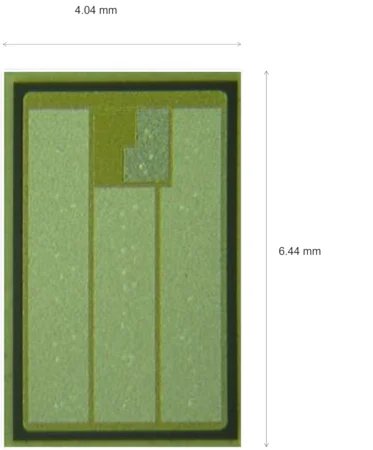

图1

图1

裸芯片在物理上非常脆弱。在固定过程中不平衡的力可能轻易导致芯片开裂或崩缺。此外,芯片的尺寸通常小于5mm,处理起来更为困难。此外,由于测试信号的快速di/dt(电流变化率)引起的电压浪涌,加上周围寄生电感,裸芯片可能会破损。

目前用于表征裸芯片的唯一方法是为该芯片创建一个完整的双脉冲测试(DPT)电路板。该电路板包括集成的PCA,配有栅极驱动器、银行电容、隔离组件及其他必要元件。芯片焊接在PCA的漏极侧,采用线焊接连接源极和栅极。通常情况下,芯片会涂上一层绝缘材料。

然而,这种设置仅在芯片特性表征时使用一次,因为PCB无法重复使用。相关的成本、时间、精力以及缺乏可重复使用性,使得工程师不愿频繁使用。

促进裸芯片动态特性表征的技术

实现裸芯片动态特性表征需要一些关键技术和方法。为裸芯片创建一个特殊夹具是解决方案中最重要的方面。这个特殊夹具必须满足以下要求:

· 不使用探针,以避免额外的寄生效应和电弧风险

· 夹具必须与裸芯片的垂直结构接触

· 与裸芯片的接触必须足够紧密,以确保电导,但又不能太紧,以避免物理开裂或崩缺

· 无需焊接的接触

· 一种对准小型裸芯片与测试夹具电极的机制

· 最小化测试夹具中的寄生效应(例如,<几个nH)

· 夹具应具备高电压和大电流能力(例如,600V和40A)

· 轻柔处理裸芯片以避免物理损伤

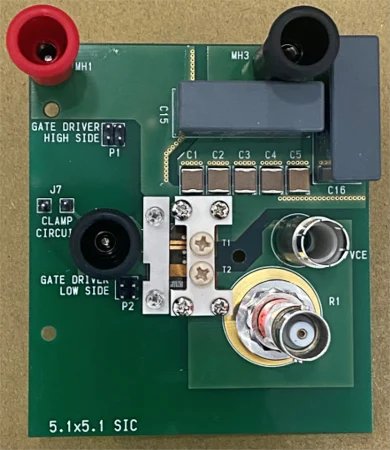

下面描述的解决方案利用了新开发的技术进行芯片动态测试,并实现了针对离散器件的双脉冲测试器。被测设备(DUT)电路板相对简单,如图2所示。相同的技术也可以应用于功率模块的双脉冲测试器,使功率模块工程师能够利用这一新方案对裸芯片和功率模块进行特性表征。

图2

图2

在DUT电路板上,对PCB的电极进行特殊处理,以实现无焊接接触。还使用了一种具有类似电极处理的柔性PCB进行顶部连接。通过将芯片放置在主PCB和柔性PCB之间,可以实现从芯片顶部到底部的电流流动,从而为垂直结构器件提供电流测量。

PCB设计旨在最小化功率环路和栅环路中的寄生电感。夹具具有精心设计的多个引脚,从PCA突出,以确保裸芯片准确对齐,从而与电极实现最佳接触。没有探针的存在进一步减少了测试电路中的寄生电感。

对于Si和SiC器件,可以使用同轴分流电阻,即使其额外插入电感在几个纳亨里(nH)的范围内。对于GaN(氮化镓)裸芯片,专利电流传感器提供了另一个减少寄生电感的手段。功率半导体裸芯片通常显示出不同的形状因素。因此,我们的策略是为Keysight PD1500A和PD1550A创建定制的DUT电路板,如图3所示。

图3

图3

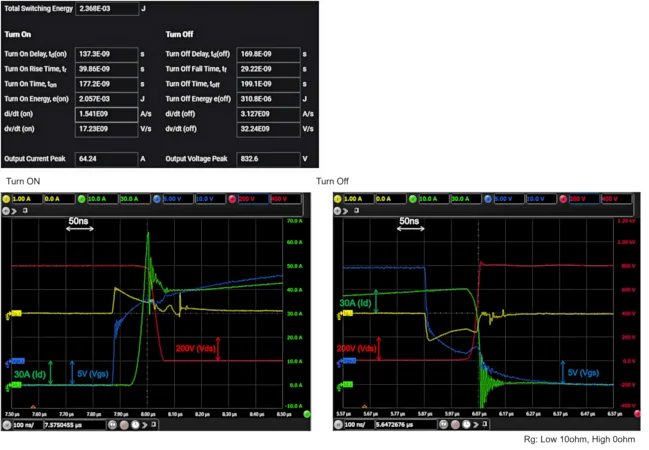

图4显示了对额定1.2 kV的SiC MOSFET裸芯片进行的示例测量结果。测试在800 V和40 A下进行,表明夹具为1.2 kV额定的SiC MOSFET提供了足够的电压和电流能力。波形非常干净,关断时只有小幅度的Vds超调。从开通波形计算出的功率环路电感仅为8.3 nH。

裸芯片夹具可以轻松与曲线追踪仪配合使用,消除了对裸芯片静态测量中晶圆探针的需求,极大地提高了生产力。

图4

图4

浮思特科技深耕功率器件领域,为客户提供IGBT、IPM模块等功率器件以及单片机(MCU)、触摸芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。

-

最新 MEMS 惯性模块如何帮助克服应用开发挑战2017-03-31 4510

-

测量系统的动态特性分析2018-01-24 10114

-

LTE系统射频特性测量2019-06-05 1229

-

LTE设备和系统射频特性的测量具有哪些挑战?2019-08-08 1417

-

想要完成高效电源时序测量,泰克示波器让您轻松应对挑战2020-02-07 1706

-

智能手机中实现环境光感测遇到的主要挑战有哪些?如何克服这些挑战?2021-03-08 3136

-

如何克服FPGA I/O引脚分配挑战?2021-05-06 1644

-

使用空中鼠标系统面临哪些挑战?如何去克服这些挑战?2021-05-10 2020

-

如何去克服基于云的物联网(IoT)配置挑战?2021-05-18 1967

-

浅析在低功耗应用中克服低IQ挑战2022-02-10 890

-

如何克服LoRa®终端节点设计中的挑战2023-07-13 1388

-

压接型IGBT芯片动态特性实验平台设计与实现2023-08-08 696

-

是德科技在宽禁带半导体裸片上实现动态测试而且无需焊接或探针2025-03-14 882

-

是德示波器如何精准测量第三代半导体SiC的动态特性2025-04-22 1053

-

泰克示波器如何精准测量半导体SiC的动态特性2025-10-17 394

全部0条评论

快来发表一下你的评论吧 !