功率MOSFET在电池管理充放电系统中的应用

描述

以下文章来源于PSD功率系统设计 ,作者Song Liu

功率MOSFET串联在锂离子电池组内部和输出负载之间

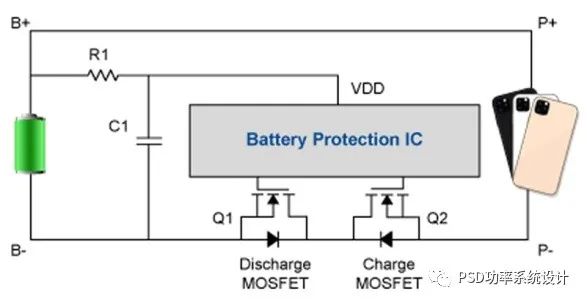

功率MOSFET需要在锂离子电池组内部和输出负载之间串联。同时,专用IC用于控制MOSFET的开启和关闭,以管理电池的充放电,如图1所示。在消费类电子系统中,如手机、笔记本电脑等,带有控制IC、功率MOSFET和其他电子元件的电路系统称为保护电路模块PCM。

图1:蓄电池保护板电路图

在PCM中,一个功率MOSFET用于充电,另一个用于放电。功率MOSFET以两种配置背靠背串联连接。一种配置是两个功率MOSFET漏极连接。在第二种配置中,连接两个功率MOSFET源。此外,有两种方法将功率MOSFET与电池串联。一种方法是将其放置在电池的负极,称为“接地端”或低压侧;另一种方法是将其放置在电池的正极端,称为高压侧。两种不同的功率MOSFET背靠背连接模式及其不同的放置方式各有优缺点,对应于不同的系统要求。

PCM需要低导通电阻MOSFET,因此通常使用N沟道功率MOSFET。由于驱动简单灵活,一些应用在正极端使用P沟道MOSFET。然而,P沟道MOSFET的导通电阻相对高于N沟道MOSFET,选择也受到限制。

功率MOSFET背靠背连接

工作原理

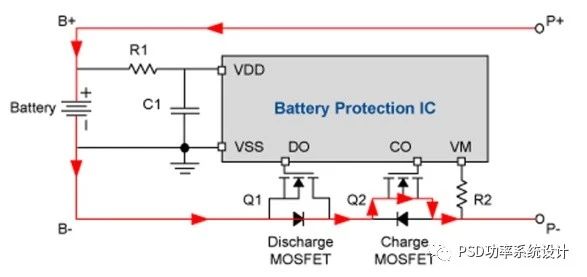

两个用于管理充电和放电的N沟道功率MOSFET放置在接地端,漏极背靠背连接,这是PCM的常见方案之一,如图2所示。其中,Q1是用于电池放电的功率MOSFET,Q2是用于电池充电的功率MOSFET,B+是电池的正极,B-是电池的负极,P+是电池组的正极,P-是电池组的负极,VSS是电池保护管理IC的接地,即电池的负极,VSS和Q1的电源连接。在PCM板工作之前,Q1和Q2都关闭。

(1)充电

充电时,控制IC栅极向充电功率MOSFET(Q2)提供驱动信号CO,Q2栅极的驱动信号路径为:外部充电电路的正端→ P+→B+→R1→VDD→CO→Q2源 →P-→外部充电电路的负极。当Q2接通时,充电电流路径为:P+→B+→B-→Q1内部寄生二极管→Q2通道→P-。然后可以对电池充电,如图2所示。

图2:Q2接通时的充电回路

为了减少Q1的损耗,当Q2开启时,将控制IC的DO引脚拉高,以使放电功率MOSFET Q1开启。由于Q1的RDS(ON)较低,其传导损耗远低于寄生二极管,充电效率可以提高。当Q2和Q1同时处于on状态时,充电电流路径为:P+B+ B-Q1通道Q2通道P-。

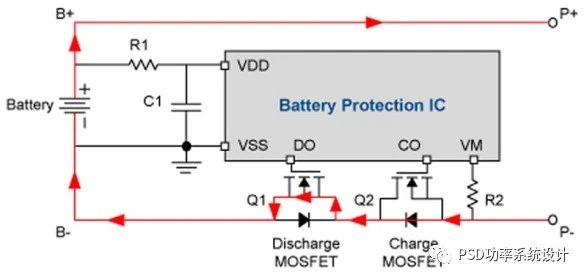

(2)放电

放电时,控制IC向放电功率MOSFET(Q1)提供栅极驱动信号DO,Q1的栅极驱动信号路径为:VDDDO(驱动器输出)Q1栅Q1源B-VSS。

当Q1为on时,放电电流路径为:P→Q2内部寄生二极管→Q1通道→B-→B+→P+。然后可以对电池进行放电,如图3所示。

图3:Q1开启时的放电回路

为了减少Q2的损耗,当Q1开启时,控制IC向充电功率MOSFET Q2提供栅极驱动信号CO,从而开启Q2。Q1和Q2同时处于开启状态。

功率MOSFET的性能要求

离子电池的容量从早期的600mAh、1000mAh,到现在已经达到6000mAh、10000mAh。为了实现更快的充电速度和更短的充电时间,通常采用增加电流和大电流充电的快速充电技术。那么,大电流充电对电池组中的功率MOSFET提出了更高的技术要求。此外,生产线和使用过程中对大容量锂离子电池有一些具体的技术要求。

功率密度高,功耗低,散热良好

大容量锂离子电池组设计的基本要求是尽可能提高电池的容量。因此,功率MOSFET需要更小的尺寸,在一定的尺寸限制下,如1.2mm*1.2mm,具有最小的导通电阻RDS(ON)。为了在较小的芯片尺寸中实现较低的RD(ON),设计主要从晶圆技术和封装技术进行优化。有必要提高MOSFET单元密度。

在PCM中,通过使用新的芯片级CSP封装技术,完全消除了封装导线电阻。

短路能力

大容量锂离子电池在应用中,特别是在极端条件下,如输出负载短路,有非常大的电流通过电池。当集成电路检测到输出过电流时,它将延迟一段时间以进行保护动作。在延迟时间内,MOSFET的工作电流非常大,这要求MOSFET对大电流应力具有鲁棒性。因此,所有锂离子电池都需要进行短路测试。

理论上,芯片尺寸越大,对短路电流的鲁棒性越强。然而,随着形状尺寸变小的趋势,性能将受到限制。因此,应用电路设计需要牢记确保稳健设计以抵抗大短路电流影响所需的要求。

雪崩稳健性

当电池组的输出端短路且开关关闭时,MOSFET雪崩能力很重要。功率MOSFET的选择应包括由应用条件确定的足够雪崩能力。

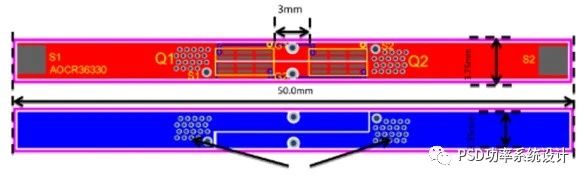

印刷电路板和热设计要点

在正常环境温度下,MOSFET的温度通常不超过65℃。PCM控制板通常与电池组装在一起,PCB尺寸是一个限制因素,通常具有较高的热阻。因此,在系统的热设计中可能需要特殊考虑。电流路径在电路板顶部到底部之间对称,以保持电流平衡。最大化功率路径的铜面积,并在MOSFET附近的铜焊盘上添加一些通孔进行散热,是提高散热能力和降低MOSFET温升的良好设计技巧。

图4:散热器:孔径12密耳,间距25密耳

所有这些因素对大容量锂离子电池组中功率MOSFET的充放电管理提出了严格的技术设计挑战。AOS为电池组应用提供了广泛的高功率密度MOSFET产品。AOS最新的AOCA33102和AOCR36330适用于具有超低RDS(ON)和新型芯片级CSP封装的手机快速充电应用,这有助于降低功率MOSFET的温升并提高其可靠性。

作者Song Liu是Alpha and Omega Semiconductor分立产品高级应用工程师;Neil Zhang是Alpha and Omega Semiconductor分立产品应用工程师

-

SiLM2660CD-DG电池充放电高边NMOS驱动器2025-11-08 881

-

电池充放电管理电路2014-08-25 7418

-

ITS5300 电池充放电测试系统2018-08-07 1195

-

NSAT-9000电池充放电自动测试系统2018-09-26 7460

-

【解密】如何让电池充放电测试变得更加简单2019-12-13 4305

-

NSAT-9000电池模组充放电自动测试系统2020-02-11 2428

-

【罗姆SiC-MOSFET 试用体验连载】电池充放电检测设备2020-04-24 2331

-

如何让电池充放电测试变得更加简单2020-05-23 4753

-

BMS电池管理系统2021-10-25 6687

-

电池充放电资料选型大全2021-09-28 1647

-

无人机电池管理充放电对MOSFET的选择2023-02-16 1134

-

BMS电池管理系统|充放电电流对锂电池性能有何影响?2023-10-24 5193

-

bms怎么区分充放电mos2024-03-27 8617

-

MOSFET在电池管理系统(BMS)中的充放电保护作用2024-05-30 7188

-

电池充放电测试系统:定制需求与适用厂家分析2025-01-15 932

全部0条评论

快来发表一下你的评论吧 !