74ls90工作原理_逻辑功能表_电性参数及应用电路

应用电子电路

描述

7490是二-五-十进制异步计数器,你要做八进制的就先把7490接成十进制的(CP1与Q0接,以CP0做输入,Q3做输出就是十进制的),然后用异步置数跳过一个状态达到八进制计数.

以从000计到111为例.先接成加法计数状态,在输出为1000时(既Q4为高电平时)把Q4输出接到R01和R02脚上(即异步置0),此时当计数到1000时则立刻置0,从新从0开始计数.1000的状态为瞬态.

状态转化图中是0000到0111是有效状态,1000是瞬态,跳转从这个状态跳回到0000状态.

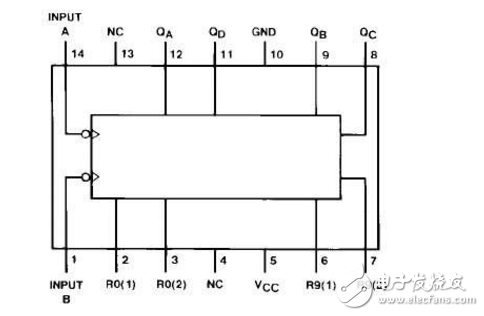

74LS90引脚图及引脚功能

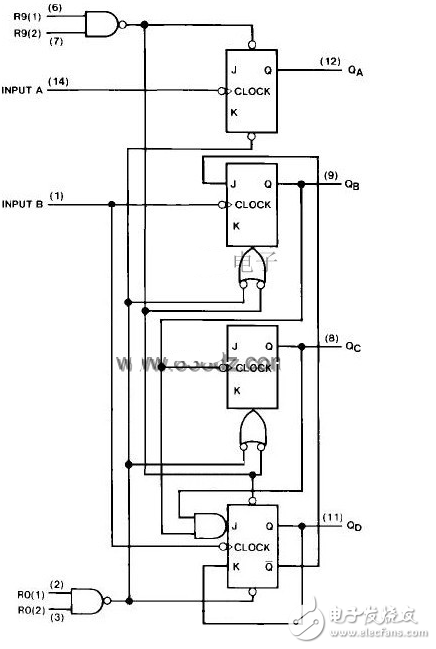

74LS90计数器是一种中规模二一五进制计数器,管脚引线如图3.6-1,功能表如表3.6-1所示。

74LS90引脚图

A. 将输出QA与输入B相接,构成8421BCD码计数器;

B. 将输出QD与输入A相接,构成5421BCD码计数器;

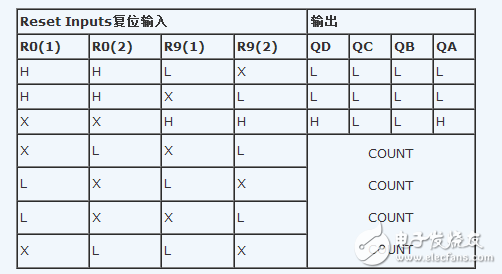

C. 表中H为高电平、L为低电平、×为不定状态。

74LS90逻辑电路图如图3.6-1所示,它由四个主从JK触发器和一些附加门电路组成,整个电路可分两部分,其中FA触发器构成一位二进制计数器;FD、FC、FB构成异步五进制计数器,在74LS90计数器电路中,设有专用置“0”端R1、R2和置位(置“9”)端S1、S2。

原理说明:本电路是由4 个主从触发器和用作除2 计数器及计数周期长度为除5 的3 位2 进制计数器所用的附加选通所组成。有选通的零复位和置9 输入。

为了利用本计数器的最大计数长度(十进制),可将B 输入同QA 输出连接,输入计数脉冲可加到输入A 上,此时输出就如相应的功能表上所要求的那样。

LS90 可以获得对称的十分频计数,办法是将QD 输出接到A 输入端,并把输入计数脉冲加到B 输入端,在QA 输出端处产生对称的十分频方波。

真值表:

H=高电平 L=低电平 ×=不定

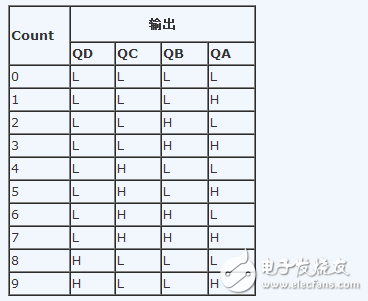

BCD 计数顺序(注1)

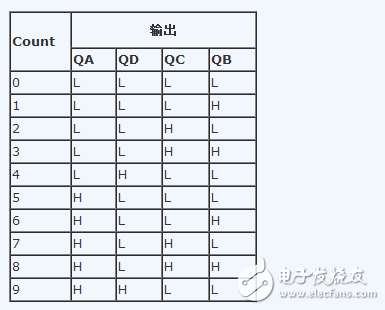

5-2 进制计数顺序(注2)

注1:对于BCD(十进)计数,输出QA 连到输入B 计数

注2:对于5-2 进制计数,输出QD 连到输入A 计数

74LS90具有如下的五种基本工作方式:

(1)五分频:即由FD、FC、和FB组成的异步五进制计数器工作方式。

(2)十分频(8421码):将QA与CK2联接,可构成8421码十分频电路。

(3)六分频:在十分频(8421码)的基础上,将QB端接R1,QC端接R2。其计数顺序为000~101,当第六个脉冲作用后,出现状态QCQBQA=110,利用QBQC=11反馈到R1和R2的方式使电路置“0”。

(4) 九分频:QA→R1、QD→R2,构成原理同六分频。

(5)十分频(5421码):将五进制计数器的输出端QD接二进制计数器的脉冲输入端CK1,即可构成5421码十分频工作方式。

此外,据功能表可知,构成上述五种工作方式时,S1、S2端最少应有一端接地;构成五分频和十分频时,R1、R2端亦必须有一端接地。

74LS90内部逻辑图

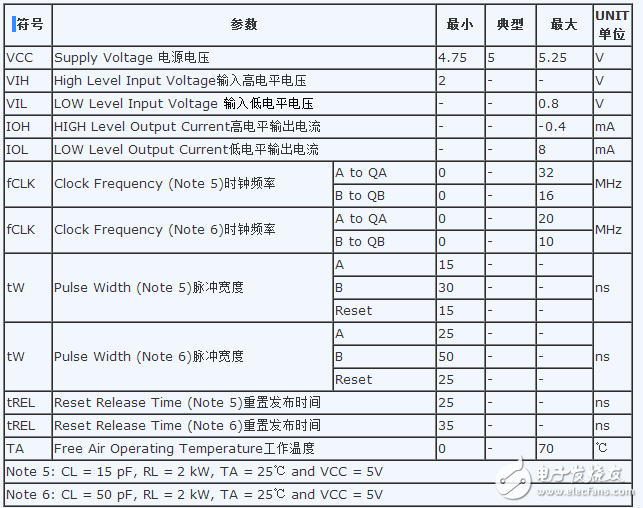

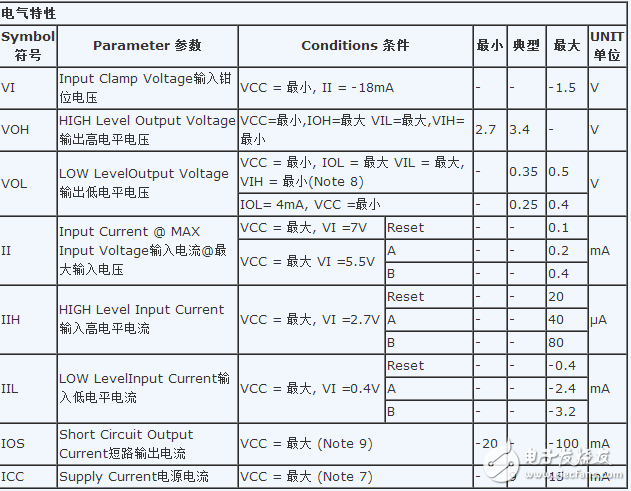

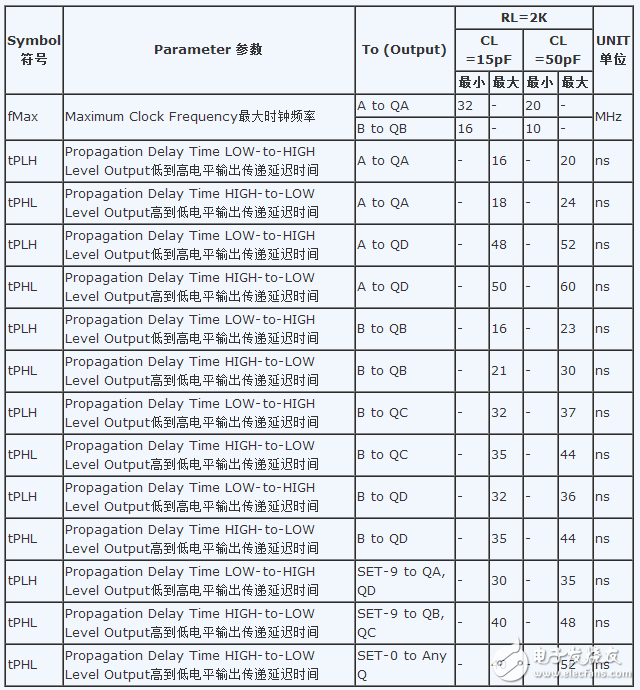

74ls90电性参数表

74ls90应用电路

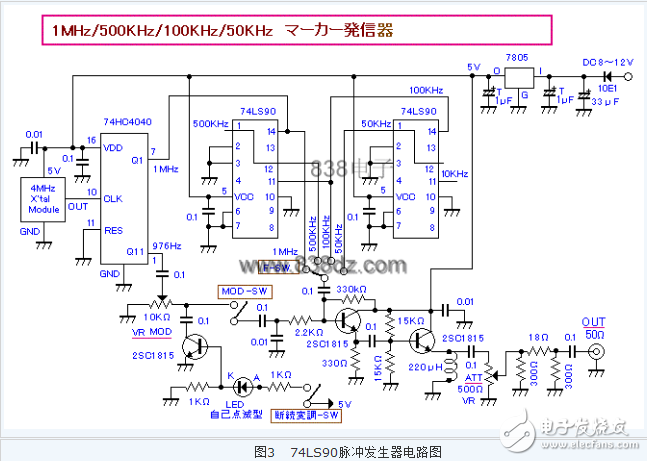

74ls90脉冲发生器电路

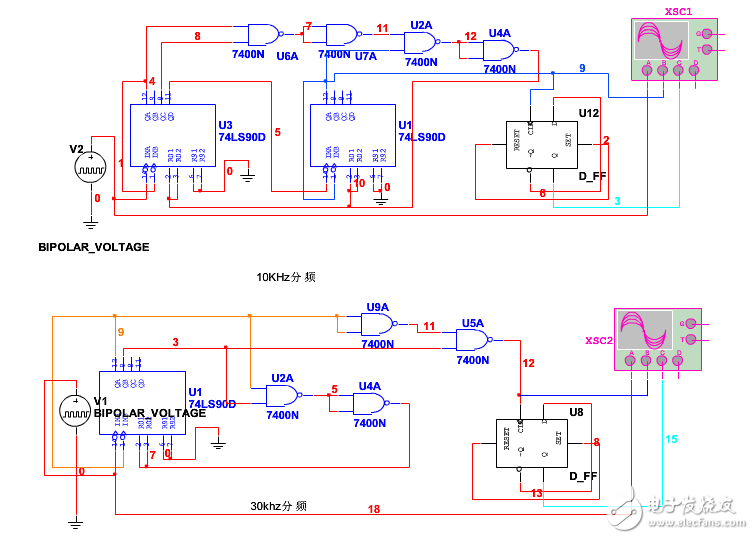

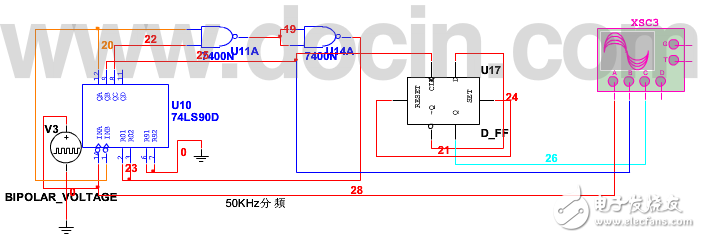

74ls90实现电路的分频

输入信号为300KHZ 的方波信号或i 弦波信号,仿真软件为Multisim10.0.

运用计数器实现分频的关键在于明白计数后产生的上升沿触发信号,触发下一个芯片。R01,R02 为复位端,由计数端控制。R91,R92 始终接地。在送复位信号时要注意信号同时到达两个复位端,复位信号传输中与、非等门电路都会延迟信号到达,所以在这个过程中门电路最好一样。当计数很大时,可以用多个741S90 分别计各个位的数。

-

四位全加器74ls83引脚图及功能表_参数2018-05-31 113657

-

74ls90应用电路图大全(脉冲发生器/分频电路/计数器/数字电子钟逻辑电路)2018-05-29 82087

-

74ls152中文资料_74ls152引脚图_功能表_逻辑图_特性参数2018-05-07 25452

-

74ls273中文资料汇总(74ls273引脚图及功能_工作原理及应用电路)2018-04-26 190388

-

74ls153管脚及功能表_真值表逻辑图及应用电路2018-01-26 613353

-

74ls194引脚图及功能_74ls194功能表_74ls194应用电路2017-12-22 383278

-

74LS系列功能表2017-01-01 5956

-

74LS90英文手册2016-11-05 1466

-

74ls90电子秒表说明书2016-05-20 2582

-

74ls138译码器内部电路逻辑图功能表简单应用2009-07-13 67831

-

74ls90引脚图及引脚功能2008-04-01 129674

-

异步计数器74LS90引管脚图及功能表真值表2007-11-22 23224

全部0条评论

快来发表一下你的评论吧 !