一种基于DSP+FPGA视频图像采集处理系统的设计与实现

FPGA/ASIC技术

描述

1、引言

实时视频图像处理技术的应用十分广泛,在民用领域有机器人视觉、资源探测和医学图像分析等;在军用领域有导弹精确制导、敌方目标侦察与跟踪等。

本设计中采用了DSP+FPGA的硬件结构,DSP采用ADI公司的高性能双核DSP-BF561作为主处理器,负责整个算法的调度和数据流的控制,完成图像数据的采集与显示及核心算法的实现;而FPGA作为DSP的协处理器,依托其高度的并行处理能力,完成图像预处理中大量的累乘加运算。DSP的2个内核与FPGA通过中断进行通信响应,使系统的各处理器并行工作,提高了DSP内核及FPGA的利用效率,保证了系统采集与显示的实时性。

2、系统原理与结构

图像采集与处理系统主要包括4大模块:图像采集模块、存储模块、处理模块和显示模块。图1所示为DSP+FPGA的图像采集与处理系统硬件结构框图。

图1 图像采集与处理系统硬件结构

系统的前端输入模块由CCD摄像头及视频解码器7181B实现,视频解码器将CCD接收到的模拟视频信号转换为标准的YUV4∶2∶2数字视频格式,图像大小为720×576。转换后的图像数据通过ADSP-BF561的专用视频接口PPI0先存储到RAM中,当采集完一帧图像数据时DSP的DMA产生中断,此时FPGA首先对采集来的图像数据完成图像的预处理,然后DSP再将预处理的数据取回完成相应图像处理算法,最后通过PPI1接口由DMA控制器将处理完的视频数据送到视频编码器7171,转换成标准的模拟PAL视频信号到监视器上进行显示。FLASH的作用是存储系统运行的程序,引导系统的启动。

针对系统要求,DSP选用AnalogDevices公司的ADSP-BF561处理器,该DSP是专门针对多媒体和通信应用方面的一款16位定点DSP,它集成了2个Blackfin处理器内核,每个内核可实现600MHz持续工作。

FPGA选用Altera公司的EP2C5,它拥有4608个逻辑单元,13个18×18硬件乘法器,多达142个用户自定义IO口。

2.1、采集模块设计

CCD摄像头采集来标准的PAL制式模拟视频,设计选用ADI的ADV7181B视频解码芯片对模拟信号进行A/D转换。ADV7181B是Analog公司的一款应用广泛的视频解码芯片。该芯片可以自动检测输入的复合视频信号,通过I2C总线配置接口,可选择图像输出格式。由于黑白图像已能够满足系统的检测需要,因此把模拟信号以ITU-R-656格式YUV(4∶2∶2)输出。Y信号是亮度信号,U、V信号是色度信号。这样就可以直接提取该格式的亮度信号,操作比转换为传统的RGB格式要简单得多。

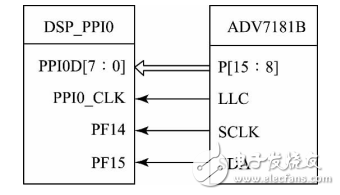

ADV7181B的8根数据线与DSP的PPI0口的8根数据线相连接,通过DSP的2根可编程标志引脚PF来模仿I2C总线,进而对7181B进行相关配置。从而将采集、量化后的视频信号传进DSP缓冲区中。输入模块的硬件连接如图2所示。

图2 采集模块硬件连接

2.2、存储模块设计

由于一帧YUV(4∶2∶2)格式的图像有720×5762=810KByte,而BF561和FPGA的内部存储空间分别只有328KByte及14KByte,因此,将SDRAM和RAM存储器分别作为DSP及FPGA的外扩存储器。这样输入的视频数据存到外部扩展存储器中,可以使系统具有大容量、高吞吐率和高存取速度的特点,实现大数据量和实时性的要求。

系统采用2片32MB的HY57V561620CSDRAM,组成32位的数据输入与输出,通过4根数据屏蔽线(SDQM[3∶0]),可以进行8位、16位、32位的数据读写。选用1片4MByte,32位宽的RAM挂接到FPGA上,其地址线,数据线都与SDRAM的分开。其选通信号CS#与读写信号WE#、OE#也由FPGA控制。

2.3、处理模块设计

DSP与FPGA作为图像处理模块的核心,协同完成图像的处理任务,DSP作为系统的主控制器,FPGA上电后由DSP来完成配置。DSP和FPGA的功能划分按照算法流程进行,DSP负责整个算法的调度和数据流的控制,而FPGA作为DSP的协处理器。DSP通过AMS3#来片选FPGA,AWE#、AOE#作为读写使能,同时DSP的24位地址线(A[25∶2])和32位数据线(D[31∶0])都挂接到FPGA上,这样DSP与FPGA就可以进行数据的交换。它们各自在系统中完成的任务如下:

1)DSP控制数据流的流向,通过自己特有的PPI图像接口完成图像数据的采集与发送,并完成图像中目标的识别算法;

2)FPGA是DSP的协处理器,FPGA作为DSP的逻辑扩展,帮助DSP来复位视频编解码器等这些外部设备;FPGA对采集到RAM中的原始图像数据完成一些数据密集,但算法简单、重复性高的图像预处理功能。再将处理后的数据送回到DSP中完成最后的目标识别算法。

2.4、显示模块设计

在数字视频数据处理完成后,选用ADI公司的视频编码器7171将数字信号转换成PAL制式电视信号,用专用的监视器将图像结果显示出来。

BF561的PPI1口的8根数据线与7171的数据线相连,输出时7171由DSP通过I2C总线配置为输出PAL制式。

3、系统软件设计

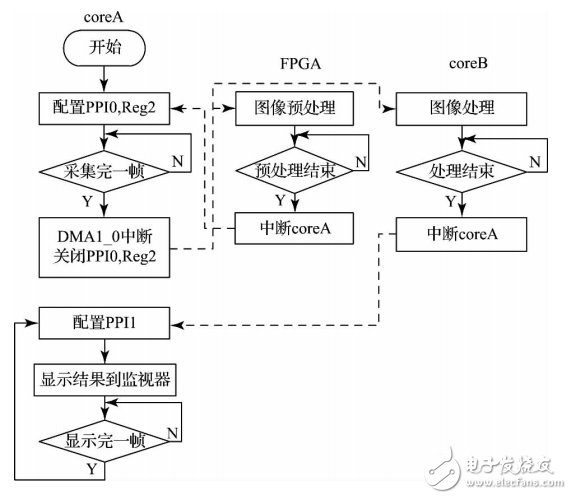

系统的软件设计主要包括系统的初始化、图像的采集与显示2大部分。针对BF561的双核结构,这里DSP的coreA完成系统的初始化以及图像采集与显示,coreB完成目标识别算法,这样可以减少双核的公共变量及数据共享,简化双核交互的时序控制设计,使系统更加稳定的工作,而FPGA进行图像的预处理。

3.1、系统初始化

首先,要对BF561的PLL锁相环时钟、EBIU外部总线接口及中断向量表进行初始化设置。外部晶振产生的27MHz时钟通过PLL的20倍频使内核工作在540MHz的时钟频率下;EBIU配置为外部总线接口打开。

EBIU配置好后,对DSP的外设进行初始化设置,依次对SDRAM、FPGA等外设进行初始化。将地址0x2E800000、0x2EF00000映射到FPGA上产生一个8位控制寄存器Reg1和32位控制寄存器Reg2,向寄存器Reg1写控制字,控制7181、7171硬复位,并配置PPI口的驱动时钟,向寄存器Reg2写控制字,控制RAM地址总线及数据总线与DSP的对接。

3.2、图像的采集与显示

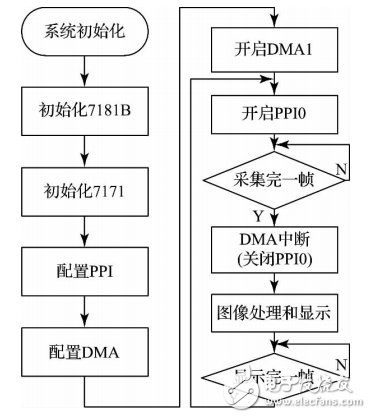

系统图像采集与显示的软件流程图如图3所示。

图3 图像采集与显示流程

系统初始化结束后,对负责图像编解码的7181B和7171通过I2C总线进行初始化。将7181配置输出为ITU-R-656模式,7171配置输出为PAL制式。通过编写控制字到PPI口的控制寄存器PPIx_CONTROL,相应地PPI0口配置为接收ITU-R-656模式,并采用有效场模式,PPI0口仅输出每场的有效数据到DSP中,而把消隐行的数据过滤掉,减小图像数据的存储空间,并节约内核开销;PPI1口则配置为GP模式,这时需要BF561产生水平同步信号和垂直同步信号配合PPI1口完成数据输出。

BF561的PPI口必须和DMA引擎一起使用。每个PPI_DMA通道可配置为发送或接收操作,最大的吞吐量是PPIx_CLK16bit/transfer,为了提高效率,这里采用8bit数据、PACK_EN=1(使能打包模式)、DMA32=1。即PPI和DMA都以其最大带宽传输数据。系统中图像采集与显示都通过DMA完成,无需内核参与,最大限度地节约了内核开销,使内核集中完成图像的处理算法任务。

3.3、图像数据流的存储与传输及其时序设计

为了提高系统运行效率,发挥DSP的流水线执行及FPGA并行处理的优势,把RAM分为3块区域,Frame0和Frame2作为乒乓缓存,轮流作为图像数据缓存的目的地和FPGA处理数据的源头;Frame1存放FPGA预处理后的结果。同样SDRAM开辟3块区域,Buffer0、2存放从FPGA搬移的预处理结果,Buffer1存放最后结果。

在FPGA完成预处理后触发DSP中断,开启PPI0口,并且DSP总线与RAM再次对接,coreA将预处理结果搬移到SDRAM中,同时DMA1_0控制PPI0采集新一帧的图像数据到RAM。此时coreB已完成目标识别并将最终结果存入SDRAM,并中断coreA,coreA打开PPI1,由DMA1_1控制PPI1完成最终结果的显示。图像的采集与显示都由DMA控制,不会干预coreA对预处理结果的搬移。而搬移速度要快于采集速度,所以在PPI0采集完新的一帧后,上一帧的预处理结果已经搬完。DMA1_0产生中断,PPI0、DSP总线与RAM对接再次关闭,如此循环往复。其实现过程流程图如图4所示。

图4 图像数据流处理流程

4、实验结果及分析

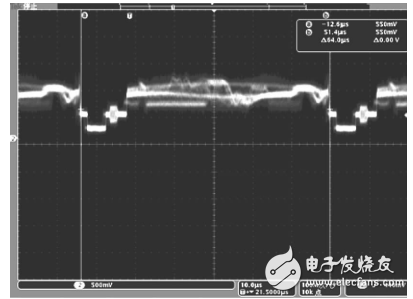

对25frames/s、16bit、720×576像素的视频图像进行显示速度测试,利用示波器检测监视器上扫描一行图像的波形如图5所示。

图5 显示一行的波形

分析图中波形,显示一行图像的时间为64μs,一帧完整图像共有625行,所以显示一帧图像所用的时间为40ms。达到了CCD摄像头25frames/s的刷新速度,实现了系统的实时采集处理。

5、结论

为实现图像的实时采集与处理,设计了一种基于ADSP-BF561+FPGA的图像采集与处理系统。结合BF561的PPI视频接口与其DMA的特点,设计了图像采集与显示算法,充分利用了DSP的流水线执行与FPGA及双核DSP并行处理的优势。通过实验论证,图像显示的刷新时间能够达到25frame/s,达到了实时性要求。并且该图像采集与处理系统还具有结构紧凑、功耗低、集成度高、执行效率高等优点。为整个数字图像处理系统的设计实现奠定了重要的实践基础。

-

如何设计一种基于CPLD和DSP器件的多分辨率图像采集处理系统?2021-06-04 1031

-

怎么设计一种基于HD-SDI技术的高清图像处理系统?2021-06-01 1791

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 3351

-

一种基于FPGA+DSP的视频处理系统设计2019-07-01 2301

-

基于FPGA+DSP架构的视频处理系统设计2019-06-28 2215

-

基于FPGA与DSP的视频处理系统设计2019-06-19 2133

-

基于DSP+FPGA的实时图像去雾增强系统设计2017-12-25 4370

-

基于FPGA和DSP的高速图像处理系统2017-10-19 1087

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 1127

-

一种CCD图像相关处理系统的FPGA_DSP实现2016-09-14 688

-

基于DSP的图像处理系统的应用研究2012-12-19 9531

-

DSP+FPGA折反射全景视频处理系统中双核高速数据通信2010-03-06 548

-

基于DSP+FPGA的实时视频采集系统设计2009-12-16 766

全部0条评论

快来发表一下你的评论吧 !