基于FPGA的交流电磁场检测仪的激励源设计

FPGA/ASIC技术

描述

引言

交流电磁场检测(AlternatingCurrentFieldMeasure-ment.ACFM)是一种基于电磁感应原理的主动式电磁无损检测技术,对导电工件表面及近表面裂纹的检测具有独特的优势。交流电磁场检测需要在被测工件表面感应出交变电流,当不存在缺陷时,感应电流均匀分布;存在缺陷时,缺陷对感应电流产生扰动,通过提取感应电流产生磁场的变化来确定缺陷的长度及深度等信息。

现场可编程门阵列(FieldProgrammableGateArray,FPGA)是近年来新型的高集成度数字器件,受到世界范围内电子工程设计人员的广泛关注和普遍欢迎,可以满足大多数专用检测系统的设计。本文以FPGA为开发平台设计频率可调的激励源模块,激励源由直接数字频率实现,合成频率适用于不同的被测材料,既可以满足交流电磁场检测系统的需求,又可以降低该系统的功耗和成本。并且FPGA的引脚丰富、存储区大,特别适合现场的实时检测系统,方便检测仪器的野外和高空操作。

1、直接数字频率合成原理

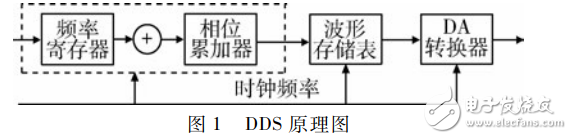

DDS或DDFS(DirectDigitalFrequencySysthesis)即直接数字频率合成,原理是将信号的完整周期预先做归一化处理,采样足够的点数存储,需要输出时通过时钟频率查找存储表地址对应的幅值输出给高速DA转换器,由低通滤波器输出模拟信号。典型的DDS原理如图1所示。波形存储表可以设置为正弦波)方波)三角波等波形。

假设正弦波信号的一个周期以2N次采样存储,fclk时钟频率fn为合成频率,T0为合成信号周期。并且假设累加器位数与地址位数相同,则控制合成频率有全采样和频率控制字采样两种方法。

1.1、全采样

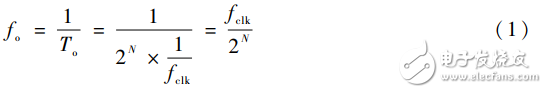

时钟频率查找波形存储表的每一个地址,输出地址对应的幅值。则合成激励源的一个完整周期需要2n次查表,合成频率与时钟频率的关系如式(1):

式中:fn为合成频率,Tn为合成信号周期,fclk为时钟频率,2n为采样次数。由式(1)可知所有采样点都经过查找输出幅值时,通过改变时钟频率fclk即可合成不同频率的信号。

1.2、频率控制字采样

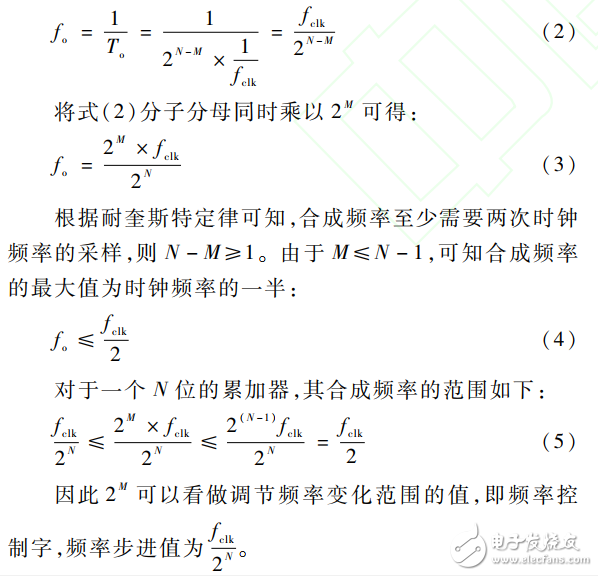

在采样时钟频率一定时,已知波形存储表的长度不变,通过控制每次累加频率控制字的大小,改变查找表的次数,合成不同频率的信号。

但是设计的累加器位数与地址位数一致后,当频率控制字的值大于l时,每次周期采样都会丢失一部分波形存储表地址。如表1所示,当以1为频率控制字累加步进时,每次相位累加后的结果与地址对应;当以2为频率控制字累加步进时,一个周期的合成只能查找一半的频率地址,另外一半的地址信息丢失。并且随着频率控制字的值增加,合成信号的每个周期采样点数越来越少。

表1 合成频率采样表

为了避免将查表的地址信息丢失,在电路设计中通常增加累加器的位数,累加器在功能上可以划分为地址寄存器和相位寄存器,如表2所示,在累加器的低位中增加相位寄存器。当频率控制字的值以小于等于相位寄存器的最大值进行累加时,都会首先向地址寄存器的最低位进一,进位后的相位寄存器清零,地址寄存器的值发生变化,这样就会使地址寄存器的输出与存储表的地址一一对应,存储表的地址信息全被查找。

表2 相位累加器功能表

2、信号源的VerilogHDL编程

VerilogHDL是硬件描述语言的一种,设计者需要掌握具体物理电路模型,编写设计文件,然后使用EDA工具进行仿真验证,使用自动综合工具转换到门级电路网表,最后经过布局布线生成电路。由上述内容可知,DDS系统需要设计相位累加器、频率寄存器、波形存储表及查表。为了方便控制频率控制字的变化,本文设计了独立按键来调节频率控制字。

2.1、相位累加器的设计

累加器功能上是由高8位地址寄存器和低8位相位寄存器组成,频率控制字通过频率寄存器实现,所以在FPGA中需要设计一个16位累加器和8位wire型频率寄存器。累加器Verilog代码如下:

2.2、波形存储表的生成

由于DA转换芯片为8位,故波形存储表的幅值位宽为8位,地址深度为256。波形存储表采用QUARTUSII的波形数据生成器MifMaker来生成。累加器的高8位输出与波形存储一一对应。正弦存储表如下所示:

波形存储表生成以后需要导入FPGA的存储区,在FPGA中配置对应的波形存储块,与波形生成器文件的深度和位宽保持一致。建立方法如下:

(1)在Tools工具栏下选择MegaWizard创建新宏单元;

(2)在MemoryCompiler目录下选择ROM,对其进行设置器件型号、位宽、深度相关参数;

(3)添加生成的波形存储表。

2.3、FPGA查表的设计

在上述第二步的基础上,将波形存储表导入FPGA的ROM存储块后,还需要例化ROM存储块,读取波形存储表的DA转换数据。其例化程序如下:

dacwavedacwave_inst(.address(addr),.clock(clk),.q

(dac_data));

2.4、按键电路的设计

通过独立按键控制DDS的输出频率,其中sb3将频率控制字设为最小值1,sb4将频率控制字设为FF。代码如下:

always@(posedgeclkornegedgerst_n)

if(!rst_n)

frewordn《=

8‘hl;

else

begin

if(fre_word_ctrl

[0]fre_word_n《=fre_

word_n+l’bl;

if(fre_word_ctrl

[1])fre_word_n《=fre_

word_n-l‘bl;

if(fre_word_ctrl

[2])fre_word_n《=8’bl;

if‘(fre_word_ctrl[3])fre_word_n《=8’bllll_llll;

end

assignfre_word=fre_word_n;

2.5、DDS模块的RTL视图

RTL级(Register-Transfer-Level)是实际电路的行为级描述,描述数据在寄存器之间的流动模型。通过RTL视图可以直观地了解设计的实际电路。基于FPGA的激励源RTL视图如图2所示。

图2 激励源的RTL视图

3、外围电路的设计

基于FPGA的激励源模块主要有时钟电路、DA转换及4输入按键电路。输入端口包括时钟输入端口、复位端口、独立按键端口、DAC时钟输出端口及DAC数据输出端口。本次设计采用40MHz晶振,AD9708进行DA转换。

AD9708是电流输出型DA转换器,8位低功耗数模转换器,最高支持125MSPS的更新速率。内置一个1.2V片内基准电压源和基准电压控制放大器,只需要单个电阻即可设置满量程输出电流。电流输出可以直接连至一个输出电阻,以提供两路互补的单端电压输出。具体的电路设计如图3所示,注意将模拟地和数字地通过0欧的电阻进行连接。

图3 DA转换电路原理图

根据AD9708的数据手册可得DA转换器的满量程输出电流可以通过REFIO与REFLO设置,REFLO连接至地时,使用内部参考电压1.2V,Ioutfs如式(6)所示,电流输出如式(7)所示,电压输出如式(8)所示。

上式中Ioutfs为满量程输出电流,Vrefio为内部参考电压,RSET为设置的电阻值,IoutA为输出电流,VoutA为输出电压。电流输出型DA转换器通常需要外接电流一电压转换电路来输出电压,一种是直接将电流输出端接负载,另外一种是接运算放大器来输出电压。DA转换器的输出阻抗比较大,所以通常采用运算放大器来输出电压。由于交流电磁场的激励线圈需要的电压和电流较大,因此还需要接功率放大器来提高驱动能力。

4、激励源模块功能验证

在FPGA中设计好激励源模块后,将高速DA转换芯片的输出接到示波器上,FPGA上电后,通过独立按键可以调节合成信号源的频率,频率值可以在610Hz~156kHz之间变化,频率控制字每增加1,激励源频率增加610Hz。图4为频率控制字为1时合成正弦波信号,频率为610Hz。

5、结论

本文实现了交流电磁场检测仪的激励源设计,对于不同的被测工件可以通过独立按键控制激励源的频率。激励源的波形可以通过存储表来改变,形成多样化的信号源。激励源控制电路集成到FPGA芯片中,提高了设计灵活性,降低了开发成本及功耗。激励源的模块化设计可以方便地移植到其他检测系统,具有广泛的应用前景。

-

交流电与电磁波的关系2024-11-24 2620

-

交流电动机的工作原理 交流电动机的调速方法2024-02-02 4077

-

交流电机的调速方法和接线方法2023-03-24 5368

-

交流电机和异步电机的区别2023-03-23 4402

-

如何减弱电路产生的电磁场对其他部件的干扰2021-03-01 3496

-

AR手持电磁场测量系统2018-09-25 3349

-

如何检测交流电磁泵是否在空转2018-09-17 2636

-

基于Cortex_M3的三相交流电压相序检测仪的研制_廖鸿2017-03-19 1311

-

新型电磁场辐射检测仪,型交流电压测试笔,2012-09-13 3447

-

avr单片机的电磁场检测仪的研究与设计的程序求购2012-05-28 2569

-

用钳形电流表检测交流电机或变压器的漏磁场2009-09-11 1467

-

电磁场与电磁波pdf2008-10-30 2244

-

工程电磁场导论2008-09-16 1834

全部0条评论

快来发表一下你的评论吧 !