使用Xilinx口袋实验平台,动手FPGA设计!

电子说

描述

当前,使用FPGA来进行数字逻辑课程实验以及相关动手实践、创新已经被越来越多的老师和学生所接受。学习数字逻辑基础课的同时,掌握FPGA设计的基本流程和技巧也会对后续的学习以及工作有莫大的好处。

EGO1,这一最新的Xilinx口袋实验平台正是为此而生!各位对EGO1还不是很熟悉的小伙伴们,请点击这里详细阅读EGO1口袋实验平台的详细介绍。

EGO1配套教材-《基于Xilinx Vivado的数字逻辑实验教程》

针对初学上手的小伙伴们,EGO1口袋实验平台推荐有多部参考教材。今天要介绍的就是一本来自于哈尔滨工业大学电工电子实验教学中心电子学实验室主任廉玉欣老师精心编写的-《基于Xilinx Vivado的数字逻辑实验教程》。

本书由依元素科技提供技术支持,以Xilinx公司最新的Vivado FPGA集成开发环境为基础,将数字逻辑设计与硬件描述语言Verilog HDL相结合,循序渐进地介绍了基于Xilinx Vivado的数字逻辑实验的基本过程和方法。书中包含了大量的设计实例,内容翔实、系统、全面。

目前该书已在各大平台以及实体书店有售,使用EGO1学习数字逻辑以及FPGA设计的小伙伴们可不要错过噢!

EGO1动手练习

今天我们EGO1动手练习部分要做的是一个计数器实验。这个实验在参考教材《基于Xilinx Vivado的数字逻辑实验教程》的第5章第3节,是时序逻辑实验部分的10K进制计数器实验。

在Verilog中,实现一个任意位的计数器非常容易。一个计数器的行为就是在每个时钟的上升沿使输出加1。

我们通过编写Verilog代码来完成这个计数器逻辑电路。

其中,mod10kcnt_top.v为计数器实验的顶层模块。该模块的作用是将各个模块连接起来。

clkdiv.v为时钟分频模块,将输入为100MHz的时钟分频为190Hz和48Hz。

mod10kcnt.v为10K进制计数器模块。该模块的输入时钟为48Hz。

binbcd14.v为14位二进制转BCD码模块,该模块的作用是将10K进制计数器模块的输出转换为BCD码。

x7segbc.v为数码管模块。该模块的输入时钟为190Hz,该模块的作用是将转换后的BCD码通过数码管显示出来。

mod10kcnt_top_tb.v为Testbench文件,该文件的作用是给这个计数器逻辑电路施加测试激励信号,并进行仿真。

mod10kcnt_top_top.xdc为管脚约束文件。

关于实验原理部分的详细讲解,有兴趣的小伙伴们可以查阅参考书的对应章节。

实验源文件准备妥当之后,我们就可以开始动手实践啦。

首先当然是打开Vivado工具咯,这里我们使用最新的2017版本的Vivado开发环境。什么?你还没有安装Vivado么?表担心啦,我们提供有详细的Vivado安装流程。

Vivado开发环境成功打开后,它的主界面如下。

接下来就让我们开始使用Vivado完成这个实验吧。如果有对Vivado操作不熟悉的小伙伴们也不用担心啦,我们提供有STEP-BY-STEP的指导噢。

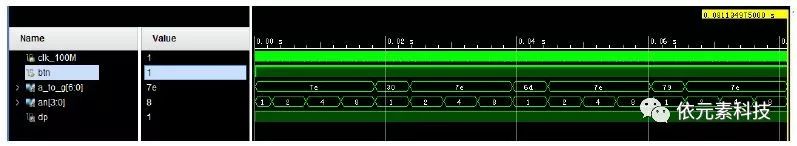

首先,我们进行实验仿真。下面是仿真的结果。

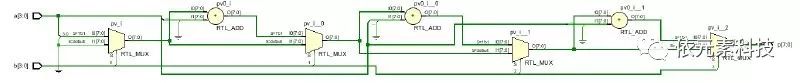

同时,我们可以在Vivado中查看我们RTL所对应的原理图。

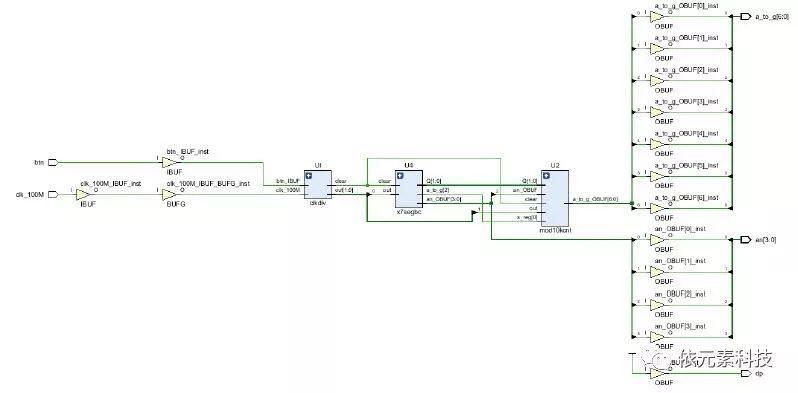

在完成Vivado FPGA综合流程后,我们还可以看到这段电路综合后的原理图。

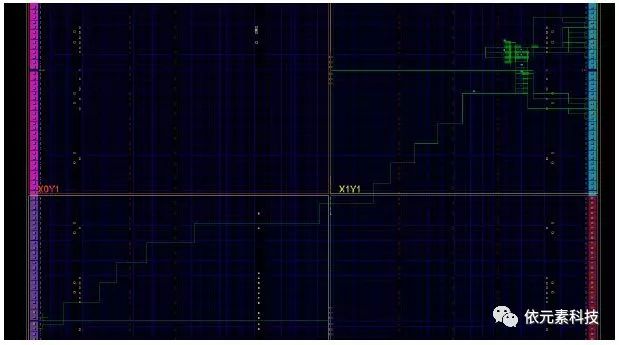

最后,我们完成设计的整体实现,可以看到这段电路在实际的FPGA芯片中的线路图。

接下来,就可以在硬件平台上下载验证啦。当然,我们也有使用EGO1口袋实验平台来进行硬件下载的详细步骤介绍哟。

硬件配置完成后,我们就可以在EGO1平台上来验证我们的设计啦,这个设计中我们将EGO1开发板的拨码开关SW0作为clr的输入,同时用数码管显示计数结果。将SW0拉高后,计数结果就直接显示在数码管上面了。好啦,各位小伙伴们大家看看我们的电路计算正确么?

FPGA我们是认真的!

-

Launchpad口袋实验平台 (指导书).2015-08-13 2589

-

Launchpad口袋实验平台MSP430G2 电子书PDF 分享2015-12-29 24112

-

基于Xilinx Zynq-7020和AD9361的口袋式软件无线电解决方案2016-07-05 25589

-

《数字电路》课程口袋型FPGA实验板介绍2021-01-28 3191

-

369口袋仪器 口袋实验室 多功能口袋仪器 便携式口袋仪器2022-12-21 9224

-

使用EMIF将Xilinx FPGA与TI DSP平台接口2009-11-01 1222

-

简谈Altera和Xilinx的FPGA区别2018-05-29 47374

-

NoLoad面向Xilinx FPGA的存储和计算加速平台2018-11-26 3843

-

口袋实验平台AY-G2PL KIT用户手册免费下载2019-04-02 1778

-

MSP430口袋实验板AY-G2PL KIT口袋实验平台用户手册免费下载2019-05-07 1423

-

从零开启大学生电子设计之路基于Launchpad口袋实验平台2019-05-09 2130

-

MSP430G2口袋实验平台例程资料免费下载2019-07-17 1554

-

使用XIlinx的FPGA芯片开发的流水灯实验工程文件免费下载2019-07-31 1348

-

Xilinx EGO1口袋实验开发板全套资料合集2020-11-17 3711

-

ED6H系列FPGA口袋实验室2024-12-05 1728

全部0条评论

快来发表一下你的评论吧 !