如何编写代码与生成下载文件的简单介绍

FPGA/ASIC技术

描述

当我们在对产品的FPGA代码做远程升级时,通常都是把加密后的下载文件发给用户,让用户在本地进行下载升级。但有时候由于我们没检查好,致使更新程序有问题,这样给到用户手上下载后,就会使得东西无法工作或者工作异常。如果不是紧急情况,做些沟通再把正确的文件重新给用户即可;但如果设备是属于持续工作型,那便一个钟也耽误不起,此时便会造成很多不必要的麻烦了。

所以在对FPGA代码进行远程升级时,建议使用多重配置功能。

1.ICAPE核

使用多重配置功能时,必须调用FPGA内部的ICAPE核,该核可以对上一节讲的IPROG的指令进行配置。

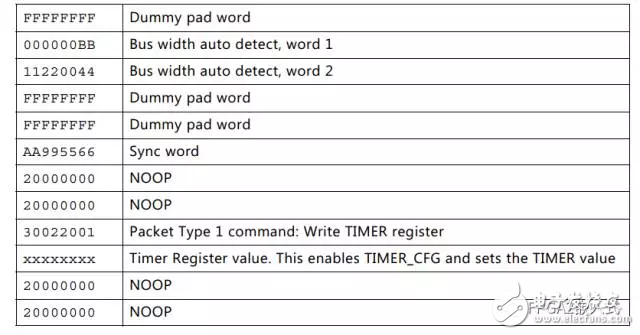

IPROG配置指令

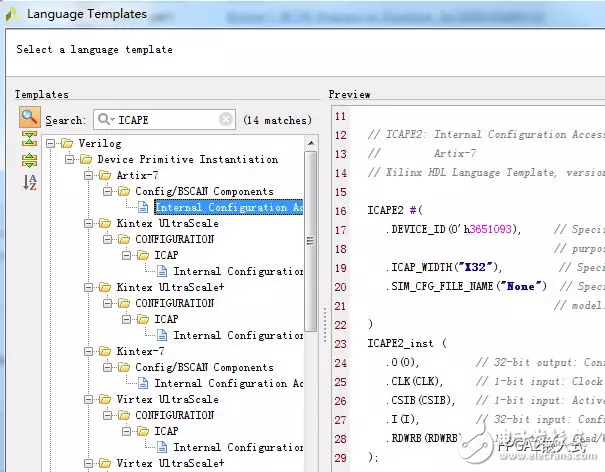

在Vivado中的“Language Templates”中进行搜索,输入”ICAPE”便可以看到你所使用的器件对应的ICAPE核的源语了。ISE的也是如此。

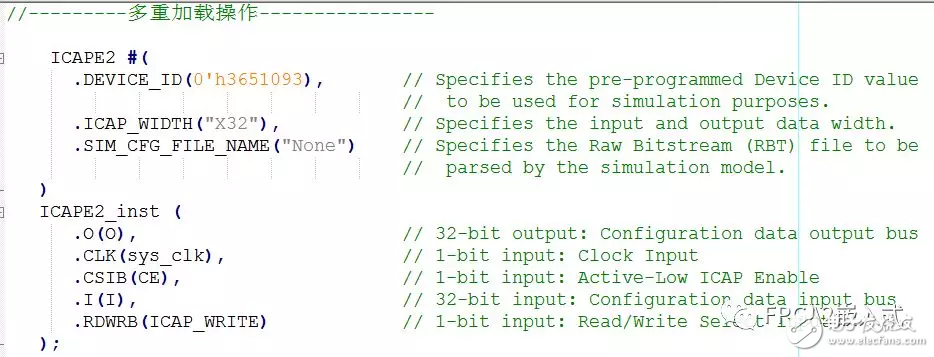

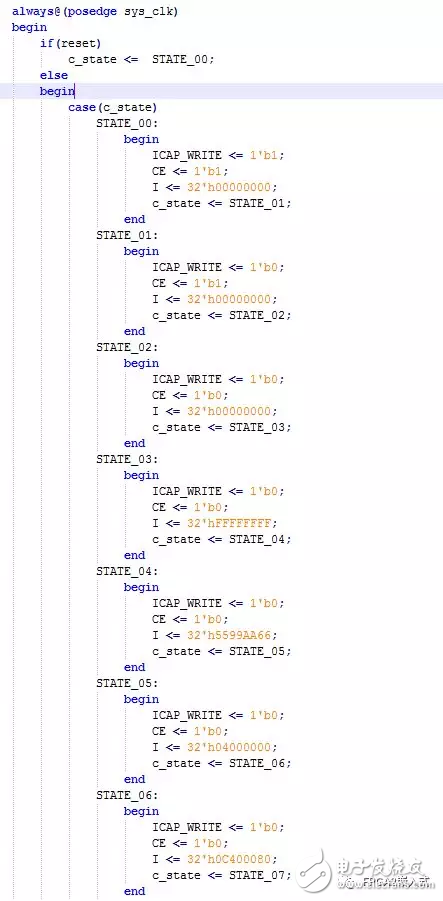

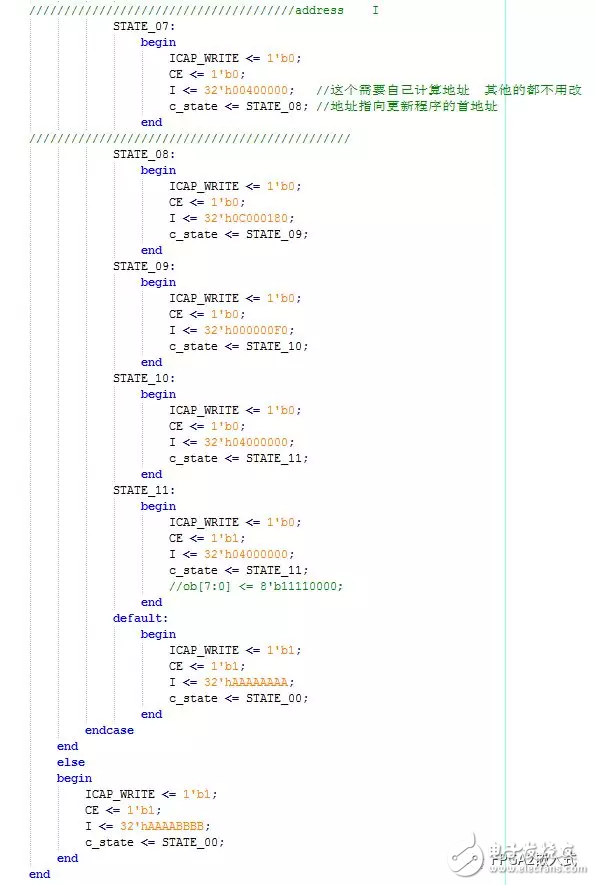

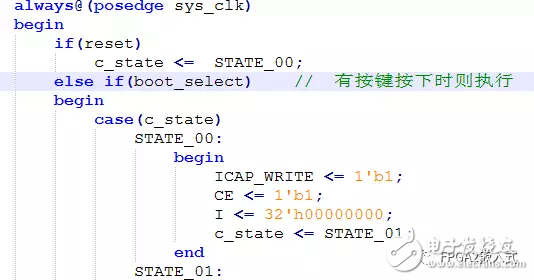

2.多重配置的代码

多重配置的代码是放在旧程序上,更新程序不需要此段代码。旧程序则从Flash的0地址开始存储;更新程序是存储在旧程序的后面。当系统上电后,FPGA会访问Flash的0地址起,查看旧程序中的ICAPE核,以此判断是否去加载新程序。

在更新程序中,则不需要以上的代码,原因上一小节已经说过了。

3.多重配置文件的打包

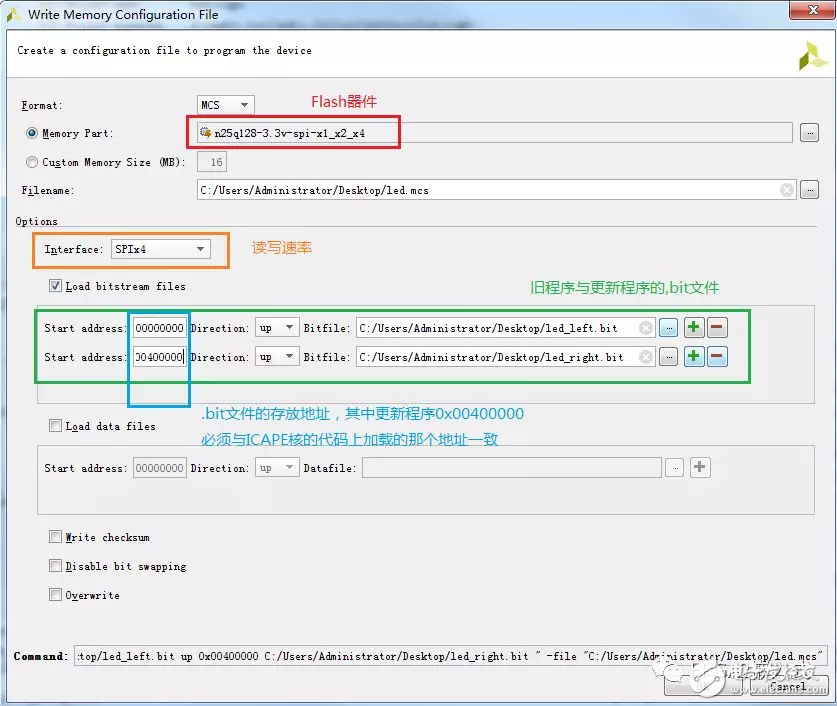

在Vivado中,生成.xdc文件时,还需要把Flash加载的信息写入。如下图所示,设置为SPI Flash存储,采用4速率进行读写。

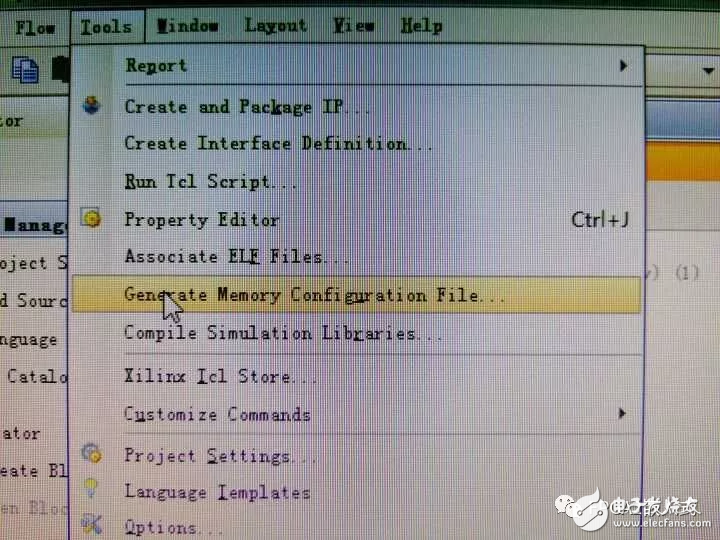

之后便是将两个.bit文件合并成一个.mcs文件了。在Vivado的菜单栏中选择“Tools”——“Generate Memory Configuration File”,进行.mcs文件的配置。

如下图所示,选择Flash器件,选择读写速率,选择下载文件,点击OK便可以生成.mcs文件了。

最后将生成的.mcs文件发给用户即可,这样当用户在加载更新程序过程中出现问题时,FPGA会自动跳到之前的旧文件重新进行程序加载,从而保证设备可以正常运行。

有兴趣的读者可以尝试一下,在ICAPE核的控制代码中加入一些控制信号,比如使用一个外部按键,当检测到按键按下时,则执行ICAPE核的代码,此时FPGA便会去重新加载新的工程。如果没有按键按下,则继续运行当前的工程。

3.结语

本小节只是简单的介绍了如何编写代码与生成下载文件,在一般的运用中,按照本小节的做法便可以做到程序的多重加载了。

-

手机登陆不能下载文件2018-08-30 1849

-

如何使用BitTorrent下载文件2009-08-03 9299

-

C#教程之断点续传下载文件2016-04-20 455

-

电路下载文件总览更新2017-11-10 798

-

Maven工具生成Mybatis的代码及映射的文件2017-11-29 2444

-

如何解决ASP NET下载文件名乱码问题详细实例说明2019-10-11 1099

-

使用Java语言编写战机的设计报告和源代码以及可执行文件2019-11-05 958

-

WQX开发板下载如何下载文件到单片机详细的过程说明2019-12-03 1117

-

使用KEIL下载文件到单片机外置存储器的方法2021-11-17 1047

-

单片机中分散加载文件介绍2021-12-03 653

-

使用OkHttp上传和下载文件时显示进度库使用2022-03-24 755

-

什么是分散加载文件?何时进行分散加载2022-09-14 3498

-

什么是分散加载文件?2023-01-30 4511

-

大彩串口屏4G应用-HTTP下载文件2021-07-26 2972

-

远程下载是什么意思?怎么实现远程下载文件2024-05-15 2029

全部0条评论

快来发表一下你的评论吧 !