AXI 总线和引脚的介绍

接口/总线/驱动

描述

1、AXI 总线通道,总线和引脚的介绍

AXI接口具有五个独立的通道:

(1)写地址通道(AW):write address channel

(2)写数据通道( W): write data channel

(3)写响应通道( B) : write response channel

(4)读地址通道(AR):read address channel

(5)读数据通道( R): read data channel

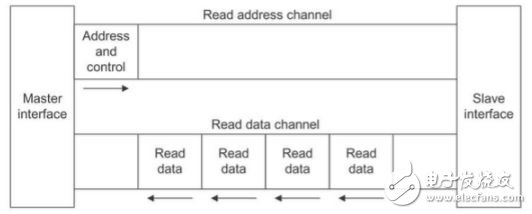

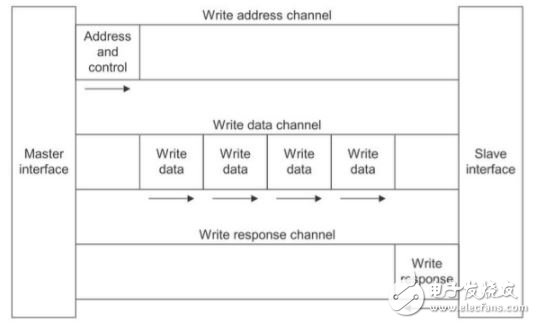

五个通道图为:

读地址通道和读数据通道

写地址通道,写数据通道和写响应通道

读地址通道的信号:S_AXI_ARADDR,S_AXI_ARPROT,S_AXI_ARVALID,S_AXI_ARREADY;

读数据通道的信号:S_AXI_RDATA,S_AXI_RRESP,S_AXI_RVALID,S_AXI_RREADY;

写地址通道的信号:S_AXI_AWADDR,S_AXI_AWPROT,S_AXI_AWVALID,S_AXI_AWREADY;

写数据通道的信号:S_AXI_WDATA,S_AXI_WSTRB,S_AXI_WVALID,S_AXI_WREADY;

写响应通道的信号:S_AXI_BRESP,S_AXI_BVALID,S_AXI_BREADY。

AXI接口的总线宽度:

C_S_AXI_ADDR_WIDTH : S_AXI数据总线的宽度

C_S_AXI_ADDR_WIDTH : S_AXI 地址总线的宽度

AXI接口的信号详细说明:

S_AXI_ACLK : in std_logic;

总线的输入时钟信号

S_AXI_ARESETN : in std_logic;

全局性的复位信号,这个信号低电平有效

S_AXI_AWADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

写地址通道(由主设备设置发送到从设备)

S_AXI_AWPROT : in std_logic_vector(2 downto 0);

写通道保护类型,此信号表示事务的特权和安全级别,以及事务是数据访问还是指令访问。

S_AXI_AWVALID : in std_logic;

写地址有效,此信号表示主设备正在发送有效的写入地址和控制信息。

S_AXI_AWREADY : out std_logic;

写地址就绪。这个信号表明,从设备将接受地址和相关的控制信号。

S_AXI_WDATA : in std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

写数据(由主设备设置传送到从设备)

S_AXI_WSTRB : in std_logic_vector((C_S_AXI_DATA_WIDTH/8)-1 downto 0);

写数据选通,这个信号表明写数据总线上哪个字节通道存着有效的数据。写数据总线上每八个位对应一个写选通位

S_AXI_WVALID : in std_logic;

写有效,这个信号表明有效的写数据和写选通可用

S_AXI_WREADY : out std_logic;

写准备,这个信号表明从设备可以获取写数据

S_AXI_BRESP : out std_logic_vector(1 downto 0);

写响应,这个信号表明写事务的完成状态

S_AXI_BVALID : out std_logic;

写响应有效。此信号表示信道正在发出有效的写响应。

S_AXI_BREADY : in std_logic;

响应准备,这个信号表明主设备可以接受写响应

S_AXI_ARADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

读地址(由主设备设置传送到从设备)

S_AXI_ARPROT : in std_logic_vector(2 downto 0);

读通道保护类型,此信号表示事务的特权和安全级别,以及事务是数据访问还是指令访问。

S_AXI_ARVALID : in std_logic;

读地址有效,此信号表明读地址通道正在发送有效的读地址和控制信息

S_AXI_ARREADY : out std_logic;

读地址准备,这个信号表明从设备已经准备接受地址和相关的控制信号

S_AXI_RDATA : out std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

读数据(由从设备设置)

S_AXI_RRESP : out std_logic_vector(1 downto 0);

读响应,此信号表明读数据传输的完成状态

S_AXI_RVALID : out std_logic;

读有效,此信号表明读数据通道正在传输需要的读数据

S_AXI_RREADY : in std_logic

读准备,此信号表明主设备可以接受读数据和响应信息

2、AXI 总线通道握手信号之间的依赖性

AXI总共有5个通道,每个通道都有一对valid & ready信号,发送方通过valid信号来指示什么时候数据和控制信息有效,接收方通过ready来指示可以接受数据和控制信息,传输的信息发生在vaild和ready同时为高电平的情况下。每个通道之间可以独立握手,相互之间关系灵活。读数据必须跟在与其数据相关联的地址之后,写响应必须在于其相关联的写事务之后出现。

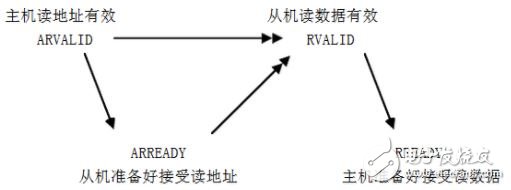

读事务握手依赖关系如图:

(1)设备可以在ARVALID出现的时候在给出ARREADY信号,也可以先给出ARREADY信号,再等待ARVALID信号。

(2)设备必须等待ARVALID和ARREADY信号都有效才能给出RVALID信号,开始数据传输。只有当读地址发送完成后,才能进行读数据的传输(箭头形状不同)

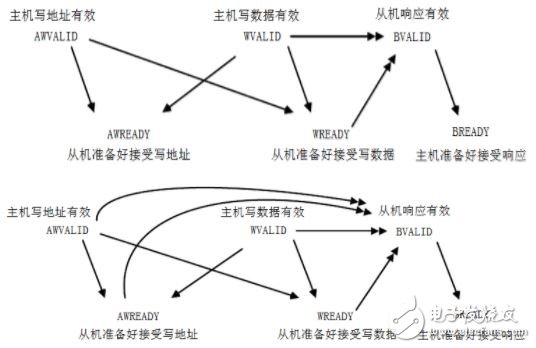

写事务握手依赖关系如图:

(1)主机不能等待设备先给出AWREADY或WREADY信号信号后再给出信号AWVALID或WVLAID。

(2)设备可以等待信号AWVALID或WVALID信号有效或者两个都有效之后再给出AWREADY信号。

(3)设备可以等待AWVALID或WVALID信号有效或者两个信号都有效之后再给出WREADY信号。

- 相关推荐

- 总线

-

AMBA 3.0 AXI总线接口协议的研究与应用2021-04-12 855

-

AXI总线协议简介2022-10-10 10090

-

玩转Zynq连载3——AXI总线协议介绍12019-05-06 0

-

AMBA3.0 AXI总线接口协议的研究与应用2023-09-20 0

-

AMBA AXI总线学习笔记2015-11-11 1098

-

AXI总线的MicroBlaze双核SoPC系统设计2017-10-31 1113

-

Xilinx zynq AXI总线全面解读2020-12-04 7131

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 5677

-

ZYNQ中DMA与AXI4总线2020-11-02 4333

-

AXI 总线交互分为 Master / Slave 两端2022-02-08 15792

-

AXI总线协议总结2021-02-04 1424

-

AXI总线工作流程2023-05-25 1000

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 2278

-

基于AXI总线的DDR3读写测试2023-09-01 4522

-

AXI IIC总线接口介绍2023-09-28 5250

全部0条评论

快来发表一下你的评论吧 !