任意波形发生器_DDS任意波形发生器的设计

通用测试仪器

描述

任意波形发生器是现代电子测试领域应用最为广泛的通用仪器之一,它的功能远比函数发生器强,可以产生各种理想及非理想的波形信号,对存在的各种波雷达、导航、宇航等领域。形都可以模拟,广泛应用于测试、通信、雷达、导航、宇航等领域。

本文介绍DDS任意波形发生器的设计。

任意波形发生器的功能

任意波形发生器既具有其他信号源的信号生成能力,又可以通过各种编辑手段产生任意的波形采样数据,方便地合成其他信号源所不能生成的任意波形,从而满足测试和实验的要求。任意波形发生器的主要功能包括:

(1)函数发生功能

基础实验中,为了验证电路功能、稳定性和可靠性,需要给它施加理想波形,任意波形发生器能替代函数发生器提供正弦波、方波、三角波、锯齿波等波形,还具有各种调制和扫频能力。利用任意波形发生器的这一基础功能就能满足一般实验的信号需求。

(2)任意波形生成

出于各种干扰的存在以及环境的变化,实际运行在实际电子环境中的设备,电路中往往存在各种信号缺陷和瞬变信号,例如过脉冲、尖峰、阻尼瞬变、频率突变等。任意波形发生器可以模拟这些特殊信号,以测试系统的实际性能。

(3)信号还原功能

在一些军事、航空等领域,有些电路运行环境很难估计,在设计完成之后,在现实环境中还需要更进一步的实验验证,而有些实验的成本很高或者风险性很大(如飞机试飞时发动机的运行情况),人们不可能重复作实验来判断所设计产品的可行性和稳定性。此时,可以利用任意波形发生器的信号还原功能。在做一些高耗费、高风险实验时,可以通过数字示波器把现实中的实际波形记录下来,再通过计算机接口下载到任意波形发生器,通过任意波形发生器还原实验中的实际做进一步的实验验证工作。

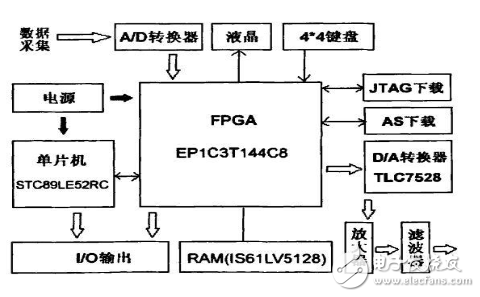

硬件结构说明

设计过程

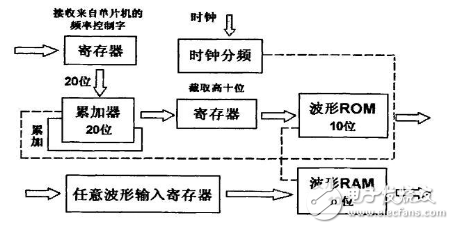

在本系统中,DDS是任意波形实现的技术关键,其核心为相位累加器(全加器与数字寄存器)与ROM波形查询表构成。那么我们设计DDS的框图如下

建立一个模块实现从单片机接收来的频率控制字的寄存功能,作为寄存器。全加器实现20位的相位累加,通过频率控制字作为步长进行控制。由于FPGA内输出位数有限,因此建立一个模块进行高位截断,只取高十位,接收累加器输出的数据。然后再通过波形ROM完成波形的查找与输出。这部分为固定的正弦波、三角波、方波与锯齿波等常规波形的输出部分。任意波形部分,则需要一个能随时接受数据更新的RAM,其数据的写入由单片机控制,接收上位机的下传数据,其数据的读取由DDS中的地址发生器控制,这样即可产生任意波形输出。

固定波形输出

在FPGA内部实现高速的多位数相位累加器,输出地址信号,控制读出波形存储器中存放的波形幅度数字信号。通过改变相位累加器的相位增量M,即地址间隔的改变,控制读出波形存储器一个周期正弦波幅值的数目,达到输出频率的控制。其输出的频率为 ,其中fclk为系统时钟频率,N为相位累加器的位数,M为相位增量--频率控制字,由公式可知fout与肘成正比,控制M就可以控制输出的频率。如要频率步进为l0Hz,则要求

,其中fclk为系统时钟频率,N为相位累加器的位数,M为相位增量--频率控制字,由公式可知fout与肘成正比,控制M就可以控制输出的频率。如要频率步进为l0Hz,则要求 。

。

保证在输出最高频率输出时有32个点的波表数据输出,则要求时钟为3.2MHz。将50MHz的时钟10分频,得到5MHz的信号作为累加器的计数信号。则fclk=5MHz,2N=500000,因此,N可取20,2N=1048576。则fout=-4.77M,M=0.21fout。利用计算机输入要输出的频率,发送到单片机,单片机将对接收到的数据进行预算处理后发送给FPGA。

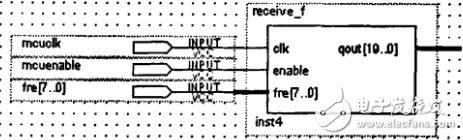

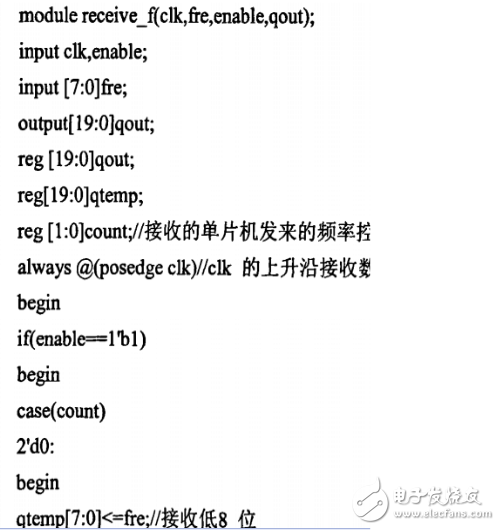

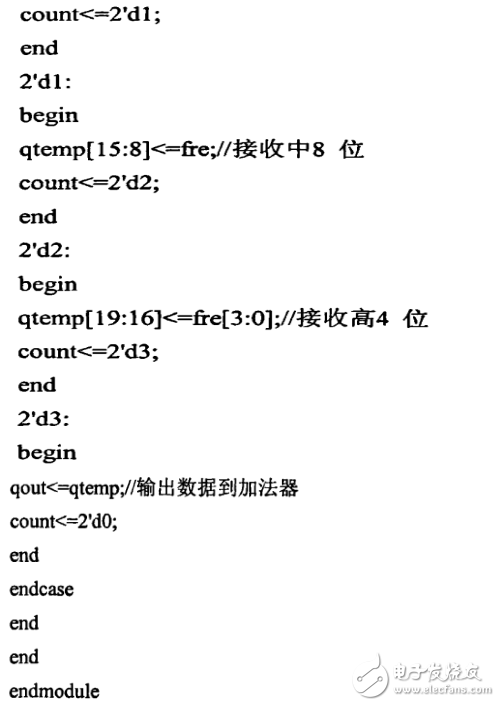

频率输入电路如图所示,接收8位的频率字长,输出为20位。

下面为STC89C52RC与EPlC3T144C8的接口程序,用控制字:

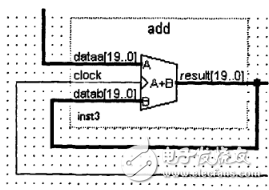

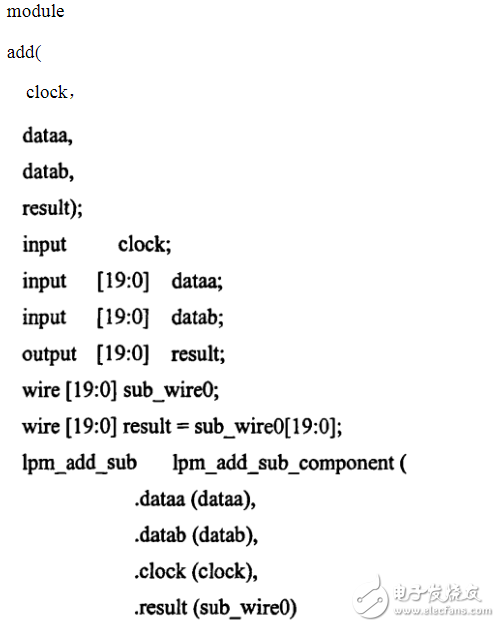

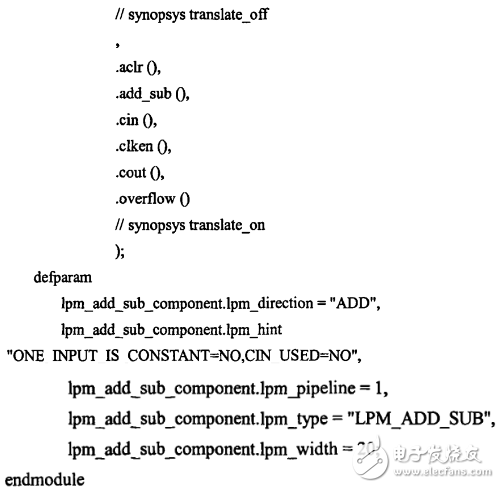

加法器

加法器为20位,自动累加,它以设定的频率控制字k作为步长来进行加法运算,当其和满时清零,并进行重新运算。电路图如下:

程序如下:

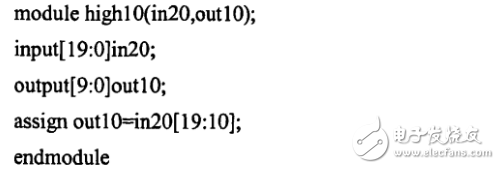

高十位寄存器

实现数据输入为20位,输出为10位,实现高位截断。程序为:

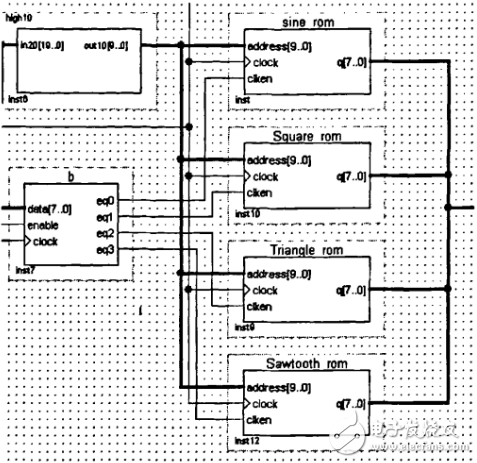

波形ROM及选择

本设计使用几个8bit的ROM,存储深度为1024点,用来存储正弦波等波形数据。每个波形数据存储在一个固定的ROM里,如下图。其中SineROM为正弦波存储模块,SquareROM为方波存储模块,Triangle-ROM为三角波存储模块,SwtoothROM为锯齿波存储模块。它们通过一个使能模块控制,采取低电平有效的方式,选择性读取任意模块的波形。一般每个模块都为高电平状态,即为不工作状态。每次输出波形时,仅有单独一个ROM_T_作(即工作模块为低电平,其他模块均为高电平),这样不仅保证可以按照需要输出固定波形,还可以避免波形输出发生非控制性的混杂。使能模块的输入端为行列式键盘,键盘中每一键单独使用,当某一键按下,则对应某一波形输入。因为4×4的键盘输出线为8位,仅为一根,因此输入端设为一根8位输入端口。通过设定,实现单键控制某~波形输出。本设计仅设定了4个固定波形ROM输出,即正弦波、方波、三角波和锯齿波,因此使能模块的选择输出线为4条,若增加新波形模块,可以更改输出端口的数量,进行扩展。

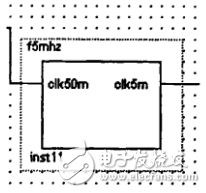

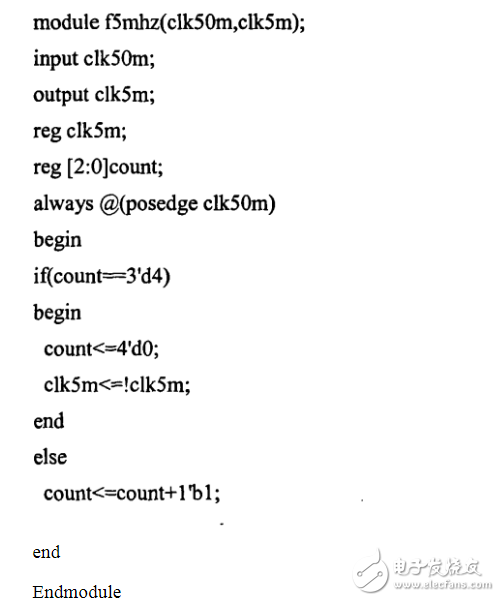

时钟分频

时钟分频电路如下,所以模块在同步时钟下协调工作,电路图如下:

程序如下:

任意波形输出

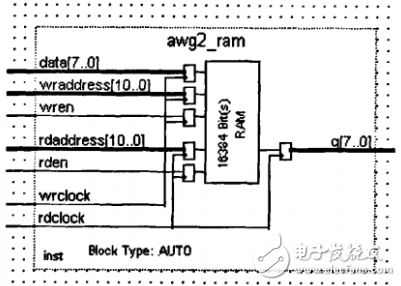

关于根据需要而产生的任意波形的设计如下:因为该任意波形是由上位机下传的波形数据,由单片机控制,所以必须设计一个能随时接受数据更新的RAM。数据传至任意波形的寄存器里,然后便可实现任意波形的输出。

选用的DA转换器为8位,所以RAM的字长也为8位,因此波形RAM的地址线的位数取lO位。为了实现任意波形数据的更新,波形RAM设计成为双口RAM。

-

函数信号发生器和任意波形信号发生器区别详解2026-02-09 432

-

任意波形发生器的基本架构2024-10-18 1767

-

什么是任意波形发生器2024-05-30 2989

-

任意波形发生器中波形生成方法2024-05-29 2957

-

什么是任意波形发生器?任意波形发生器是干什么用的?2024-05-28 2502

-

任意波形发生器的定义、特点及应用2024-05-21 2915

-

任意波形发生器与示波器怎么连接2024-05-15 2736

-

浅谈任意波形发生器及通道合并功能2024-01-19 1898

-

函数信号发生器是否与任意波形信号发生器相同2022-03-23 2080

-

基于USB的任意波形发生器2021-05-25 1236

-

基于DDS的任意波形/ 函数发生器之间的差别2020-03-29 3414

-

高速任意波形发生器的原理及硬件设计方案2019-11-26 8767

-

基于LabVIEW的任意波形发生器设计2016-01-20 1262

全部0条评论

快来发表一下你的评论吧 !