揭开Zynq Z-7000从SPI接口挂载的flash启动的神秘面纱

电子说

描述

各位在开发FPGA产品的时候,不仅需要熟知板子上的硬件,还要在硬件上运行代码,想要观测硬件上代码的运行是可以通过逻辑分析仪这种硬件调试仪器来进行的。内置有Xilinx Spartan-6 FPGA的Digital Discovery提供了高速的逻辑分析功能,能够让开发者观察和分析板子上的信号流,同时,今天给各位介绍另外一款Xilinx公司芯片的产品Zynq Z-7000 SoC,我们一起来揭开它从SPI接口挂载的flash启动的神秘面纱。

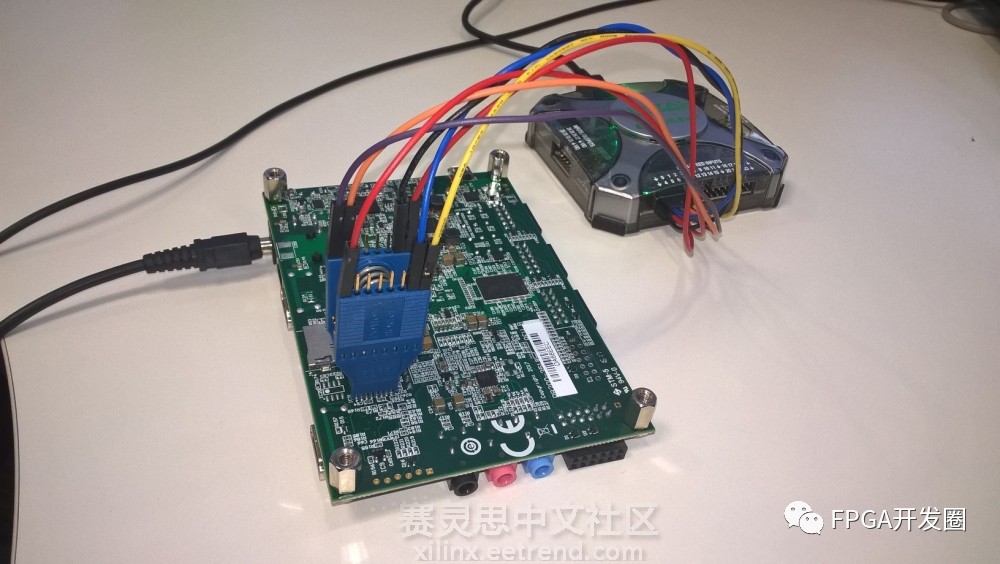

Zynq板从SPI端口的flash启动的过程,使用的仪器是Digilent公司的Digital Discovery。使用Digital Discovery而不是逻辑分析仪的原因有两个,首先,QSPI传输是在较高的时钟频率下进行的,在此案例中很可能就超过了100MHz,所以需要较高的采样率;其次,Digital Discovery有着512 MB的DDR,能够存储更多的采集过来的信号样本。那么,说了这么多的理论,各位是不是已经想知道怎么才能使Digital Discovery和Zynq连接到一起呢?具体的连接方式如图.1所示,将Digital Discovery的逻辑采样端口接到Zynq的falsh芯片的相应的引脚上,然后将Digital Discovery通过USB跟PC机相连接,用上位机Waveforms来进行信号的采集和处理。

图.1 用Digital Discovery逻辑分析仪捕获Zynq Z-7000 SoC的启动信号的连接方法

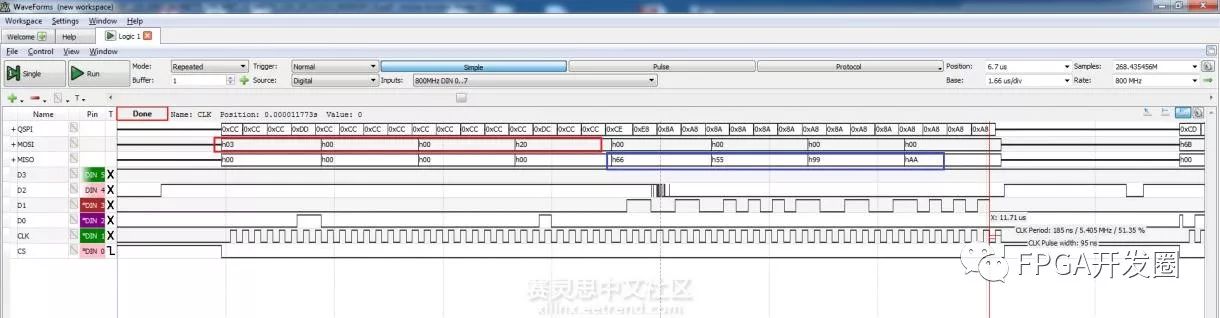

最大的QSPI时钟频率大约是100MHz,当启动的时候,整体的启动时间大约是700ms,这就需要很大的采样率,Digital Discovery能支持这样的频率,268万条指令在200MHz的传输条件下需要1.3秒的时间。设置在CS信号的下降沿触发采样,数据的采样需要占用大量的计算机内存,而且处理数据的时间也是相对较长的。图.2展示了整体的QSPI的传输波形图。注意在所获得波形的最左边时钟的频率从5.4MHz变到了25MHz。

图.2 Digilent公司的Digital Discovery逻辑分析仪捕获Zynq Z-7000启动的全过程

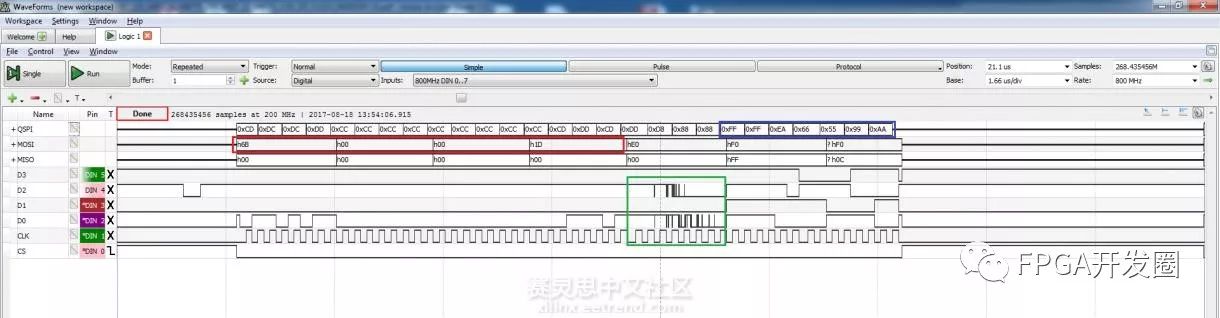

如果想要去理解数据传输所代表的意思,可以参考Zynq TRM和对应flash的数据手册。指令从Zynq传输到flash通常是通过SPI的D0引脚,第一个指令发送的是0x03 0x00 0x00 0x20(图.3的红色框框部分),此指令的意思是SPI READ,读的地址是0x20;相应的,收到的回复信号是经过SPI的D1引脚获得的,收到的信号为0x66 0x55 0x99 0xaa(图.3的蓝色框框部分所示),在Zynq TRM的170页到179页解释了收到的信号的意思是flash告诉Zynq此flash是支持QSPI的,通过观察发现,在读指令的地方SPI的时钟频率是5.405MHz,这个时钟的频率相对较低。在读指令之后,flash支持QSPI,所有的传输都会在四根QSPI数据线上进行。下一个指令是0x6b,紧跟着的是3byte的物理地址,如图.4红色框内所示,0x6b代表的是四次读写指令,flash回应的数据在8个时钟周期之后(图.4中绿色框内所示)能在QSPI信号线上被观察到,如图.4蓝色框内所示。

图.3 Zynq发送给flash的第一个读信号指令以及flash的反馈信号波形

图.4 Zynq的四次读写指令以及QSPI信号的相应

Zynq-7000 AP SoC集成了ARM处理器核和硬件可编程的FPGA于一身,集成了CPU,DSP,ASSP,混合信号处理装置等在一个芯片上,能够用于主要的数据分析和硬件加速上,有着很好的性能价格比。而Digital Discovery里面使用了Xilinx公司的Spartan-6 FPGA,有着较高的logic-to-pin比率,内置MicroBlaze软核,支持800Mb/s的DDR3,支持丰富的I/O协议,所以在性能上能够胜任逻辑分析仪的工作。

用逻辑分析仪来捕获处理器启动时候的信号波形不足为怪,但是在这个例子中是使用了Digital Discovery的逻辑分析仪功能,突出的地方就是Xilinx公司的两款芯片的交互,演绎了本次的启动信号揭秘之旅。Digital Discovery和Zynq SoC都是很出色的产品,一个是硬件开发者的便携式调试神奇,一个是硬件开发者的高性能开发板,是不是想自己亲手试一试了呢?

-

用智能DAC揭开医疗报警设计的神秘面纱2024-09-14 289

-

揭开快充芯片的神秘面纱2024-04-15 1548

-

新能源汽车的“隐形护卫”,揭开WAYON维安Auto TVS的神秘面纱2023-01-06 1833

-

揭开数字健康应用的AI和机器学习的神秘面纱2022-12-01 1311

-

ZYNQ的启动流程2022-05-07 8602

-

AN40-揭开开关电容器过滤的神秘面纱2021-04-27 777

-

MT-001: 揭开公式(SNR = 6.02N + 1.76dB)的神秘面纱2021-03-20 1575

-

揭开深记忆示波器的神秘面纱2019-09-23 1245

-

Duskers - 揭开科幻生存游戏中的神秘面纱2018-11-08 4047

-

ZYNQ-7000如何生成从Flash和SD卡启动的镜像文件2018-05-28 11825

-

揭开vivo APEX全面屏的神秘面纱2018-03-21 2489

-

苹果iPhone手机神秘面纱被揭开2010-04-17 685

-

揭开连接出现小叹号不能上网问题的神秘面纱2010-02-23 933

-

[分享]揭开zzz 手机神秘面纱2009-05-31 3766

全部0条评论

快来发表一下你的评论吧 !