CD4013介绍_CD4013分频电路工作原理解析

接口/时钟/PLL

描述

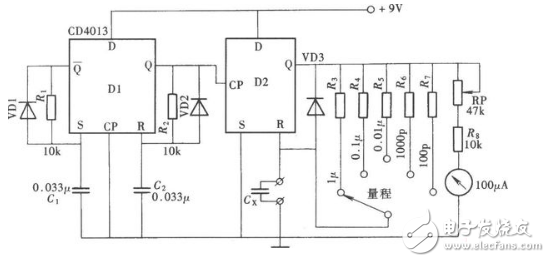

在电子技术中,N/2(N为奇数)分频电路有着重要的应用,对一个特定的输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。CD4013是双D触发器,在以CD4013为主组成的若干个二分频电路的基础上,加上异或门等反馈控制,即可很方便地组成N/2分频电路。

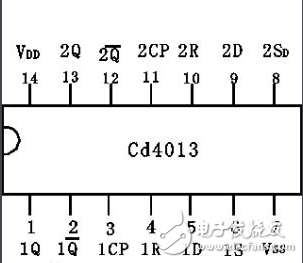

CD4013由两个相同的、相互独立的数据型触发器构成。每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出。此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计数器和触发器。在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。置位和复位与时钟无关,而分别由置位或复位线上的高电平完成。

CD4013分频电路工作原理

设电路初始状态均在复位状态,Q1、Q2端均为低电平。当fi信号输入时,由于输入端异或门的作用(附表是异或门逻辑功能表),其输出还受到触发器IC2的Q2端的反馈控制(非门F2是增加的一级延迟门,A点波形与Q2相同)。在第1个fi时钟脉冲的上升沿作用下,触发器IC1、IC2均翻转。由于Q2端的反馈作用使得异或门输出一个很窄的正脉冲,宽度由两级D触发器和反相门的延时决定。当第1个fi脉冲下跳时,异或门输出又立即上跳,使IC1触发器再次翻转,而IC2触发器状态不变。这样在第1个输入时钟的半个周期内促使IC1触发器的时钟脉冲端CL1有一个完整周期的输入,但在以后的一个输入时钟的作用下,由于IC2触发器的Q2端为高电平,IC1触发器的时钟输入跟随fi信号(反相或同相)。本来IC1触发器输入两个完整的输入脉冲便可输出一个完整周期的脉冲,现在由于异或门及IC2触发器Q2端的反馈控制作用,在第1个fi脉冲的作用下得到一个周期的脉冲输出,所以实现了每输入一个半时钟脉冲,在IC1触发器的Q1端取得一个完整周期的输出。

CD4013分频电路图

-

关于CD4013的迷惑点2025-01-21 454

-

关于CD4013电源的问题如何解决2025-01-20 551

-

CD40132023-02-21 1389

-

用CD4013双D触发器做的脉冲4分频器资料推荐2021-05-13 2082

-

用CD4013实现一按键双功能电路,CD4013 Light Switch2018-09-20 5687

-

用CD4013做二分频,未达到分频效果,想请各路大神看看是什么原因~2018-04-19 6778

-

cd4013中文资料详细介绍2017-11-07 8077

-

cd4013逻辑电路图与真值表_cd4013工作原理2017-10-27 15013

-

cd4013的工作原理_在电路中可以用什么代替2017-10-23 11710

-

基于集成电路CD4013的双稳态电路2014-08-04 45688

-

CMOS集成CD4013触摸开关2010-04-09 7224

-

cd4013应用电路2008-01-09 14658

全部0条评论

快来发表一下你的评论吧 !