什么是拉电流_什么是灌电流_拉电流和灌电流有什么区别

模拟技术

描述

什么是拉电流

由于数字电路的输出只有高、低(0,1)两种电平值,高电平输出时,一般是输出端对负载提供电流,其提供电流的数值叫“拉电流”。例如在使用反向器作输出显示时,当输出端为高电平时才符合发光二极管正向连接的要求,但这种拉电流输出对于反向器只能输出零点几毫安的电流用这种方法想驱动二极管发光是不合理的(因发光二极管正常工作电流为5~10mA)。

什么是灌电流

当反向器输出端为低电平时,发光二极管处于正向连接情况,在这种情况下,反向器一般能输出5~10mA的电流,足以使发光二极管发光,所以这种灌电流输出作为驱动发光二极管的电路是比较合理的。因为发光二极管发光时,电流是由电源+5V通过限流电阻R、发光二极管流入反向器输出端,好像往反向器里灌电流一样,因此习惯上称它为“灌电流”输出。

灌电流与拉电流的区别介绍

当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。由三极管输出特性曲线也可以看出,灌电流越大,饱和压降越大,低电平越大。

然而,逻辑门的低电平是有一定限制的,它有一个最大值UOLMAX。在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOLMAX ≤0.4~0.5V。所以,灌电流有一个上限。

当逻辑门输出端是高电平时,逻辑门输出端的电流是从逻辑门中流出,这个电流称为拉电流。拉电流越大,输出端的高电平就越低。这是因为输出级三极管是有内阻的,内阻上的电压降会使输出电压下降。拉电流越大,输出端的高电平越低。

然而,逻辑门的高电平是有一定限制的,它有一个最小值UOHMIN。在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOHMIN ≥2.4V。所以,拉电流也有一个上限。

可见,输出端的拉电流和灌电流都有一个上限,否则高电平输出时,拉电流会使输出电平低于UOHMIN;低电平输出时,灌电流会使输出电平高于UOLMAX。所以,拉电流与灌电流反映了输出驱动能力。(芯片的拉、灌电流参数值越大,意味着该芯片可以接更多的负载,因为,例如灌电流是负载给的,负载越多,被灌入的电流越大)

由于高电平输入电流很小,在微安级,一般可以不必考虑,低电平电流较大,在毫安级。所以,往往低电平的灌电流不超标就不会有问题。用扇出系数来说明逻辑门来驱动同类门的能力,扇出系数No是低电平最大输出电流和低电平最大输入电流的比值。

在集成电路中, 吸电流、拉电流输出和灌电流输出是一个很重要的概念。

拉即泄,主动输出电流,是从输出口输出电流。

灌即充,被动输入电流,是从输出端口流入

吸则是主动吸入电流,是从输入端口流入

吸电流和灌电流就是从芯片外电路通过引脚流入芯片内的电流,区别在于吸收电流是主动的,从芯片输入端流入的叫吸收电流。灌入电流是被动的,从输出端流入的叫灌入电流。

拉电流是数字电路输出高电平给负载提供的输出电流,灌电流时输出低电平是外部给数字电路的输入电流,它们实际就是输入、输出电流能力。

吸收电流是对输入端(输入端吸入)而言的;而拉电流(输出端流出)和灌电流(输出端被灌入)是相对输出端而言的。

给一个直观解释:

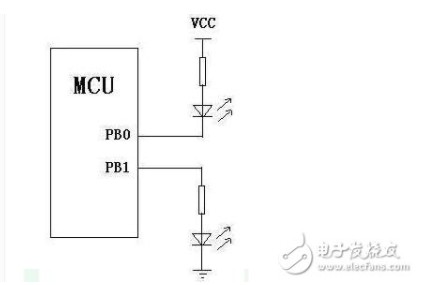

图中PB0输出0,LED会亮,PB0的电流方向是流向PB0也就是灌电流了;而PB1要输出1,LED会亮,PB1的电流方向是从PB1流出,也就是拉电流了。

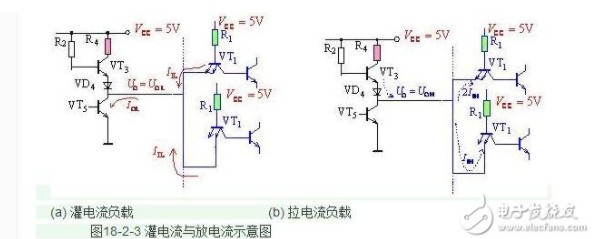

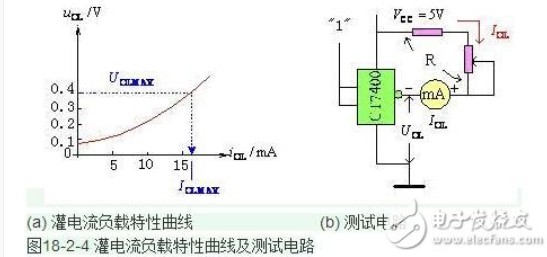

在实际电路中灌电流是由后面所接的逻辑门输入低电平电流汇集在一起而灌入前面逻辑门的输出端所形成,读者参阅图18-2-3自明。显然它的测试电路应该如图18-2-4(b)所示,输入端所加的逻辑电平是保证输出端能够获得低电平,只不过灌电流是通过接向电源的一只电位器而获得的,调节的电位器可改变灌电流的大小,输出低电平的电压值也将随之变化。

当输出低电平的电压值随着灌电流的增加而增加到输出低电平最大值时,即uOL=UOLMAX时所对应的灌电流值定义为输出低电平电流的量大值IOLMAX。

不同系列的逻辑电路,同一系列中不同的型号的集成电路,国家标准中对输出低电平电流的最大值IOLMAX的规范值的规定往往是不同的。比较常用的数值如下

TTL系列 IOLMAX=16mA

LSTTL74系列 IOLMAX=8mA

LSTTL54系列 IOLMAX=4mA

扇出系数NO是描述集成电路带负载能力的参数,它的定义式如下 18-2-1)

NO= IOLMAX / IILMAX

其中IOLMAX为最大允许灌电流,IILMAX是一个负载门灌入本级的电流。

No越大,说明门的负载能力越强。一般产品规定要求No≥8。

在决定扇出系数时,正确计算电流值是重要的,对于图18-2-3而言,后面所接的逻辑门的输入端有并联的情况。当输出为低电平时,后面逻辑门输入端流出的IIL,因有R1的限流作用,与并联端头数无关。但是,当输出为高电平时,电流的方向改变为流进输入端,后面逻辑门输入级的多发射极三极管相当有两个三极管并联。流入的IIH就要加倍,与并联端头数有关。对于图18-2-3,NOL=2,而NOH=3,输出低电平和输出高电平两种情况下,扇出系数可能是不同的。由于IIL的数值比IIH的数值要大很多,对于集成电路来说矛盾的主要方面在低电平扇出系数。所以,一般我们只需要考虑低电平扇出系数就可以了。

-

什么是灌电流和拉电流,灌电流和拉电流的意思2009-10-21 0

-

什么是拉电流,什么是灌电流?什么是吸收电流 ?2011-11-07 0

-

拉电流与灌电流的含义和区别2018-09-06 0

-

拉电流与灌电流(双向通讯思考)2018-10-09 0

-

拉电流和灌电流2019-06-03 0

-

灌电流是什么?拉电流又是什么2021-09-28 0

-

灌电流与拉电流有哪些区别2021-09-30 0

-

拉电流和灌电流是什么意思2021-10-08 0

-

拉电流负载和灌电流负载的区别在哪2021-10-14 0

-

灌电流和拉电流到底是什么2019-07-25 1640

-

拉电流和灌电流及吸收电流的详细介绍2020-12-09 1124

-

电路小科普:拉电流和灌电流2022-12-26 1891

-

什么是拉电流 、灌电流、吸收电流?2023-11-30 2528

-

拉电流和灌电流的区别是什么 拉电流和灌电流哪个大些2024-10-07 2117

-

拉电流和灌电流有什么用2024-09-14 554

全部0条评论

快来发表一下你的评论吧 !