利用MMCM实现多芯片相位对齐的串行收发器纠偏方法

FPGA/ASIC技术

描述

在一些特定的应用场景下,需要支持单板内多芯片串行收发器纠偏。要求各接收/发送机输入/出的数据相位差很小,比如250pS。为了达到该技术指标要求,必须使用多通道相位对齐技术、输入输出FIFO旁路技术。通常的相位对齐技术由于引入了Delay_Aligner,会带来2~4nS的相位不确定,不能满足系统指标要求。

这里介绍一种利用MMCM实现多芯片相位对齐的串行收发器纠偏方法:

1) 利用图1所示电路实现多芯片间的全局时钟相位对齐。该电路通过单板上的low Skew时钟分配器分发同相位时钟到多个相同的芯片的相同全局时钟管脚上,再由MMCM实现零延迟BUFG电路,实现到每个GT的USRCLK/2的延迟差最小,达到全板GT的USRCLK/2同相位的目的。

图1. 时钟架构图

2) 利用7系Tranceiver的Phase_Aligner实现TX/RXBUFFER Bypass。

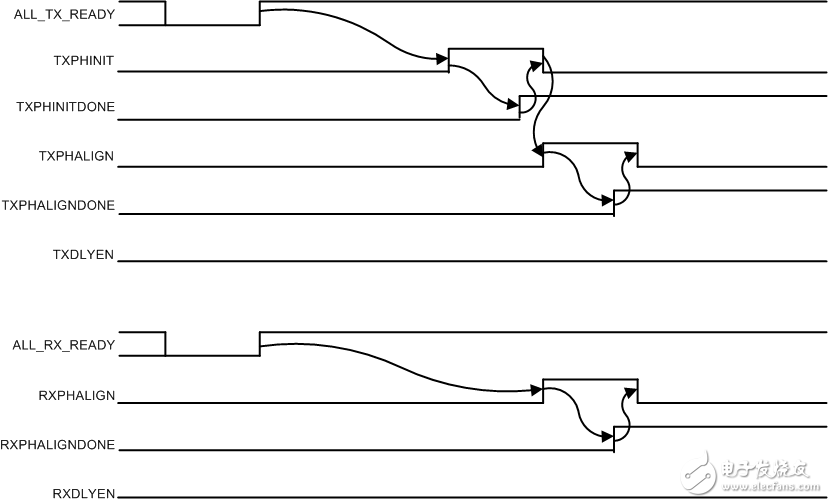

7系列GT(GTX,GTH,GTP)支持TXBUFFER/RXBUFFER Bypass功能,该功能将Tranceiver内部的XCLK的相位调整到与TXUSRCLK或RXUSRCLK同相(误差小于1UI)。这样,由于整个单板的所有通道的TXUSRCLK和RXUSRCLK同相位(由时钟架构保证。即使有误差,也可以重复并在设计中校准)。具体Phase_Aligner控制时序见图2.

图2. 全局时钟作为TXUSRCLK/RXUSRCLK的Phase_Aligner控制时序图

应用案例:某公司需要一个2048通道,且延迟差在250pS内的解决方案。系统分解到8块单板实现,每块单板支持128通道。通过背板设计,可以保证到达每块单板的100MHz高质量时钟的相位是同相的。这样,只要单板内的各通道延迟差能控制在200pS内,就可以实现该要求。XILINX采用上述解决方案,实现了该需求,且在实际的系统中满足了系统要求。

- 相关推荐

- 热点推荐

- 串行收发器

-

高速串行收发器原理及芯片设计2024-05-16 2762

-

多模光纤收发器分ab端吗 多模光纤收发器怎么连接2024-01-23 5086

-

#fpga 利用IBERT IP核实现GTX收发器硬件误码率测试实例明德扬科技 2023-09-05

-

串行异步收发器相关资料推荐2021-11-18 1695

-

详细讲解电角度相位对齐的基本方法2019-02-05 9568

-

Virtex-7 2000T GTX收发器实现高速串行性能2018-11-22 4387

-

电角度相位对齐的基本方法总结2017-02-10 4342

-

Xilinx推出UltraScale FPGA收发器设计2017-02-09 467

-

Exar公司推出可简化双协议系统设计的串行收发器SP3372010-12-31 1321

-

基于CPLD的异步串行收发器设计2010-07-19 1110

-

通用串行总线收发器MIC2550及其应用2010-03-03 2003

-

Maxim发布新一代多协议收发器芯片组2010-01-25 1049

-

Maxim推出下一代多协议收发器芯片组2010-01-23 1002

-

多协议收发器2009-04-30 1227

全部0条评论

快来发表一下你的评论吧 !