LDO 的运行困境:低裕量和最小负载

电源设计应用

描述

LDO裕量及其对输出噪声和PSRR 的影响

基于深亚微米工艺的最新千兆级模拟电路对电源电压的要求越来越低,在有些情况下,还不到1 V。这些高频电路往往需要较大的供电电流,因此,可能在散热方面存在困难。设计目标之一是使功耗降至电路性能绝对需要的水平。

开关模式DC-DC转换器是最高效的电源,有些器件效率可超过95%,但其代价是电源噪声,通常在较宽带宽范围内都存在噪声问题。通常用低压差线性调节器(LDO)清除供电轨中的噪声,但也需要,在功耗和增加的系统热负荷之间做出权衡。为了缓解这些问题,使用LDO 时,可使输入和输出电压之间在较小的压差(裕量电压)本文旨在讨论低裕量电压对电源抑制和总输出噪声的影响。

LDO电源抑制与裕量

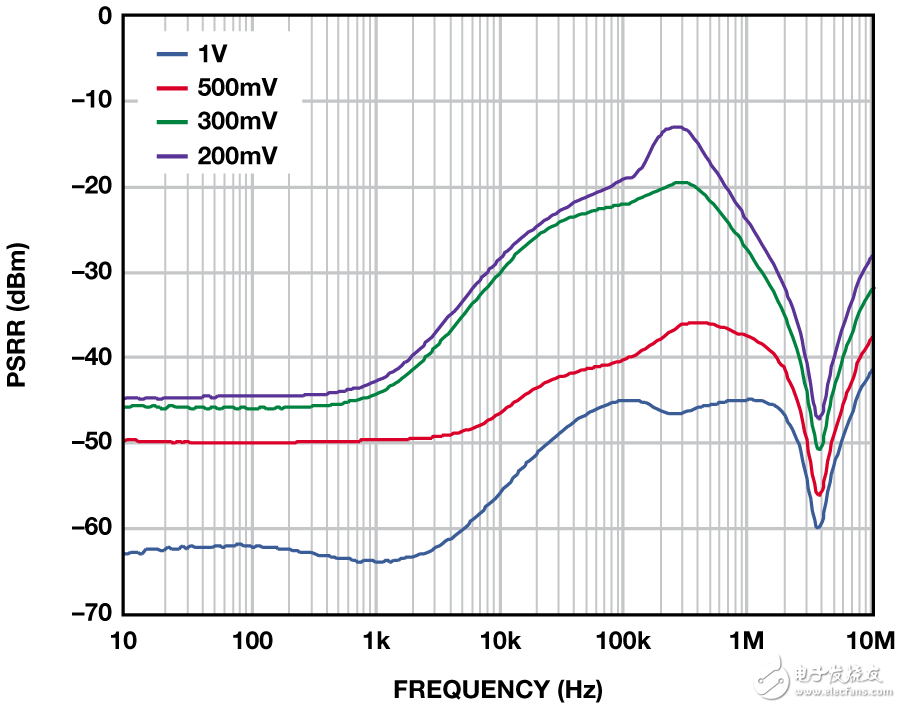

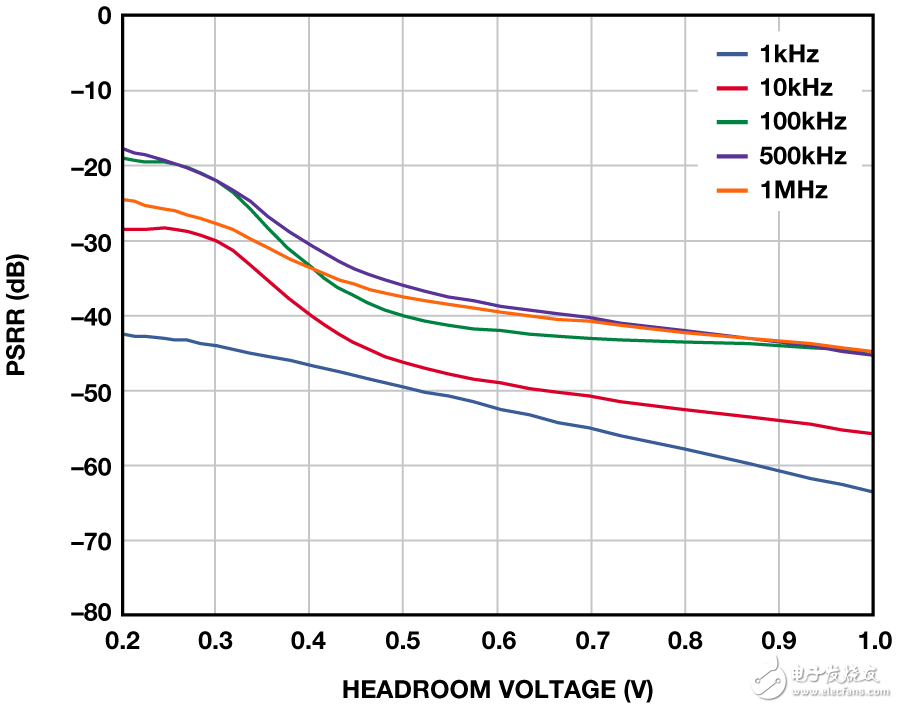

LDO 电源抑制比(PSRR)与裕量电压相关——裕量电压指输入与输出电压之差。对于固定裕量电压,PSRR随着负载电流的提高而降低,大负载电流和小裕量电压条件下尤其如此。图1所示为ADM7160超低噪声、2.5V线性调节器在200mA 负载电流和200mV、300mV、500mV 和1V 裕量电压条件下的PSRR。随着裕量电压的减小,PSRR也会减小,压差可能变得非常大。例如,在100kHz下,裕量电压从1V 变为500 mV,结果将使PSRR减少5dB。然而,裕量电压的较小变化,从500mV 变为300mV,结果会导致PSRR下降18dB 以上。

图1. ADM7160 PSRR与裕量

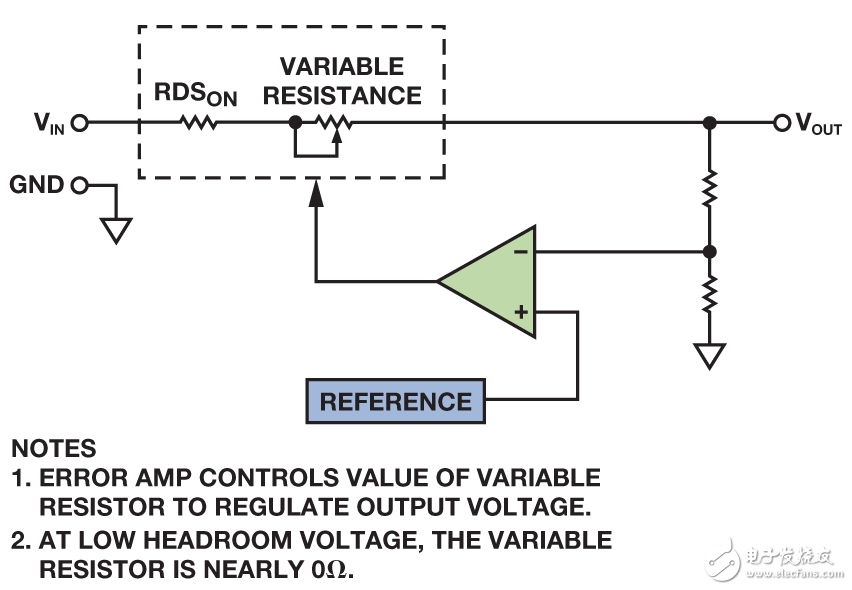

图2 显示了LDO 的框图。随着负载电流的增加,PMOS 调整元件的增益会减小,它脱离饱和状态,进入三极工作区。结果使总环路增益减小,导致PSRR下降。裕量电压越小,增益降幅越大。随着裕量电压继续减小到一个点,此时,控制环路的增 益降至1,PSRR降至0dB。

导致环路增益减小的另一个因素是通路中元件的电阻,包括FET的导通电阻、片内互连电阻和焊线电阻。可以根据压差推算出该电阻。例如,采用WLCSP封装的ADM7160在200mA下的最大压差为200mV。利用欧姆定律,调整元件的电阻约为1Ω,可以把调整元件近似地当作固定电阻与可变电阻之和。

流过该电阻的负载电流导致的压差减去FET的漏极源极工作电压。例如,在1 Ω FET条件下,200 mA的负载电流会使漏极源极电压下降200 mV。在估算裕量为500 mV或1 V 的LDO的PSRR 时,必须考虑调整元件上的压差,因为调整FET的工作电压实际上只有300 mV或800 mV。

图2. 低压差调节器的框图

容差对LDO裕量的影响

客户通常要求应用工程师帮助他们选择合适的LDO,以便在负载电流Z 条件下从输入电压Y产生低噪声电压X,但在设置这些参数时,往往忽略了输入和输出电压容差这个因素。随着裕量电压值变得越来越小,输入和输出电压的容差可能对工作条件造成巨大的影响。输入和输出电压的最差条件容差始终会导 致裕量电压下降。例如,最差条件下的输出电压可能高1.5%,输入电压可能低3%。当通过一个3.8 V源驱动3.3 V的调节器时,最差条件裕量电压为336.5 mV,远低于预期值500 mV。在最差条件负载电流为200 mA的情况下,调整FET 的漏极源极电压只有136.5 mV。在这种情况,ADM7160 PSRR可能远远低于标称值55 dB(10 mA时)。

压差模式下的LDO的PSRR

客户经常会就LDO在压差模式下的PSRR请教应用工程师。开始时,这似乎是个合理的问题,但只要看看简化的框图,就知道这个问题毫无意义。当LDO工作于压差模式时,调整FET 的可变电阻部分为零,输出电压等于输入电压与通过调整FET 的RDSON的负载电流导致的压降之差。LDO不进行调节,而且没有增益来抑制输入端的噪声;只是充当一个电阻。FET的RDSON与输出电容一起形成一个RC滤波器,提供少量残余PSRR,但一个简单的电阻或铁氧体磁珠即可完成同一任务,而且更加经济高效。

在低裕量工作模式下维持性能

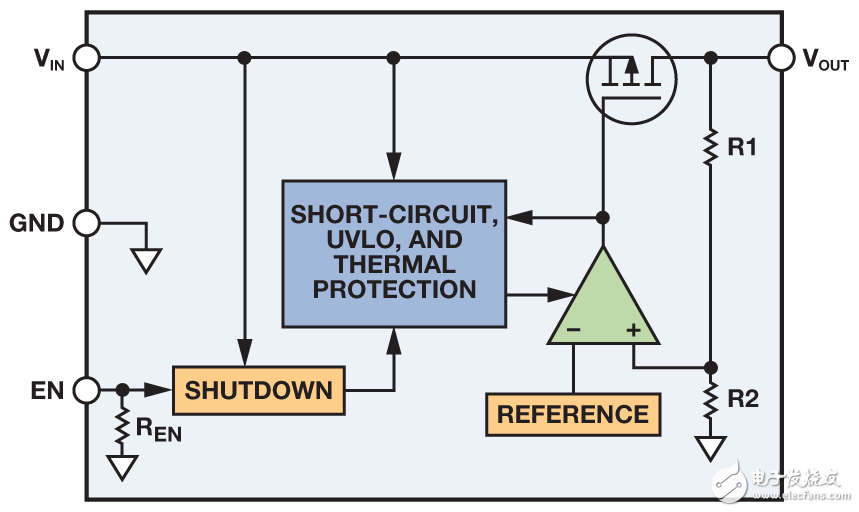

在低裕量工作模式下,需要考虑裕量电压对PSRR的影响,否则,会导致输出电压噪声水平高于预期。如图3 所示的PSRR与裕量电压关系曲线通常可在数据手册中找到,而且可以用来确定给定条件下可以实现的噪声抑制量。

图3. PSRR与裕量电压的关系

然而,有时候,通过展示LDO的PSRR如何有效滤除源电压中的噪声,可以更加容易地看到这种信息的利用价值。下面的曲线图展示了LDO在不同裕量电压下时,对总输出噪声的影响。

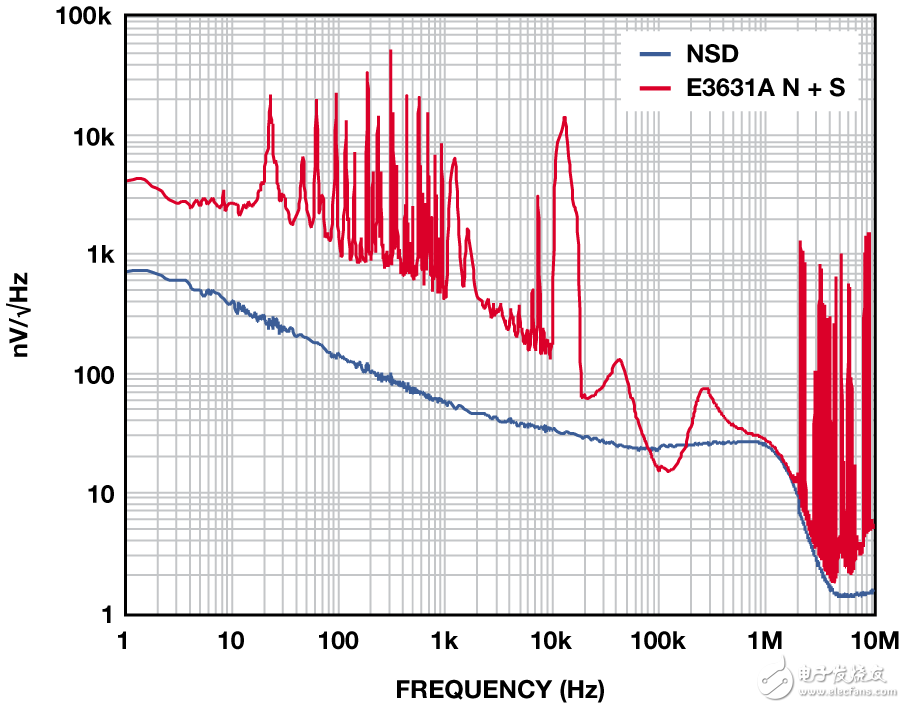

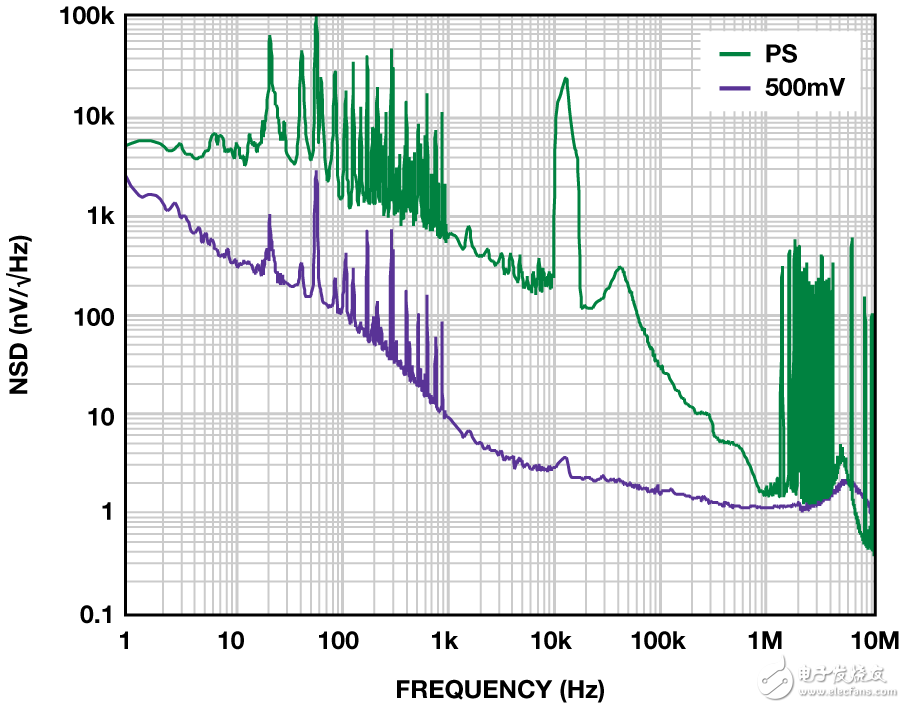

图4 展示的是2.5 V ADM7160在500 mV裕量和100 mA负载条件下,相对于E3631A台式电源的输出噪声,该台式电源在20 Hz至20 MHz范围内的额定噪声低于350 μV-rms。1 kHz以下的许多杂散为与60 Hz线路频率整流相关的谐波。10kHz以上的宽杂散来自产生最终输出电压的DC-DC转换器。1 MHz以上的杂散源于环境中与电源噪声不相关的RF 源。在10Hz至100kHz范围内,这些测试所用电源的实测噪声为56 μVrms,含杂散为104μV。LDO抑制电源上的所有噪声,输出噪声约为9 μV-rms。

图4. ADM7160噪声频谱密度(裕量为500 mV)

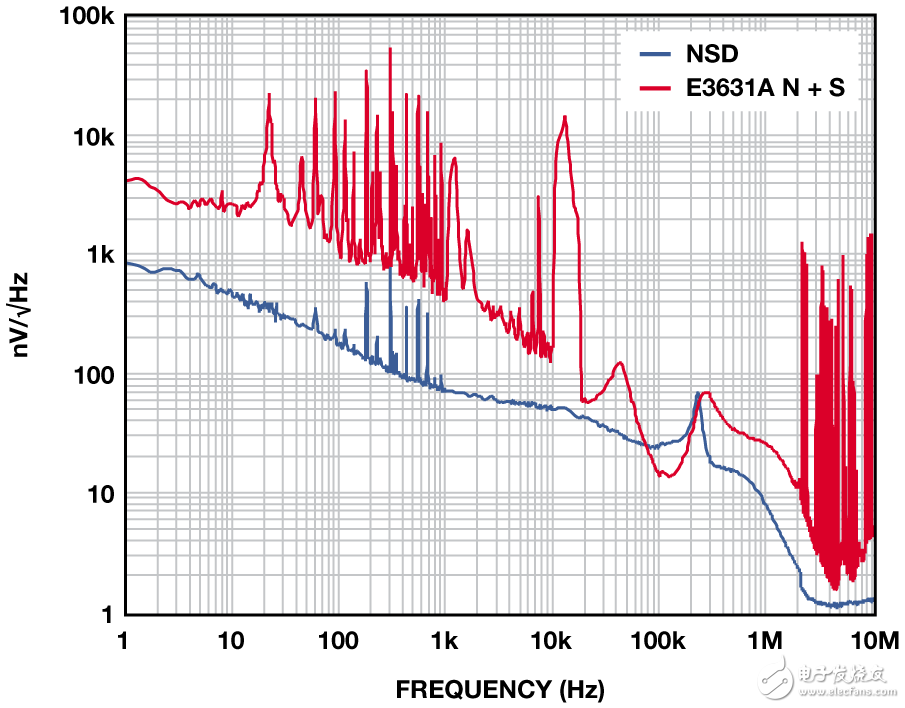

当裕量电压降至200 mV时,随着高频PSRR接近0 dB,100 kHz以上的噪声杂散开始穿过噪底。噪声略升至10.8 μV rms。随着裕量降至150 mV,整流谐波开始影响输出噪声,后者升至12μVrms。在大约250 kHz 处出现幅度适中的峰值,因而尽管总噪声的增加量并不大,但敏感电路也可能受到不利影响。随着裕量电压进一步下降,性能受到影响,与整流相关的杂散开始在噪声频谱中显现出来。图5所示为100-mV裕量条件下的输出。噪声已上升至12.5 μV rms。谐波所含能量极少,因此,杂散噪声只是略有增加,为12.7 μV rms。

图5. ADM7160噪声频谱密度(裕量为100 mV)

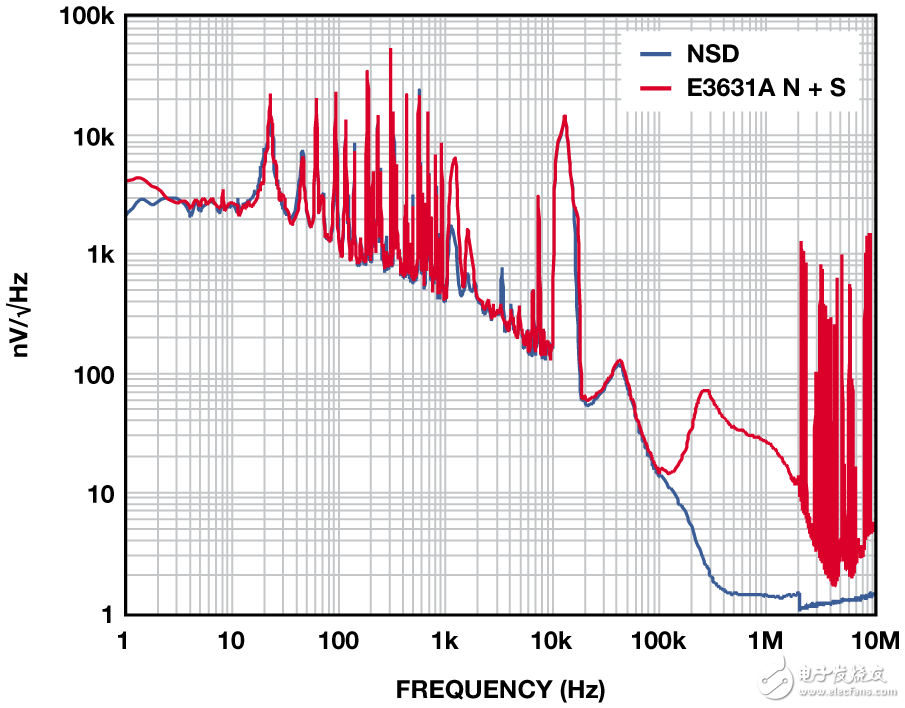

当裕量为75 mV时,输出噪声受到严重影响,整流谐波出现在整个频谱中。Rms噪声升至18 μV rms,噪声与杂散之和升至27μV rms。超过~200 kHz范围的噪声被衰减,因为LDO环路无增益,充当一个无源RC滤波器。当裕量为65 mV时,ADM7160采用压差工作模式。如图6 所示,ADM7160的输出电压噪声实际上与输入噪声相同。现在,rms噪声为53 μVrms,噪声与杂散之和为109 μV rms。超过~100 kHz 范围的噪声被衰减,因为LDO充当一个无源RC 滤波器。

图6. ADM7160在压差模式下的噪声频谱密度

高PSRR、超低噪声LDO

如ADM7150 超低噪声、高PSRR调节器一类的新型LDO实际上级联了两个LDO,因此,结果得到的PSRR约为各个级之和。这些LDO要求略高的裕量电压,但能够在1 MHz条件下实现超过60 dB的PSRR,较低频率下,PSRR可以远超100 dB。

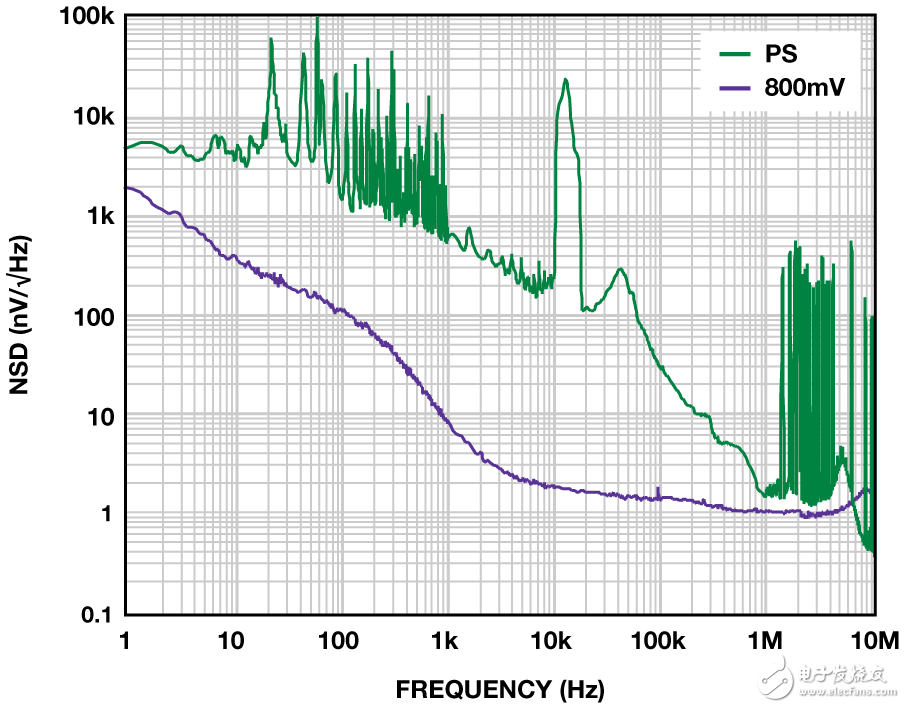

图7 所示为一个5 V的ADM7150的噪声频谱密度,其负载电流为500 mA,裕量为800 mV。10 Hz至100 kHz范围内,输出噪声为2.2 μV rms。随着裕量降至600 mV,整流谐波开始显现,但当输出噪声升至2.3 μV rms时,其对噪声的影响很小。

图7. ADM7150噪声频谱密度(裕量为800 mV)

当裕量为500 mV时,可在12 kHz处明显看到整流谐波和峰值,如图8所示。输出电压噪声升至3.9 μV rms。

图8. ADM7150 噪声频谱密度(裕量为500 mV)

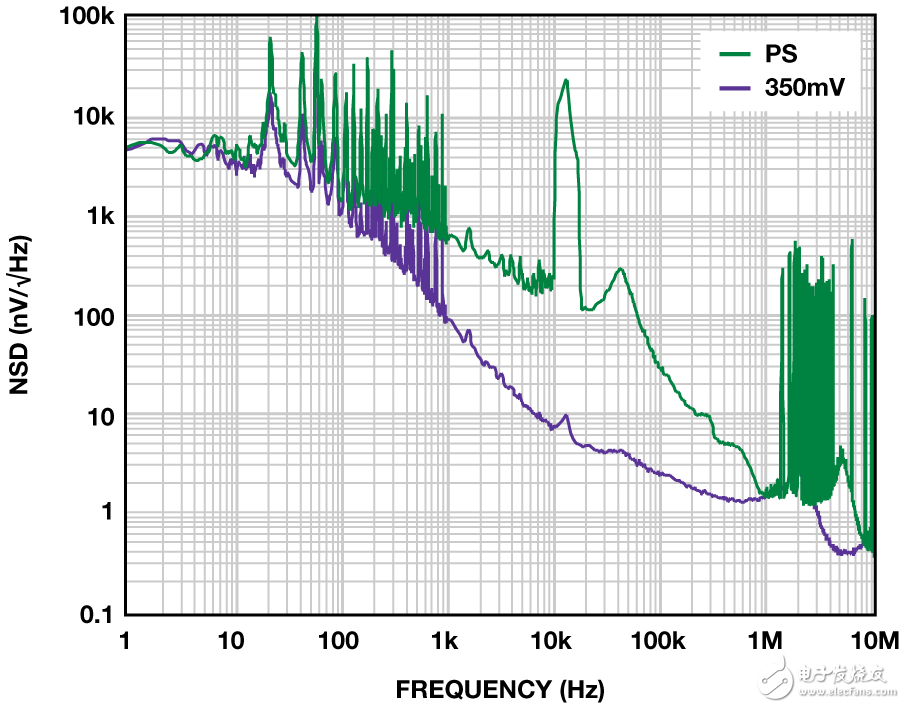

当裕量为350 mV时,LDO采用压差工作模式。此时,LDO再也不能调节输出电压,充当一个电阻,输出噪声升至近76 μV rms,如图9所示。只有FET的RDSON和输出端的电容形成的极点衰减输入噪声。

图9. ADM7150在压差模式下的噪声频谱密度

结论

现代LDO越来越多地用于清除供电轨中的噪声,这些供电轨通常通过可以在较宽频谱下产生噪声的开关调节器实现。开关调节器以超高的效率形成这些电压轨,但本身耗能的LDO既会减少噪声,也会导致效率下降。因此,应尽量降低LDO的工作裕量电压。

如前所述,LDO的PSRR为负载电流和裕量电压的函数,会随负载电流的增加或裕量电压的减少而减少,因为,在调整管的工作点从饱和工作区移至三极工作区时,环路增益会下降。

通过考虑输入源噪声特性、PSRR 和最差条件容差,设计师可以优化功耗和输出噪声,为敏感型模拟电路打造出高效的低噪声 电源。

在裕量电压超低的条件下,输入和输出电压的最差条件容差可能对PSRR形成影响。在设计时充分考虑最差条件容差可以确保可靠的设计,否则设计的具有较低的PSRR的电源解决方案,其总噪声也会高于预期。

- 相关推荐

- 热点推荐

- ldo

-

LDO的运行困境:低裕量和最小负载2023-11-24 442

-

LDO操作角:低裕量和最小负载2023-02-03 2460

-

ADI: LDO裕量及其对输出噪声和PSRR的影响2022-11-30 2709

-

【世说设计】LDO的运行困境:低裕量和最小负载2022-11-02 1824

-

对LDO的最小负载电流有何要求2021-10-11 2486

-

最小负载电流工作 — 零负载工作2019-10-22 2538

-

理解低压差稳压器(LDO)实现系统优化设计2019-10-18 2255

-

最小负载电流工作: 零负载工作2018-10-26 3497

-

电容性负载和相位裕度2018-10-25 3282

-

LDO的运行困境:低裕量和最小负载2018-10-23 2719

-

LDO裕量及其对输出噪声和PSRR的影响2016-01-07 790

全部0条评论

快来发表一下你的评论吧 !