用结构简单的套筒式共源共栅运算放大器实现高增益、高单位增益带宽和低功耗的设计

电子说

描述

1 引言

运算放大器作为模拟系统和混合信号系统中的一个重要电路单元,广泛应用于数/模与模/ 数转换器、有源滤波器、波形发生器和视频放大器等各种电路中。伴随着每一代CMOS 工艺 的发展,电源电压和晶体管沟道长度的持续减小,不断为运算放大器的设计提出了复杂的课 题。在A/D 转换器中,运算放大器是最关键的部件。比如,有限增益、带宽和有限压摆率 等运算放大器的非理想特性都会造成积分器中的电荷转移不完全,从而引起A/D转换器的非线性。与单端输出的运算放大器相比,全差分运算放大器能提供更大的输出电压摆幅,并具 有不易受共模噪声影响、更高的线性度、减少偶次谐波干扰以及偏置电路更简单等优点。

本文从分析和优化运算放大器的参数出发,实现了一款高性能CMOS 全差分运算放大器 的设计,其主要性能指标要求为:开环增益大于70dB,单位增益带宽大于80 MHz,转换速 率大于160 V/μs。

2 高增益CMOS 全差分运算放大器设计

2.1 结构选择与分析

常见的全差分运算放大器的结构有套筒式共源共栅、折叠式共源共栅和两级运放等。在 两级运放结构中,次极点频率由负载电容CL 决定,使速度受到限制,带宽较小,且功耗较 大,电源抑制比和共模抑制比也较差。与套筒式结构相比,折叠式共源共栅运放的输出电压 摆幅要大一些,但这是以较大的功耗和噪声、较低的电压增益和极点频率为代价得到的[2]。套 筒式共源共栅是各种不同运放结构*耗最低的一种,其增益也较高,可和普通的两级运放 相比。从本设计的应用出发,决定采用套筒式共源共栅结构来设计全差分运算放大器。

2.2 套筒式共源共栅运算放大器

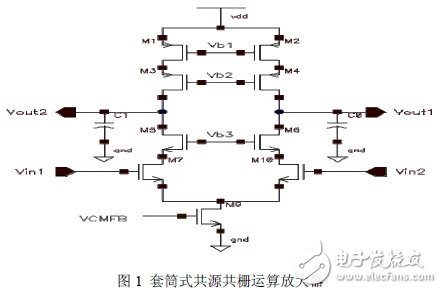

采用的套筒式共源共栅运算放大器主体结构如图1 所示。其中,M1、M2、M3 和M4 组成有源负载,其阻值很大,可提高运算放大器的增益。M7 和M8 是NMOS 差分输入对,用 于把输入电压变为电流;M7、M8 和M5、M6 一起组成差分式共源共栅结构。M9 用来产生 尾电流以抑制输入共模电平的变化对M7 和M8 的工作及输出电平的影响。Vb1、Vb2 和Vb3 为 三个偏置电压,VCMFB 为共模反馈电路产生的控制电压。

2.3 共模反馈电路

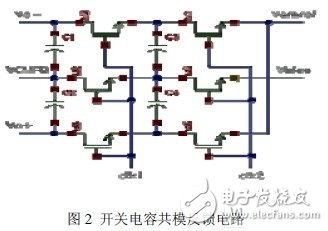

全差分运算放大器中通常需要一个共模反馈电路(CMFB),使受控的共模输出电压值接近 于某个特定值(通常约为电源电压的一半)[4]。CMFB 分连续时间和开关电容两种。由于本文设 计的运放用在全差分开关电容电路中,加之连续时间CMFB 具有限制差模输出信号幅度、增 加差模负载和增加静态功耗等缺点[5-6],因此采用开关电容CMFB,其实际结构如图2 所示。

图2 中的C1=C2,C3=C4,clk1 和clk2 为两相不交叠时钟信号,Vo-和Vo+接运放输出电 压,VCMFB 为该CMFB 产生的调节电压,Vcmref 代表期望的输出共模电压,Vbias 是使运放输出 共模电压刚好等于期望值时的电流源栅极偏压。当clk2 为高电平时,C3 和C4 预充电到 Vcmref-Vbias。当clk1 为高电平时,C1 和C3 并联,C2 和C4 并联,存储在C3 和C4 上的电荷 将发生转移,最终在C1 与C2 之间产生一个DC 补偿电压,叠加到运放的输出共模电压上, 从而保证运算放大器实际输出共模电压保持在预期值附近。

3 电路参数分析

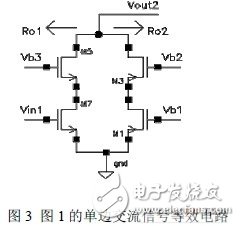

在图 1 所示的电路中,由于两条支路对称,所以当输入差模交流信号时,M9 的漏极电位 保持恒定,于是可认为M9 的漏极交流接地,由此得到图1 的单边交流信号等效电路,如图3 所示。

3.1 开环直流增益

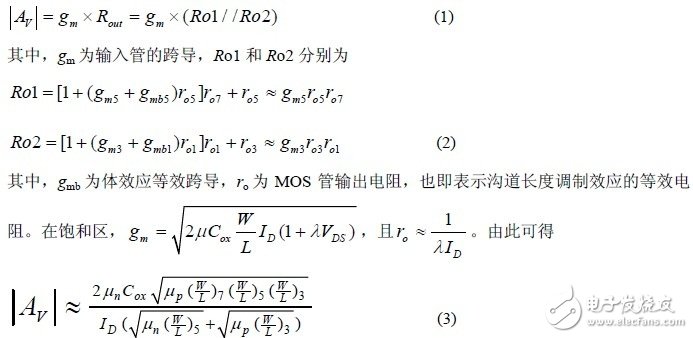

如图3 所示,单边增益等于输入管的跨导乘以输出电阻。输出电阻等于从输出节点看进去的两个共源共栅结构输出电阻的并联,因此有

上式指出了具体某个晶体管对电路直流增益的贡献,因此是晶体管参数调整的总体指导 依据。此外,从图1 可以看到,M5、M6、M7 和M8 处在信号通路上,故要保证其电容值最 小,因此在改变参数以增大直流增益的过程中,尽量保持最小尺寸不变而进行宽长比的整体 变化。而PMOS 管M1、M2、M3 和M4 对信号的影响小得多,增大其尺寸可非常有效地改变 直流增益。

3.2 单位增益带宽

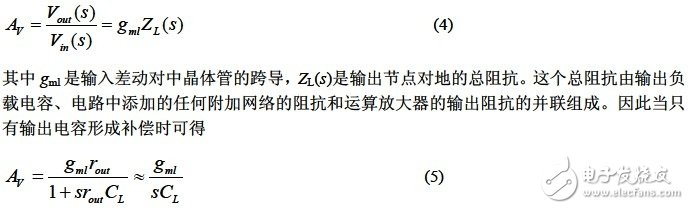

套筒式共源共栅运算放大器的小信号传递函数可写为

由(3)式和(10)式可知,增加输入差分管的W/L、减小负载电容是提高单位增益带宽的有效方法。

3.3 转换速率和建立时间

运算放大器在额定负载及输入阶跃大信号时,输出电压上升段(或下降段)线性部分的斜率 称为转换速率,也叫压摆率。图1 所示运放Vout1-Vout2 的压摆率SR=ID9/CL。本设计中负载电 容CL 为2.6 pF,转换速率要求大于160 V/μs,因此ID9 至少为0.42 mA。

建立时间指当运算放大器构成闭环负反馈时,在限定输出负载并输入阶跃信号的条件下, 输出电压从阶跃信号输入时起至输出电压上升到稳定值的误差容限内所需的时间。它分为线 性建立和非线性建立两个不同的阶段。线性建立阶段指输入差分小信号时,运算放大器的输 出由闭环作用控制的阶段。单位增益带宽越大,线性建立时间越短。非线性建立阶段是指当 输入差分大信号时,运算放大器的输出波形由转换速率决定的阶段,因此可通过适当增加尾 电流来缩短这段时间。

3.4 共模输入范围

输入共模电压范围定义为当差动信号为零时,能维持电路工作在饱和区的共模电平范围。 对于理想差分运算放大器,输入共模电压时输出应为零。而实际的差分运算放大器,电路既 不可能完全对称,尾电流源的输出阻抗也不可能为无穷大。因而,当输入共模电压时输出不 为零;甚至当输入共模电压超出某一范围时,运算放大器就不能再对差模信号进行正常放大。 从图1 可以看到,输入共模电压VIC 有:

4 仿真结果

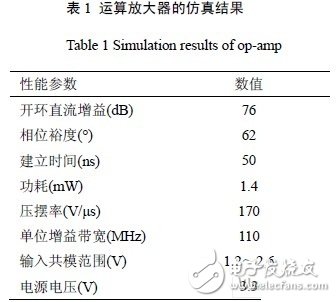

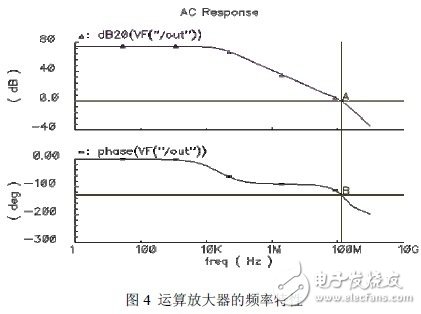

基于 SMIC 0.35 μm CMOS 工艺,在Cadence Spectre 模拟器上对该CMOS 运算放大器进 行仿真。结果如表1 所示。图4 给出了运算放大器的频率响应特性曲线。

5 结论

采用简单的套筒式共源共栅结构,通过分析决定开环直流增益、单位增益带宽、转换速 率和建立时间等主要性能参数的各种因素,实现了一款性能优良的全差分运算放大器。Spectre 仿真表明,运算放大器的各项性能指标均达到设计要求,可应用于高精度音频Σ-Δ A/D 转换 器中。

-

共源共栅放大器的特点是什么2024-09-27 2539

-

共源共栅放大器电路图分享2024-02-19 9157

-

折叠共源共栅运算放大器的设计2022-07-08 1331

-

请问怎么设计一种单级全差分增益增强的折叠共源共栅运算放大器?2021-04-20 3247

-

求一种低电压全差分套筒式运算放大器的设计方法2021-04-14 1715

-

500MHz单位增益带宽的OPA656运算放大器2020-10-26 2495

-

ADC低电压高增益运算放大器VLSI设计2013-09-25 1093

-

一种高单位增益带宽CMOS全差分运算放大器2011-07-31 1697

-

增益增强共源共栅放大器的设计2011-06-29 12573

-

一种高增益CMOS全差分运算放大器的设计2010-07-29 659

-

一种低压低功耗CMOS折叠-共源共栅运算放大器的设计2009-12-14 1471

-

高增益带宽运算放大器2009-09-28 2665

全部0条评论

快来发表一下你的评论吧 !