半导体制造的键合线检测解决方案

描述

引线键合广泛应用于电子设备、半导体行业和微电子领域。它实现了集成电路(IC)中芯片与其他电子元件(如晶体管和电阻)之间的互连。引线键合通过在芯片的焊盘与封装基板或其他芯片上的对应焊盘之间建立电气连接。随着需求的不断增加,测试引线键合的重要性也在上升。这些连接在将半导体芯片与封装引脚或基板连接中至关重要。任何在这些键合中出现的缺陷都可能导致开路或短路等问题,显著影响设备功能。因此,测试引线键合不仅是为了确保可靠性和降低生产成本,还为了确保符合行业标准。

以下是一些影响引线键合的常见缺陷:

引线下垂:当引线在拉力下伸展或下垂时,导致接触不良和电气性能下降。

引线偏移:指引线在键合过程中横向移动,导致错位和不可靠的连接。

环形形成:多余的引线可能导致环形形成,影响键合质量和设备功能。

引线短路:这是一个关键缺陷,两个引线意外电接触,可能导致电路故障或设备完全失效。

引线断开:指本应与焊盘电连接的引线断开,造成开路,影响设备功能。

是德科技(Keysight Technologies,Inc.)推出电气结构测试仪(EST),这是一款用于半导体制造的键合线 (Wire Bonding) 检测解决方案,确保电子组件的完整性和可靠性。

Keysight的电气结构测试仪是一种基于电容的测试解决方案,旨在精确识别线键合缺陷。通过利用先进的平均测试(PAT)分析,该测试仪从已知的良好单元建立基线,快速检测出诸如近短路、杂散线、线扫和线下垂等偏差。此功能确保了强大的产品质量管理,并显著提升了制造效率。

电气结构测试仪利用金属表面之间的耦合特性,如引线键合和金属板(也称为IC上方的传感器板)。该测试有效地将IC的每个引脚和引线键合转化为电容器的导电板。这可以检测到以前传统的方法无法发现的缺陷,例如引线和内部引脚之间的“近短路”,以及垂直下垂的引线。此外,电容测试还可以识别诸如错误芯片和模具化合物等问题。

是德科技电气结构测试仪(EST)

EST的主要特点包括:

先进的缺陷检测:

通过分析电容耦合模式的变化,识别各种电气和非电气键合线 (Wire Bonding) 缺陷,确保电子组件的功能和可靠性。

大批量生产准备:

通过同时测试多达20个集成电路,每小时产量高达72,000单位,在大批量生产环境中提升生产力和效率。

大数据分析集成:

通过临界不良重测 (Marginal Retry Test/MaRT)、动态零件平均测试(Dynamic Part Averaging Test/ DPAT)和实时零件平均测试(Real-time Part Averaging Test/RPAT)等先进算法捕捉缺陷并提高产量。

电容测试的原理

使用电容耦合方法进行引线键合缺陷检测的理论相对简单。该方法通过共享的电场在两个导体之间转移电能,而不是通过直接的电连接。这使得未通过电线物理连接的组件之间可以进行通信或信号传输。

在引线键合测试中,可以通过测量两个导电表面之间的电容来应用这一概念:一是位于引线键合区域上方的电容结构,另一是与引线键合相关的导电路径。通过分析导电表面的电容响应,可以评估封装IC中引线键合的状态和位置。

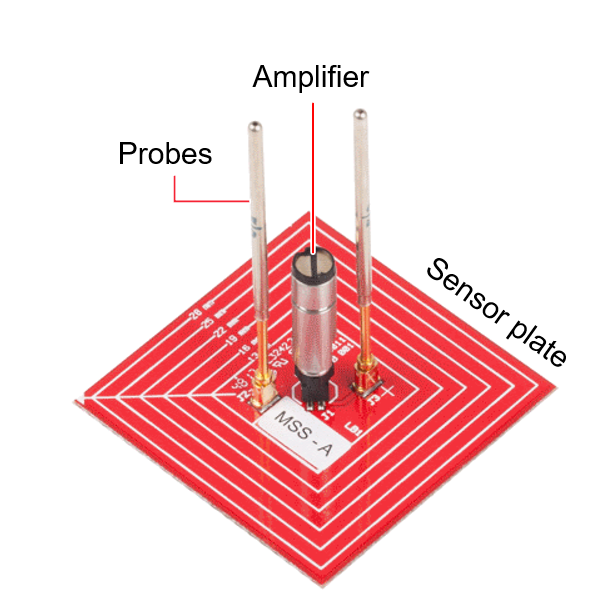

如图1所示,Vectorless Test Enhanced Probe(VTEP)是可以进行此类测试的一个例子。该探头采用先进的电容和电感传感技术,检测和测量印刷电路板(PCB)上组件和互连的电气特性。与传统测试方法需要详细的输入输出向量不同,该技术可以不依赖这些向量,并提供出色的信噪比特性。

图1:Keysight的无矢量测试增强探针(VTEP)

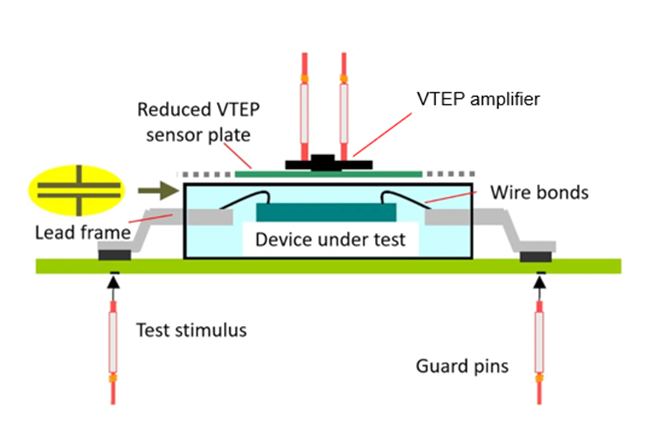

如下图2所示,该解决方案利用先进的电容和电感传感技术来检测和测量引线键合的电容值。该过程涉及通过保护针将刺激信号注入引线框架,然后传递到引线键合。当放大器接触到传感器板(在这种情况下为电容结构)时,电路完成并捕获耦合响应。

图2:使用VTEP进行的四方扁平封装(QFP)引线键合测试设置的横截面图

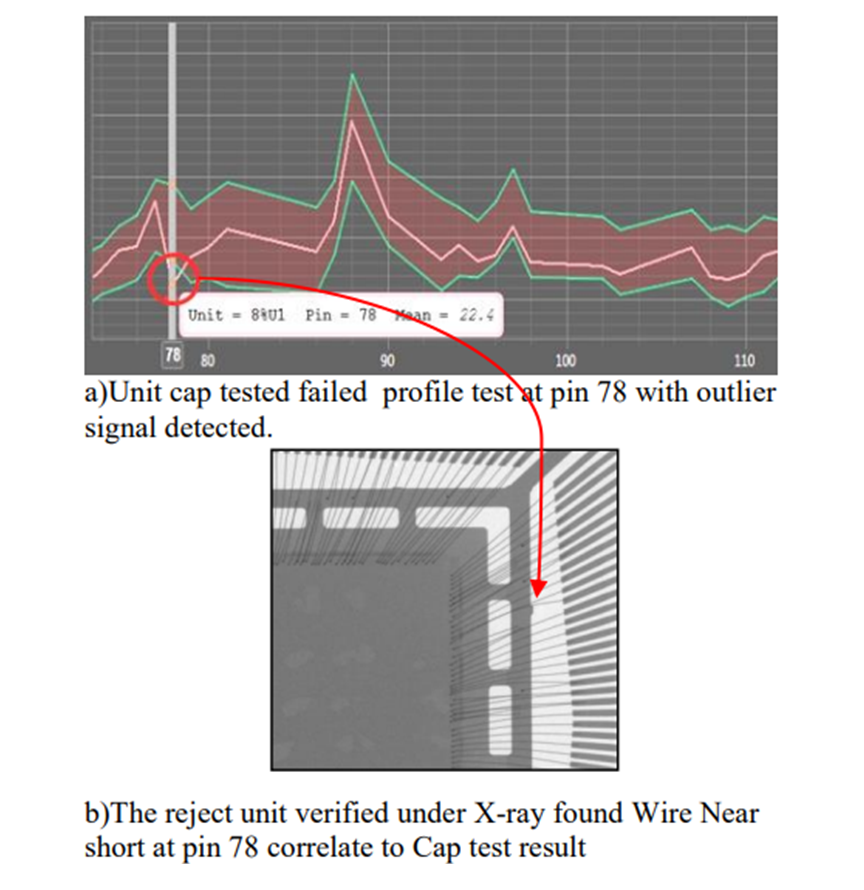

通过这种方法,电气结构测试仪(EST)利用先进的电容和电感传感技术以及部件平均测试(PAT)统计算法,从一组已知良品中学习基线引线键合测试。这使得用户能够将任何引线键合的偏差捕捉为异常值,例如下图3中测试仪捕获的近短缺陷。

图3:“近短路”缺陷,通过s8050 EST检测到,并在X光下验证

电容测试方法特别适用于外围引脚排列的封装,因为这些引脚位于同一侧或围绕集成电路(IC)的位置。常见的例子包括双列直插封装(DIP)和四方扁平封装(QFP)。在这些封装中,所有引脚紧邻排列,形成单层引线键合,便于测量电容耦合信号以确定引线键合的物理位置。

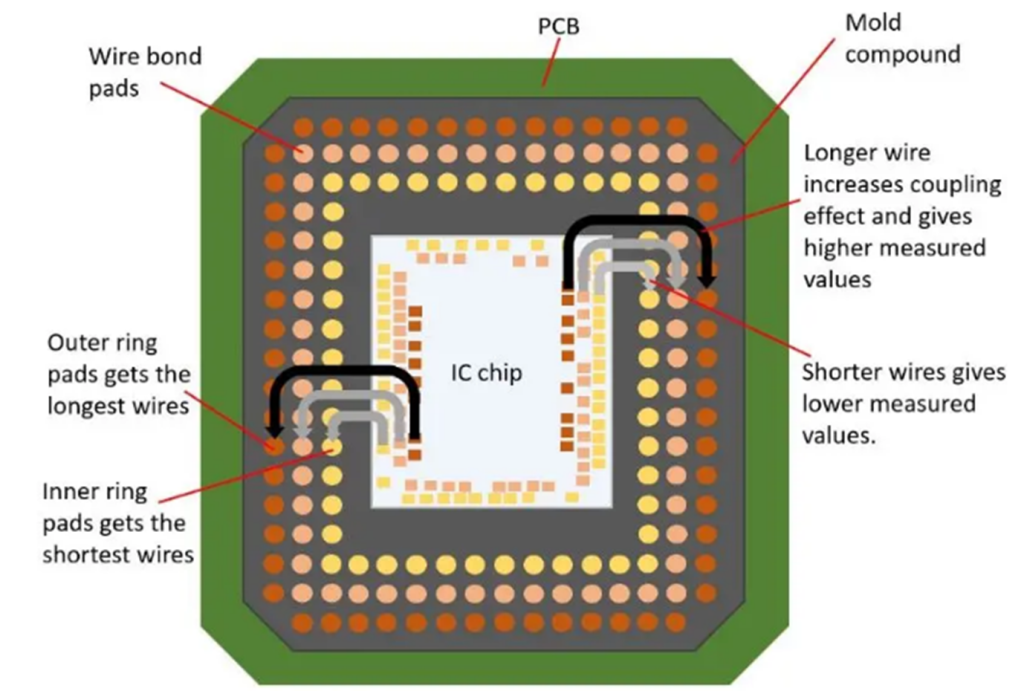

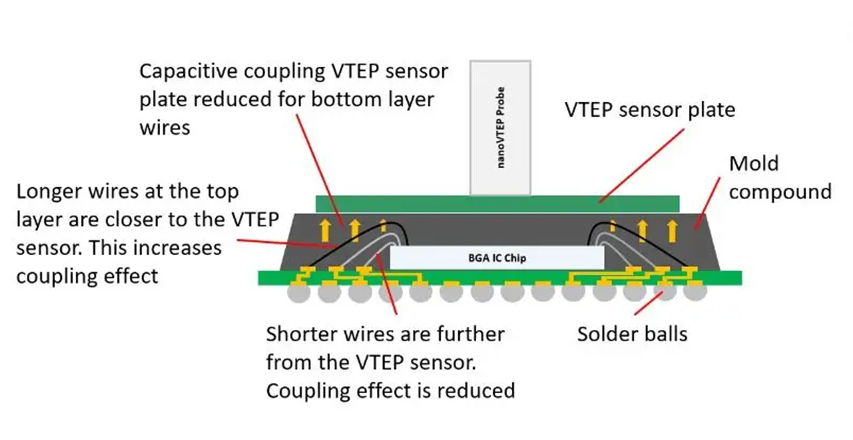

然而,随着技术进步和集成电路复杂性的增加,更先进的封装类型也随之出现,例如球栅阵列(BGA),涉及多层引线键合堆叠。这种高级方法在测量电容耦合信号时面临额外挑战,因为引线键合的排列更为复杂。

图4:BGA封装的俯视图

电容耦合方法可能不适用于这些高级集成电路封装类型。例如,BGA将其引线键合焊盘安排在芯片周围和印刷电路板(PCB)上的同心环中,导致多个重叠的引线层。这种配置使得测量电容耦合信号变得更加困难,因为它会影响信号的强度和信噪比,如图5所示。

图5:BGA封装的横截面视图,其中多个引线重叠在一起

因此,在选择电容耦合测试方法之前,考虑引线的排列非常重要。对于具有复杂引线键合排列的先进封装类型,可能需要采用替代测试方法,以确保准确的测量和可靠的缺陷检测。

转变微电子领域的引线键合缺陷筛选

引线键合在微电子领域至关重要,随着市场增长预期飙升,对高效测试方法的需求比以往任何时候都更为迫切。传统的AXI和ATE系统虽然提供了有价值的见解,但也存在重大局限性。ATE系统可以轻松检测开路、短路和缺失引线等电气缺陷,但无法发现额外或漂浮引线、近短路下垂或扫动引线等问题。而AXI可以检测所有引线键合缺陷,但需要人工视觉检查,劳动力密集且容易出错。

是德科技基于电容的测试解决了这两个挑战。这种先进技术能够检测传统ATE和X射线系统无法发现的缺陷,包括引线之间的“近短路”和垂直下垂的引线。此外,它还可以识别不正确的芯片和模具化合物,扩展了其诊断能力。通过与PAT统计分析相结合,此测试方案可以轻松以高测试通量检测电气和非电气缺陷,并适应高生产节拍率。

关于是德科技

是德科技(NYSE:KEYS)启迪并赋能创新者,助力他们将改变世界的技术带入生活。作为一家标准普尔 500 指数公司,我们提供先进的设计、仿真和测试解决方案,旨在帮助工程师在整个产品生命周期中更快地完成开发和部署,同时控制好风险。我们的客户遍及全球通信、工业自动化、航空航天与国防、汽车、半导体和通用电子等市场。我们与客户携手,加速创新,创造一个安全互联的世界。

-

半导体晶片键合的对准方法2022-04-26 4719

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1792

-

半导体引线键合清洗工艺方案2010-04-22 19527

-

想了解半导体制造相关知识2012-02-12 6670

-

《半导体制造工艺》学习笔记2012-08-20 67996

-

半导体制造2012-07-11 5182

-

半导体制造技术经典教程(英文版)2014-03-06 26547

-

中国半导体FAB制造线总况简说2016-12-22 3893

-

半导体制程2018-11-08 5554

-

半导体制造的难点汇总2020-09-02 4931

-

半导体制造车间的环境与生产要求以及设施规划2020-09-24 8645

-

半导体芯片键合装备综述2024-06-27 3624

-

半导体制造行业MES系统解决方案2024-12-10 1919

-

德州仪器:铜键合线在半导体封装中的应用变革2026-01-18 1301

全部0条评论

快来发表一下你的评论吧 !