了解CPU vs FPGA处理技术的好处和得失来进行图像处理

电子说

描述

机器视觉在工业自动化系统中的应用已经有一定的历史,它取代了传统的人工检查,提高了生产质量和产量。 我们已经看到了相机在计算机、移动设备和汽车等日常生活设备中的迅速普及,但是机器视觉的最大进步莫过于处理能力。随着处理器的性能以每两年翻一番的速度不断提升,以及多核CPU和FPGA等并行处理技术日益受到关注,视觉系统设计人员现在可以应用复杂的算法来可视化数据,并创建出更加智能的系统。

性能的提高意味着设计人员可以获得更高的数据吞吐量,从而实现更快速的图像采集,使用更高分辨率的传感器,并充分利用市场上具有最高动态范围的一些新款相机。性能的提高不仅可让设计人员更快速地采集图像,而且还能更快速地处理图像。预处理算法(如阈值和滤波)或处理算法(如模式匹配)也可以更快速地执行。最终设计人员能够比以往更快地基于可视化数据制定决策。

德州奥斯汀NI总部数据采集和控制产品市场经理,主要负责机器视觉领域的Brandon Treece认为,随着视觉系统越来越多地集成最新一代多核CPU和强大FPGA,视觉系统设计人员需要了解使用这些处理元件的好处和得失。他们不仅需要在正确的硬件上运行正确的算法,还需要了解哪些架构最适合作为其设计的基础。

内联处理和协处理

在研究哪种类型的算法最适合哪个处理元件之前,您应该了解每个应用最适合的架构类型。在开发基于CPU和FPGA的异构架构的视觉系统时,需要考虑两个主要的使用情况: 嵌入式处理和协处理。

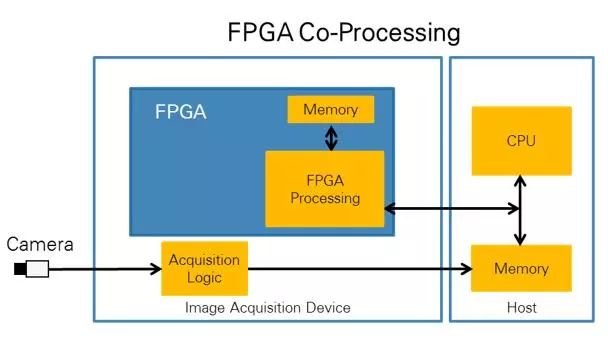

如果是FPGA协处理,FPGA和CPU将共同工作,共享处理负载。这种架构最常用于GigE Vision和USB3 Vision相机,因为它们的采集逻辑最好是在CPU上实现:

您可以使用CPU采集图像,然后通过直接存储器访问(DMA)将其发送到FPGA,以便FPGA可以执行诸如滤波或颜色平面提取等操作。然后,您可以将图像发送回CPU以进行更高级的操作,例如光学字符识别(OCR)或模式匹配。

在某些情况下,您可以在FPGA上实现所有的处理步骤,并只将处理结果发送回CPU。这使得CPU可以将更多的资源用于运动控制、网络通信和图像显示等其他操作。

图1.在FPGA协处理中,图像使用CPU进行采集后,通过DMA发送到FPGA,然后由FPGA对图像进行处理。

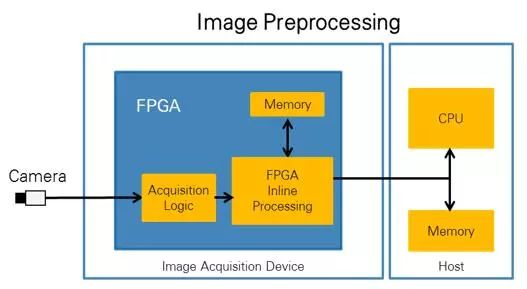

在嵌入式FPGA处理架构中,您可以将相机接口直接连接到FPGA的引脚,以便像素可直接从相机发送到FPGA。这种架构通常与Camera Link相机一起使用,因为它们的采集逻辑易于使用FPGA上的数字电路来实现。 这个架构有两个主要的好处:

首先,与协处理一样,在FPGA上执行预处理功能时,可以使用嵌入式处理将部分工作从CPU转移到FPGA。例如,在将像素发送到CPU之前,可以在FPGA上执行高速预处理,如滤波或阈值处理。这也减少了CPU必须处理的数据量,因为CPU上的逻辑只需捕获感兴趣区域的像素,这最终提高了整个系统的吞吐量。

这种架构的第二个好处是可以在不使用CPU的情况下直接在FPGA内进行高速控制操作。FPGA是控制应用的理想选择,因为它们可以提供非常快速且高度确定的循环速率。其中一个例子就是高速分类,其中FPGA向执行器发送脉冲,当脉冲通过执行器时,执行器会对零件进行剔除或分类操作。

图2.在嵌入式FPGA处理架构中,您可以将相机接口直接连接到FPGA的引脚,以便像素可直接从相机发送到FPGA。

CPU与FPGA视觉算法

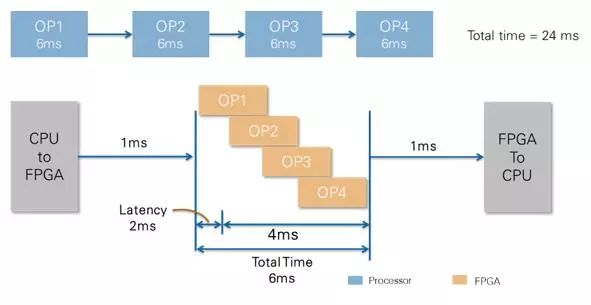

在对构建异构视觉系统的不同方式有了基本了解,您可以看一下在FPGA上运行的最佳算法。 首先需要了解CPU和FPGA的工作原理。 为了解释这一概念,我们假设一个理论算法可对图像执行四个不同的操作,然后看一下这四个操作部署到CPU和FPGA上时分别是如何运行的:

CPU按顺序执行操作,因此第一个操作必须在整个图像上运行结束后,第二个操作才能启动。在本例中,假设算法中的每个步骤在CPU上运行需要6ms; 因此,总处理时间是24ms。

现在考虑在FPGA上运行相同的算法。由于FPGA本质上是大规模并行的,所以该算法中的四个操作可以同时对图像中的不同像素上操作。这意味着接收第一个处理的像素仅需2ms的时间,处理整个图像需要4ms的时间,因而总处理时间为6ms。这比CPU的执行速度快得多。

即使使用FPGA协处理架构并将图像传输到CPU,整个处理时间(包括传输时间)也比单独使用CPU要短得多。

图3.由于FPGA在本质上是大规模并行的,因此相比CPU,可显着性能提升。

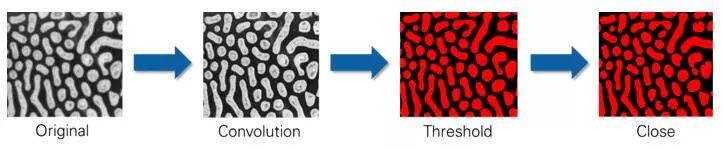

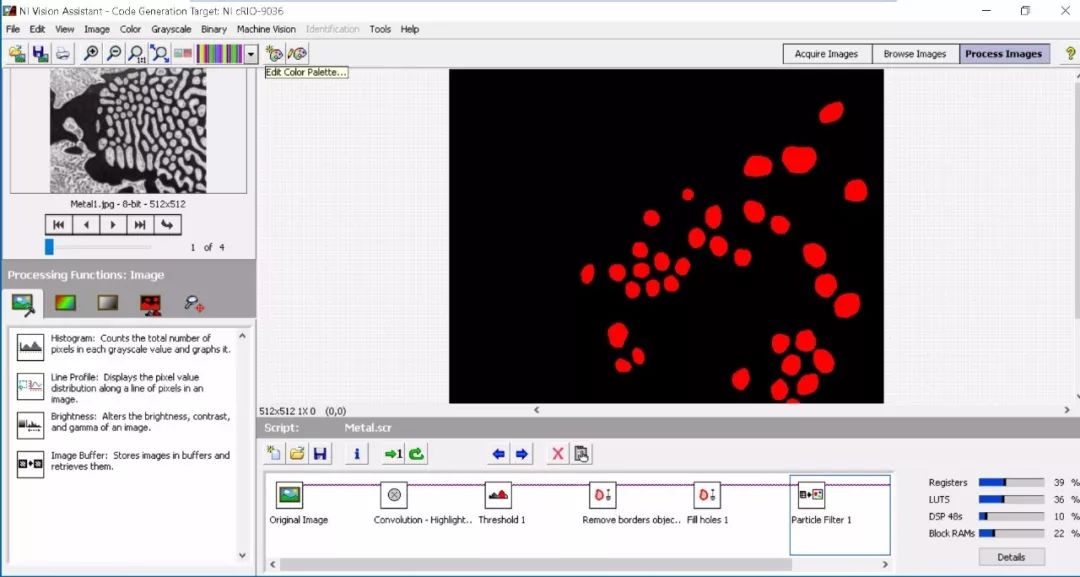

现在考虑一个真实的例子,比如粒子计数所需的图像。

首先需要应用卷积滤镜来锐化图像。

接下来,通过阈值运行图像以生成二进制图像。这不仅可以通过将其从8位单色转换为二进制来减少图像中的数据量,还可以为二进制形态学应用准备图像。

最后一步是使用形态学来应用关闭功能。 这会去除二进制粒子中的任何孔。

如果仅在CPU上执行上述算法,则必须在阈值步骤开始之前完成整个图像的卷积步骤。使用NI公司面向LabVIEW的视觉开发模块(Vision Development Module)和基于Xilinx Zynq-7020全可编程SoC的cRIO-9068 CompactRIO控制器时,执行上述算法需要的时间为166.7ms。

但是,如果在FPGA上运行相同的算法,则可以并行执行每个步骤。在FPGA上运行相同的算法只需8ms即可完成。请记住,8ms的时间中包括将图像从CPU发送到FPGA的DMA传输时间,以及算法完成的时间。在某些应用中,可能需要将处理后的图像发回到CPU,以供应用中的其他部分使用。如果加上这个时间的话,整个过程也只需8.5ms。总的来说,FPGA执行这个算法要比CPU快20倍。

图4:使用FPGA协同处理架构运行视觉算法,性能比仅用CPU运行同样的算法提高了20倍。

那么,为什么不在FPGA上运行每个算法呢?

尽管FPGA比CPU更有益于视觉处理,但是要享受这些优势也要做出一定的权衡。例如,考虑CPU与FPGA的原始时钟频率。FPGA的时钟频率在100~200MHz数量级。很显然,FPGA的时钟频率低于CPU的时钟频率,CPU可以轻松地在3GHz或更高的频率下运行。因此,如果一个应用需要一种必须迭代运行的图像处理算法,并且不能利用FPGA的并行性,那么CPU能够更快地进行处理。

前面讨论的示例算法在FPGA上运行可以获得20倍的速度提升。该算法中的每个处理步骤同时对各个像素或一组像素进行操作,因此该算法可以利用FPGA的并行优势来处理图像。 然而,如果算法使用诸如模式匹配和OCR这样的处理步骤,这些要求立即分析整个图像,这时候FPGA的优势就比较勉强了。这是由于缺少处理步骤的并行化,以及需要大量内存进行图像与模板之间的比对分析。虽然FPGA可以直接访问内部和外部存储器,但通常情况下,FPGA可用的存储器数量远不及CPU可用的数量,或是这些处理操作所需的数量。

克服编程复杂性

FPGA用于图像处理的优势,取决于每种应用要求,包括应用的特定算法、延迟或抖动要求、I/O同步和功耗等因素。通常使用具有FPGA和CPU的架构,能充分利用FPGA和CPU各自的优势,并且在性能、成本和可靠性方面都具有竞争优势。然而,实现基于FPGA的视觉系统面临的最大挑战之一是克服FPGA的编程复杂性。视觉算法开发本质上是一个迭代过程。完成任何一项任务都必须尝试多种方法。大多数情况下,需要确定的不是哪种方法可行,而是哪种方法最好,而“最好方法”的判定则因应用的不同而不同。例如,对于某些应用而言,速度至关重要;而对于另一些应用,则更看重准确度。至少,需要尝试几种不同的方法才能为特定应用找到最好的方法。

为了实现生产率的最大化,不论使用哪种处理平台,都需要立即获得关于算法的反馈和基准测试信息。当使用迭代探索性方法时,实时查看算法结果将会节省大量时间。什么是正确的阈值?用二进制形态滤波器剔除的颗粒多大或多小? 哪种图像预处理算法和算法参数可以最好地清理图像? 这些都是开发视觉算法时的常见问题,而关键在于是否能够更改并快速查看结果。然而,传统的FPGA开发方法可能会减缓创新,因为算法的每个设计变化之间需要编译时间。克服这一点的一个方法是使用一个算法开发工具,可让您在同一个环境进行CPU和FPGA的开发工作,而不会在FPGA编译时陷入困境。NI Vision Assistant是一种算法工程工具,用于开发部署到CPU或FPGA上的算法,以帮助您简化视觉系统设计。您还可以使用Vision Assistant在目标硬件上编译和运行之前测试算法,同时轻松访问吞吐量和资源利用率信息。

图5. 在具有集成基准测试的FPGA硬件上使用基于配置的工具开发算法,可减少等待代码编译的时间,从而提高了开发速度。

因此在考虑谁更适合进行图像处理时,CPU还是FPGA?答案是“视情况而定”。您需要了解应用的目标,才能使用最适合该设计的处理元件。但是,不管是什么应用,基于CPU或FPGA的架构及其固有的优势都可以将机器视觉应用的性能提升一个等级。

-

FPGA图像处理基础----实现缓存卷积窗口2025-02-07 1464

-

FPGA 实时信号处理应用 FPGA在图像处理中的优势2024-12-02 2417

-

FPGA在图像处理领域的优势有哪些?2024-10-09 9360

-

FPGA设计经验之图像处理2024-06-12 3173

-

FPGA图像处理方法2023-12-02 1796

-

荐读:FPGA设计经验之图像处理2023-06-08 5906

-

什么是深度学习?使用FPGA进行深度学习的好处?2023-02-17 2023

-

FPGA学习-基于FPGA的图像处理2023-02-15 1929

-

如何使用FPGA进行图像实时处理系统的设计2018-10-23 1348

-

CPU vs FPGA?图像处理谁更“应景”?2018-08-03 3260

-

在FPGA上进行图像处理及其示例2017-11-17 19731

-

FPGA图像处理2016-12-14 992

-

张工教你FPGA图像处理技术2014-11-05 2540

-

基于DSP和FPGA的通用图像处理平台设计2010-02-01 1674

全部0条评论

快来发表一下你的评论吧 !