深度解析IO模拟时序(SPI)的注意事项

描述

原则:有硬件I2C、SPI时尽量用硬件操作,省去IO模拟繁琐的时序调试。但在内部资源不够时就要用IO模拟总线了。

关于短延时:

模拟时序时是否需要延时要看MCU与device的相对速度。比如I2C如果400K的速率和MCU动辄几十M的速率不再一个量级,肯定要通过延时调整时序;但对于SPI因为其速度很高,甚至有的比单片机的速度还高,这时就没必要延时了。

关于IO模拟的收发函数是否要合并成一个:

对于SPI因为是全双工,所以可以分开,当然也可以合并成一个(发送时不需要返回值,而接收时此时参数是要发送的数据,返回值是要读的值)

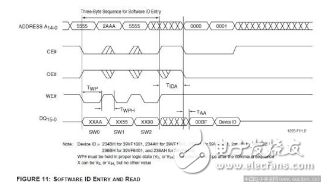

关于在什么跳变沿操作:

比如芯片手册中说到在上升沿采样/锁定(也就是在搞定平之后值必须稳定),那么单个位bit的收发都应该在0->1之间进行操作。

关于时钟极性和时钟相位:

CPOL时钟极性只是说明了空闲时总线的电平状态:CPOL=1表明空闲时时钟是搞定平;否则是低电平。

CPOA时钟相位说明了在第几个跳变沿进行采样,CPOA=0表明在第一个沿进行采样,否则在第二个沿。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

美国Odyssey奥德赛电池充电注意事项全解析2025-05-19 1281

-

ADS8528、ADS8548和ADS8568时序注意事项2024-10-10 650

-

深度剖析 IGBT 栅极驱动注意事项2023-11-24 2011

-

CPU翻转IO口注意事项2023-10-23 707

-

SPI协议如何通过IO口模拟,有哪些注意事项?2023-06-26 726

-

使用注意事项2023-03-17 747

-

低功耗配置IO的注意事项是什么2022-02-11 1102

-

通用IO结构注意事项是什么2021-11-24 951

-

PIC18Fxx单片机IO设置注意事项!2021-11-16 729

-

AVR单片机IO使用注意事项有哪些?2021-10-29 2781

-

PSoC Creator模拟设计:引脚放置的模拟及注意事项2020-07-01 4533

-

请问stm32与DSP的SPI通信有什么注意事项吗?2019-04-17 2695

-

车载信息娱乐系统IO端口和电子模块的电路保护注意事项2017-01-24 1342

-

FPGA设计中的时序分析及异步设计注意事项2009-12-07 3988

全部0条评论

快来发表一下你的评论吧 !