加法器电路设计方案汇总(八款模拟电路设计原理详解)

应用电子电路

描述

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

加法器电路设计方案一:BCD加法器的设计

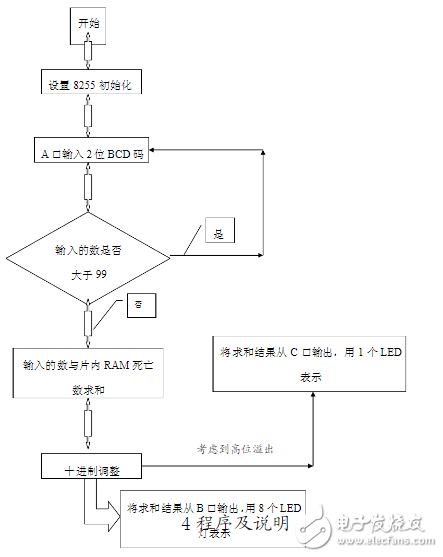

BCD加法器的设计, 目的是根据彩灯亮灭的方式,来显示两个BCD码相加之和。

本设计要求考虑高位溢出,无高位溢出时,求和结果用8个LED灯显示,亮的为1,灭的为0,读出BCD码转化为十进制,即为结果;若有高位溢出时,第9个灯亮,所得结果已超过两位,通过9个灯结合读出结果。

硬件接线图

程序流程图

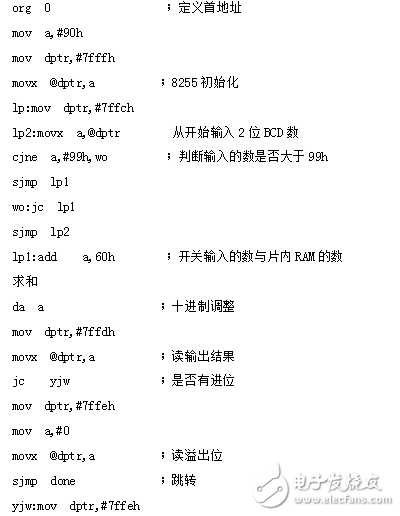

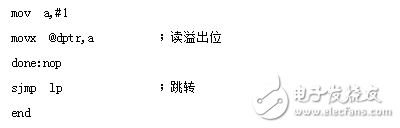

程序设计

加法器电路设计方案二:8位级联加法器的设计

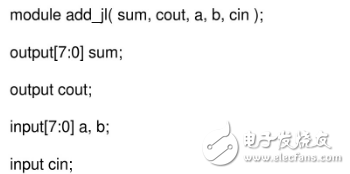

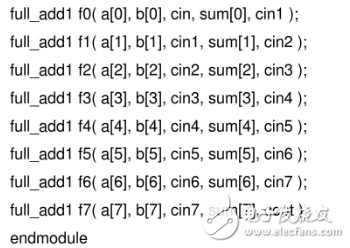

8位级联加法器的设计程序

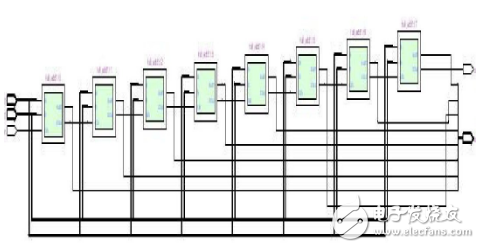

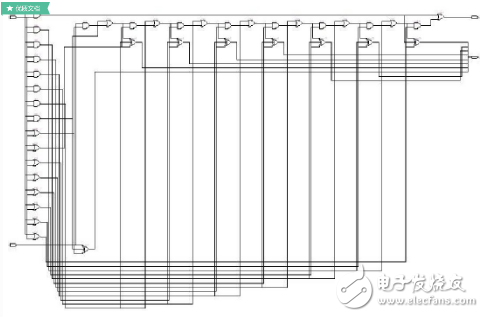

8位级联加法器RTL图

加法器电路设计方案三:八位并行加法器设计

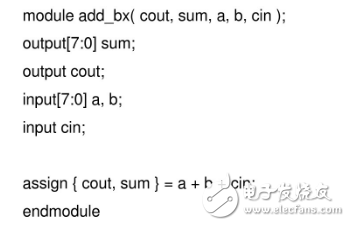

它的结构为用加法运算符描述,由EDA软件综合,其优点是运算速度快。

程序

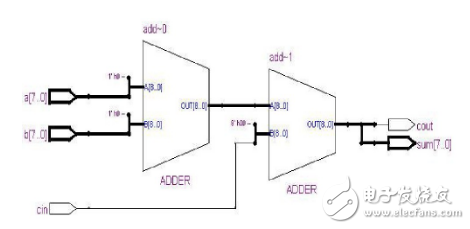

8位并行加法器RTL图

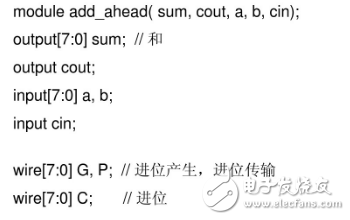

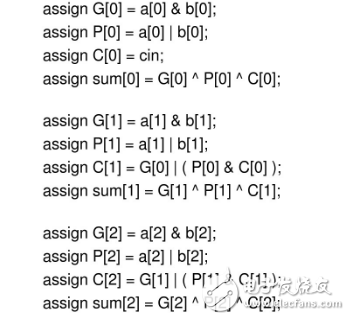

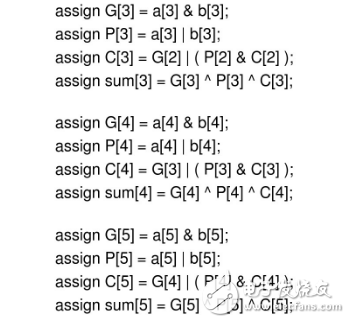

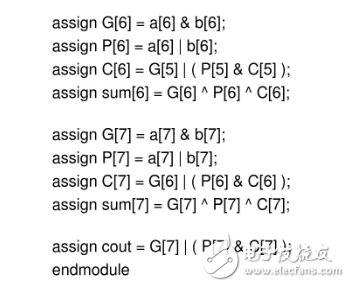

加法器电路设计方案四:八位超前进位加法器设计

程序

八位超前进位加法器RTL图

加法器电路设计方案五:四位串行进位加法器设计

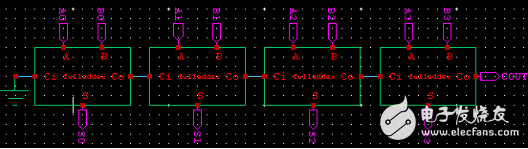

根据四位串行进位加法器的逻辑关系,用S-Edit完成串行进位加法器的电路图以及模块符号图的设计,如图1和图2所示。

图1 四位串行进位加法器电路图

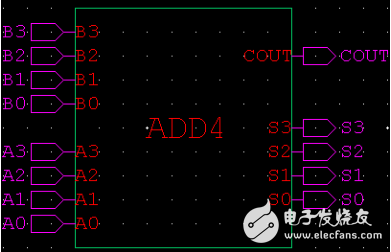

图2 四位串行进位加法器模块符号图

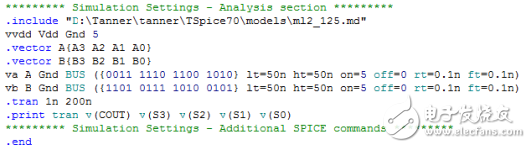

加载SPICE文件

完成四位串行进位加法器的设计,提取设计电路的SPICE 文件,并对SPICE 文件进行文件加载设定,以完成整个电路的仿真。加载包含文件如下图所示。

加载SPICE文件图

仿真

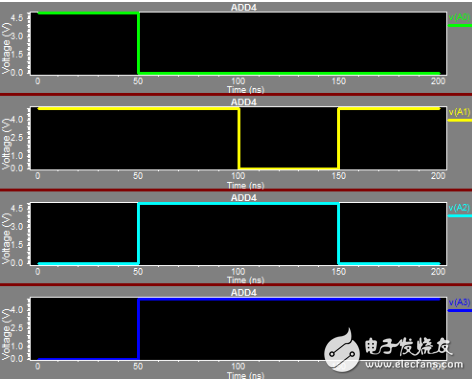

完成加载设定后,对设计电路进行仿真,其仿真结果如图3、图4 所示,图3为输入信号A 设定的电平波形,从上到下依次为A0、Al、A2、示。A3。图4为输入信号B 设定的波形图,从上到下依次为B0、B1、B2、B3。

图3 输入信号A波形图

图4 输入信号B波形图

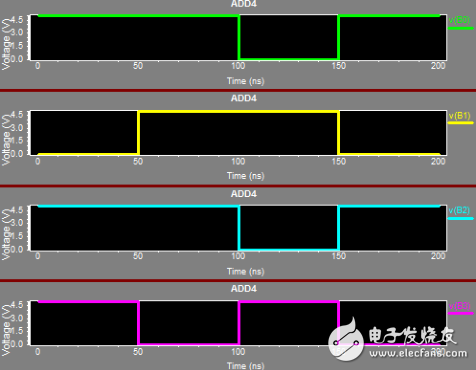

通过对输入信号A、B的设定,通过四位串行进位加法器电路的仿真运算,其仿真结果如图5所示。该图从上至下的信号端依次为SO、S1、S2、S3、COUT.

图5 四位加法器电路仿真波形图

通过上述波形图可知,当t=0-50ns 时,A3A2A1A0=0011,B3B2B1B0=1101,输出和S3S2S1S0=0000,输出进位COUT=1;当t=50-100ns 时,A3A2A1A0=1110,B3B2B1B0=0111,输出和S3S2S1S0=0101,输出进位COUT=1;当t=100-150ns时,A3A2A1A0=1100,B3B2B1B0=1010,输出和S3S2S1S0=0110,输出进位时,输出和COUT=1;当t=150-200ns,A3A2A1A0=1010,B3B2B1B0=0101,S3S2S1S0=111,输出进位COUT=0。通过对仿真波形图的分析,可以看出该仿真结果存在0-10ns 的延时,除此之外均符合四位串行进位加法器的逻辑功能。

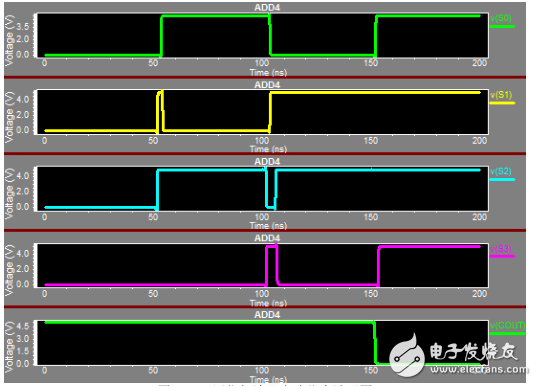

加法器电路设计方案六:反相加法器的电路设计1

下图是由运算放大器构成的反相加法器的电路图

uo=-[ui1*RF/R1+ui2*RF/R2]

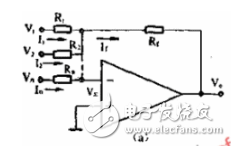

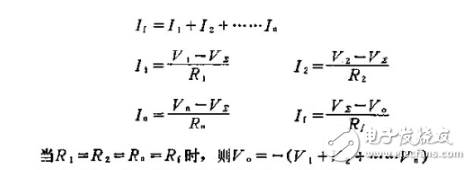

加法器电路设计方案七:反相加法器的电路设计2

下图为一个反相加法器电路

由图可知

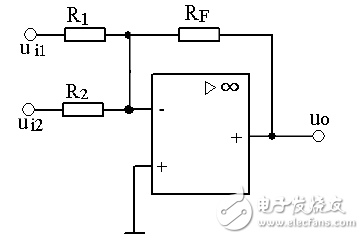

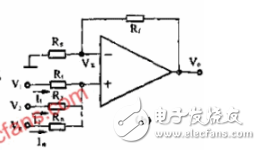

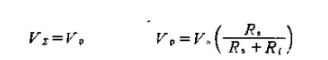

加法器电路设计方案八:同相加法器电路设计

下图为同相加法器电路

从图中可知同向放大器的真正输入信号是外接信号与反馈信号VΣ相串联的,因此可得出

-

同相加法器和反相加法器的区别是什么2024-05-23 5284

-

镜像加法器的电路结构及仿真设计2023-07-07 5179

-

小信号放大电路设计方案汇总2021-09-14 3293

-

电流检测电路设计方案汇总(六款模拟电路设计原理图详解)2018-02-06 330296

-

超温报警器电路设计方案汇总(六款模拟电路设计原理图详解)2018-01-29 36486

-

停电报警器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-28 43287

-

减法器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-17 95091

-

同相加法器电路原理与同相加法器计算2016-09-13 58861

-

加法器,加法器是什么意思2010-03-08 5891

全部0条评论

快来发表一下你的评论吧 !