20进制计数器设计方案汇总(三款仿真电路设计原理详细)

应用电子电路

901人已加入

描述

本文为大家介绍三个20进制计数器设计方案。

20进制计数器设计方案一:基于MAX+PLUSⅡ的20进制计数器设计

创建电路

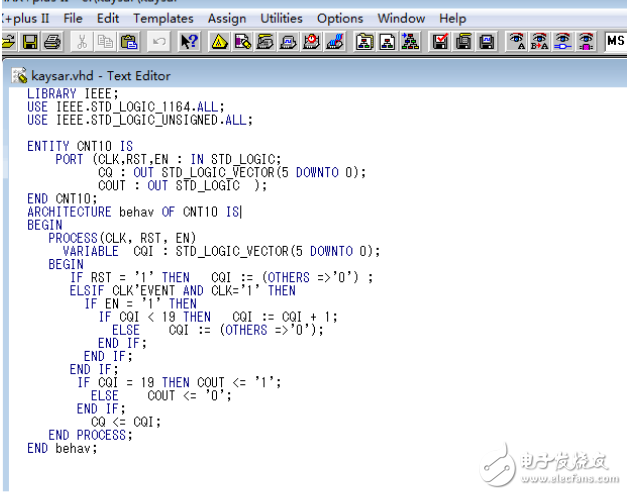

文本图:

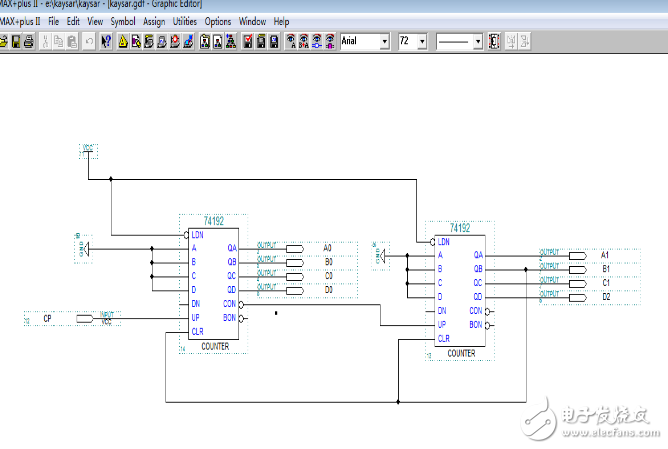

20进制计数器的原理图

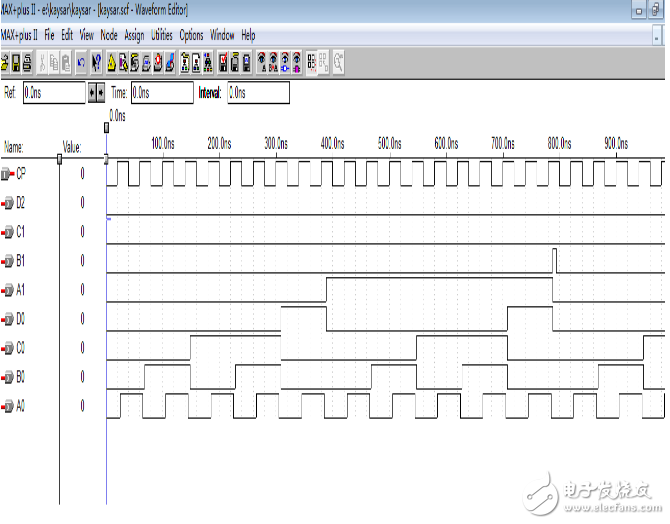

原理图输出波形图

可见当LD信号为“1”是不管CLK信号是什么都不工作。只要LD为“0”是才能正常工作。

功能表

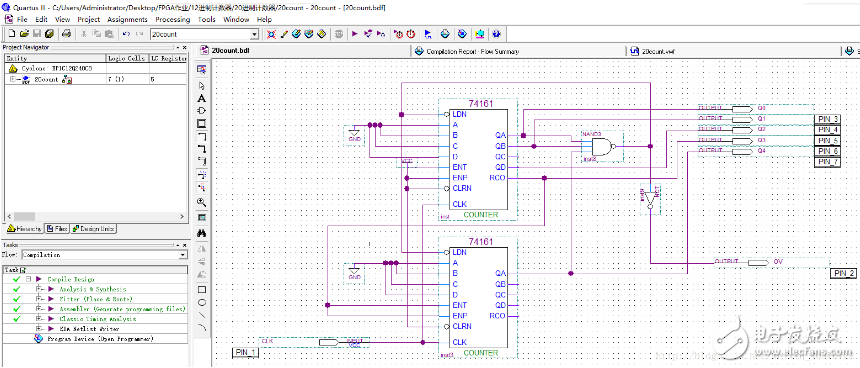

20进制计数器设计方案二:FPGA利用74161设计20进制计数器

1.首先,建立工程,新建BDF文件,在BDF文件中画出电路图,如图所示:

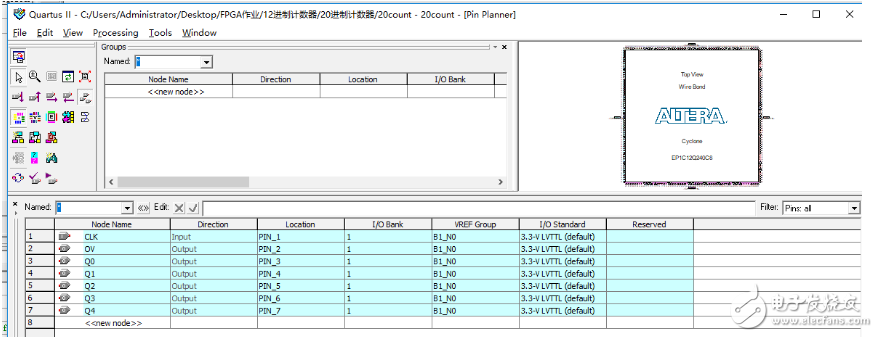

2.由于输入输出数目较少,PIN管脚设置采用手动输入的方法,设置后如图所示:

然后点击startcompilcation进行编译,得到如下结果:

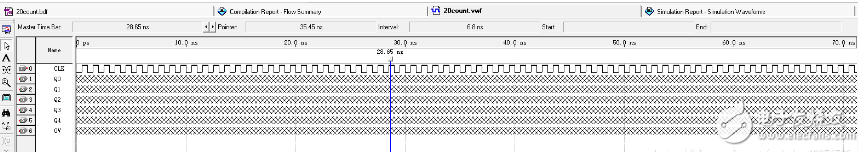

3.最后,进行仿真设计,先新建一个VWF文件,再将nodefinder中的关键引脚拖至仿真区,设置好仿真时间以及输入信号,如图所示:

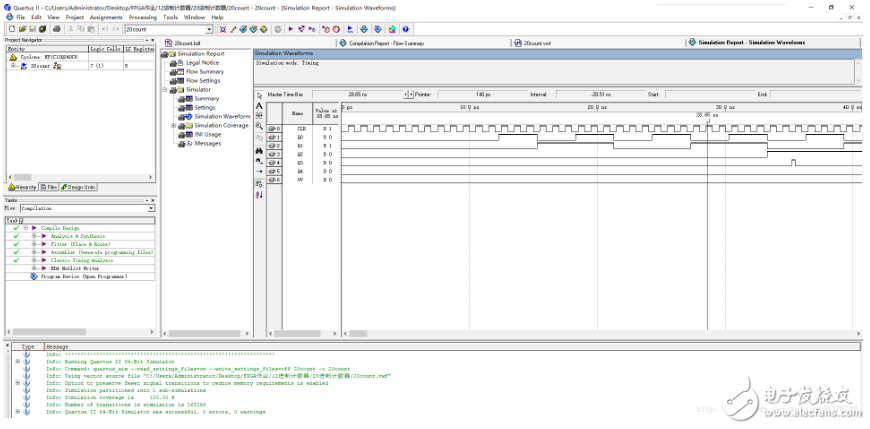

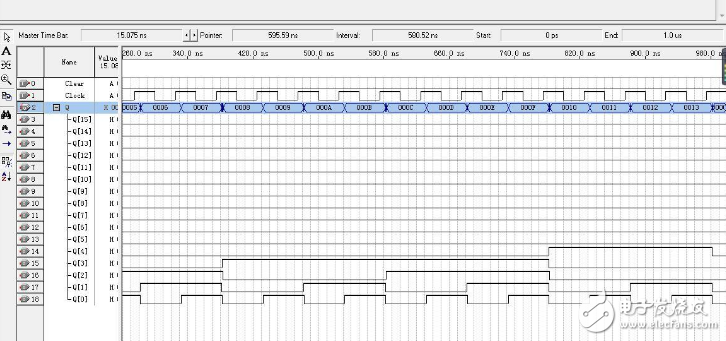

点击startsimliation进行仿真,得到仿真结果如图所示:

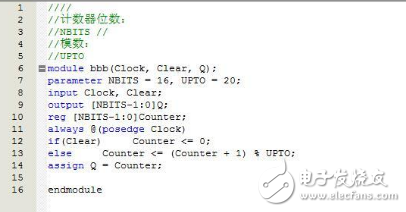

20进制计数器设计方案三:用verilog语言实现的20进制计数器

程序设计

仿真波形

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

计数报警器电路设计方案汇总(多款模拟电路设计原理图详解)2018-01-29 25898

-

N进制异步计数器设计方案2011-10-24 3807

-

基于Proteus的任意进制计数器设计与仿真2016-07-29 1891

-

24进制计数器的设计2017-11-09 4842

-

基于74LS160的N进制计数器仿真设计2017-12-21 68811

-

10进制计数器设计方案汇总(六款电路设计原理及程序分享)2018-01-17 80736

-

2进制计数器设计方案汇总(五款模拟电路设计原理及过程详解)2018-01-17 23091

-

八进制计数器设计方案汇总(四款模拟电路原理实现过程)2018-01-17 99257

-

16进制计数器设计方案汇总(四种电路设计原理图及仿真程序分享)2018-01-17 77796

-

12进制计数器设计方案汇总(五款模拟电路设计原理及程序分享)2018-01-17 77280

-

5进制计数器设计方案汇总(三款计数器的电路原理图)2018-01-17 69362

-

6进制计数器设计方案汇总(三款模拟电路原理图分享)2018-01-17 77038

-

7进制计数器设计方案汇总(三种模拟电路设计过程详细)2018-01-17 60611

-

任意进制计数器设计方案汇总(七款模拟电路设计原理详解)2018-01-17 74869

-

乘法器电路设计方案汇总(五款模拟电路设计原理及仿真程序分享)2018-01-17 59845

全部0条评论

快来发表一下你的评论吧 !