6进制计数器设计方案汇总(三款模拟电路原理图分享)

应用电子电路

901人已加入

描述

本文为大家分享三种6进制计数器设计方案。

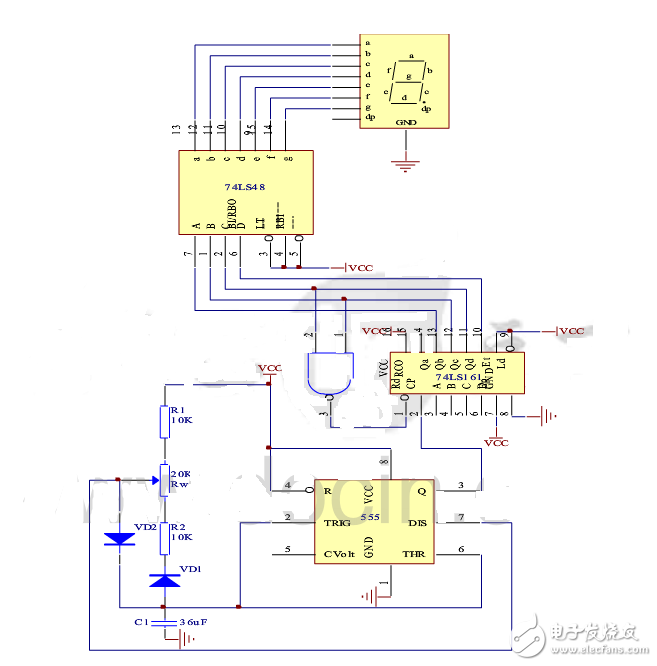

6进制计数器设计方案一:基于74LS161的6进制计数器设计

首先由555 定时器产生1HZ 脉冲信号,将此信号作为74LS161芯片CP 的输入信号,当在CP信号上升沿到来时74LS161芯片就会自动完成加一功能输出0001111这十六个循环状态,这个输出信号再通过74LS48 译码器将这个信号转化为七段数码管的输出显示,但以在74LS161芯片的12、13 脚(输出信号) 1脚(Rd 非) 之间加了一个与非门,当输Rd (非) 就会自动由出的信号到0110 时,变为‘0‘,这时74LS161就完成了清零“1’功能进入下一个循环状态,这样就完成了从0-5 的六进制计数功能。

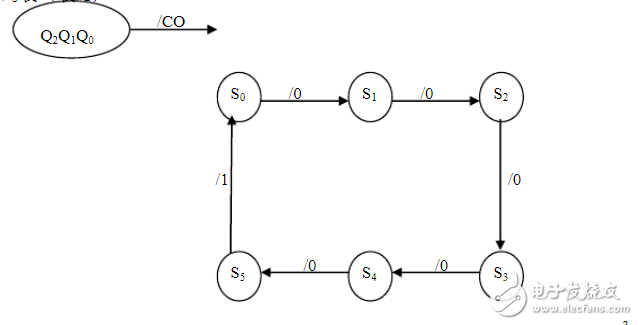

6进制计数器设计方案二:六进制加法计数器设计

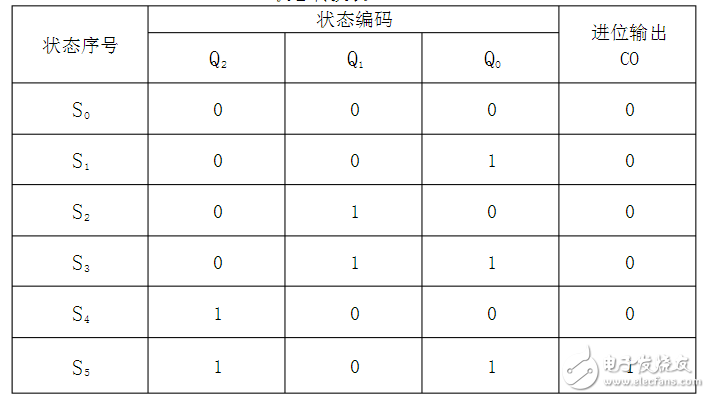

状态编码

状态图

按照习惯,我们取二进制的(000~101)为S0~S5的编码,于是得到下表的状态编码表。

状态转换表

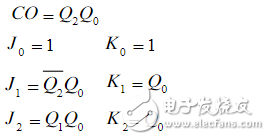

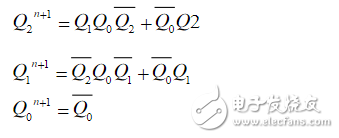

驱动方程

JK触发器的状态方程

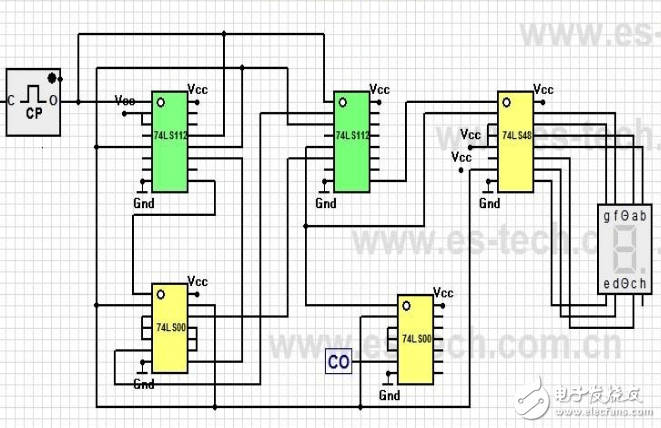

设计原理图

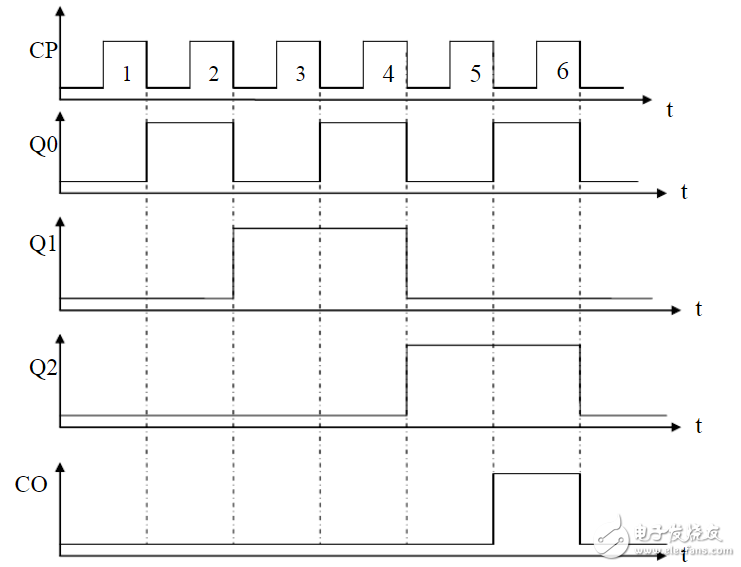

时序图

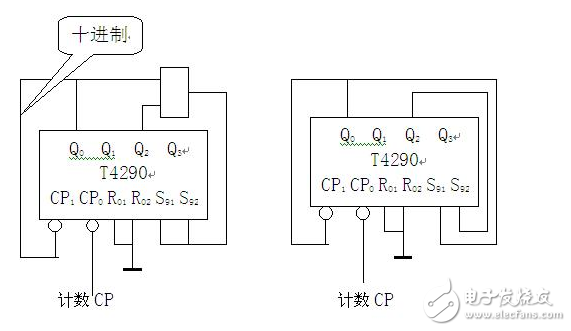

6进制计数器设计方案三:采用T4290用置位法实现6进制计数器

详细电路设计方案:6进制计数器(采用T4290用置位法实现)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- �

-

三路抢答器电路设计方案汇总(三款模拟电路设计原理图详解)2018-01-29 84046

-

100进制计数器2009-06-28 8139

-

N进制异步计数器设计方案2011-10-24 3807

-

模拟脉冲计数器原理图2016-05-11 1086

-

10进制计数器设计方案汇总(六款电路设计原理及程序分享)2018-01-17 80736

-

2进制计数器设计方案汇总(五款模拟电路设计原理及过程详解)2018-01-17 23090

-

八进制计数器设计方案汇总(四款模拟电路原理实现过程)2018-01-17 99257

-

20进制计数器设计方案汇总(三款仿真电路设计原理详细)2018-01-17 13149

-

16进制计数器设计方案汇总(四种电路设计原理图及仿真程序分享)2018-01-17 77796

-

12进制计数器设计方案汇总(五款模拟电路设计原理及程序分享)2018-01-17 77280

-

5进制计数器设计方案汇总(三款计数器的电路原理图)2018-01-17 69362

-

7进制计数器设计方案汇总(三种模拟电路设计过程详细)2018-01-17 60611

-

任意进制计数器设计方案汇总(七款模拟电路设计原理详解)2018-01-17 74869

-

计数报警器电路设计方案汇总(多款模拟电路设计原理图详解)2018-01-29 25898

-

光电转换电路设计方案汇总(三款模拟电路设计原理图详解)2018-02-06 75378

全部0条评论

快来发表一下你的评论吧 !