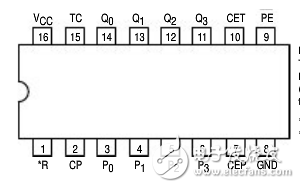

74ls161管脚图引脚图及功能表

芯片引脚图

730人已加入

描述

74ls161管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·Q1·Q2·Q3·CET)

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。74LS161还有一个进位输出端CO,其逻辑关系是CO=Q0·Q1·Q2·Q3·CET。合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 74LS161

-

74ls161引脚图及功能介绍2021-07-08 234819

-

74ls161商品批发价格 74ls161引脚图与管脚功能测试2021-06-08 11563

-

使用74LS161设计数字时钟的原理图免费下载2019-06-05 5222

-

74ls107引脚图及功能表详解2018-05-29 47364

-

74ls153管脚及功能表_真值表逻辑图及应用电路2018-01-26 613571

-

74ls161制作24进制计数器设计2018-01-16 129360

-

74ls161中文资料_74ls161计数器功能及其应用2018-01-02 563466

-

74ls1612013-05-20 5516

-

十进制可逆计数器74LS192引脚图管脚及功能表2011-05-19 132385

-

74ls92引脚图及功能表2008-12-01 26140

-

74ls190引脚图管脚图及功能表2008-08-06 117298

-

74LS161计数器及显示应用电路图2007-12-02 16115

-

二进制同步计数器74LS161引脚图及功能表(管脚图)2007-11-22 60343

-

74ls74芯片引脚图及管脚功能2007-11-19 72918

全部0条评论

快来发表一下你的评论吧 !