计数器74LS161的Multisim仿真

IC应用电路图

描述

74LS161是具有异步置零、计数、预置数和保持功能的可编程集成中规模同步4位二进制加法计数器。

用Muhisim仿真软件虚拟仪器中的字组产生器做信号源产生所需的时钟脉冲、控制信号,用逻辑分析仪显示时钟脉冲、控制信号及状态输出信号的波形,通过仿真实验可直观描述计数器的工作过程。

1、Multisim仿真实验方法

Muhisim仿真实验方法如下:

(1)创建电路

确定字组产生器产生74LS161计数器所需的时钟脉冲、控制信号,逻辑分析仪所显示的时钟脉冲、控制信号及状态输出信号。

74LS161计数器可从Muhisim的TTL数字IC库中找出,字组产生器、逻辑分析仪分别从虚拟仪器库中找出。

(2)设置字组产生器

确定字组产生器产生的74LS161计数器所需的时钟脉冲、控制信号等各个字的内容,在字组产生器中依次输入各字组数据,进行所有字组信号的设置。

(3)仿真运行分析

进行实验仿真,分析仿真实验结果。

2、Multisim仿真实验举例

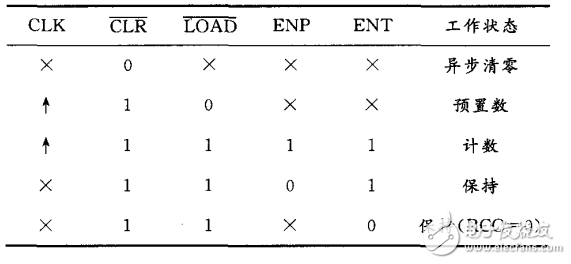

74LS161计数器的功能表如表1所示,其中CLK为时钟脉冲输入信号、ENP及ENT为计数控制信号、L0AD为预置数控制信号、CLR为异步置零控制信号、ABCD为预置数输入信号、QAQBQCQD为状态输出信号、RCO为进位输出信号。

2.1、仿真实验电路创建

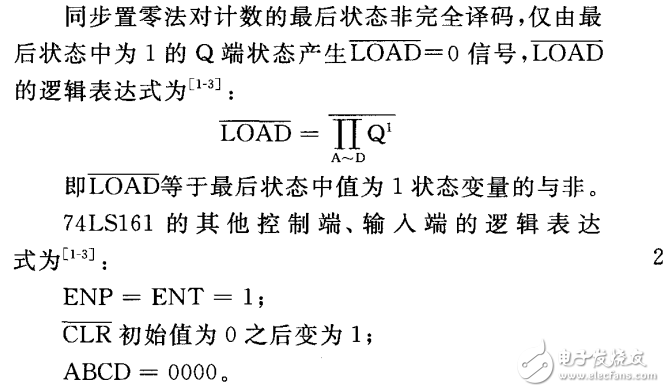

实验时附加与非门将计数器74LS161用同步置零法构成计数范围为0000~1001的十进制计数器,并用CIR异步置零信号将计数器置于0000初始状态,计数器工作时所用到的工作方式有异步清零、二进制计数和预置数,全面反映了计数器的工作过程。

表174LS161的功能表

构建仿真实验电路如图1所示。其中,字组产生器输出时钟脉冲CLK、异步置0信号CLR,逻辑分析仪显示时钟脉冲/CLK、异步置0信号/CLR、预置数控制信号/LOAD及状态输出信号QA~QD的波形。

图1 集成计数器74LS161的仿真实验电路

注意,Multisim10版本中,74LS161的时钟脉冲CLK为下降沿触发,附加反相器74LS04修正为与实际器件一致的上升沿触发方式。

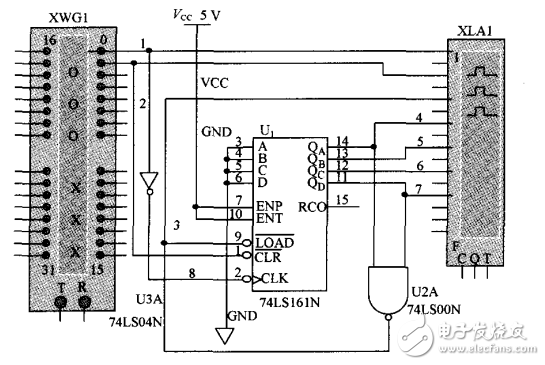

2.2、字组产生器输出字组的设计

所设计的各字数据为0,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,如图2所示。

在字组产生器的数据栏内以十六进制(Hex)依次输入各字组数据,并对最后一个字数据进行末地址设置(SetFinalPosition),完成所有字组信号的设置,如图3所示。

图3 集成计数器74LS161仿真实验字组信号的设置

2.3、仿真运行分析

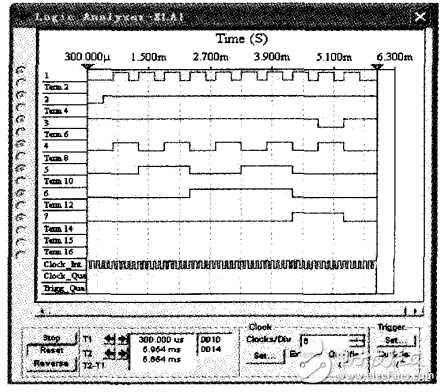

逻辑仪分析显示波形如图4所示。

图4 集成计数器74LS161仿真实验波形

图4中,“1”为时钟脉冲/CLK的波形;“2”为异步置0信号/CLR的波形;“3”为预置数控制信号/LOAD的波形;“4”~“7”为状态输出信号QA~QD的波形。

由图4可知,/CLR一0时将计数器置于0000初始状态;/CLR=1时,从0000~1001状态,预置数控制信号/LOAD=1,计数器在时钟脉冲/CLK作用下按计数方式工作;在1001状态预置数控制信号/LOAD一0,计数器在时钟脉冲/CLK作用下按预置数方式工作,使QAQBQcQD—ABCD一0000。

3、结语

由于受实验仪器的限制无法对计数器工作波形进行硬件实验验证,主要是,现有的信号发生器不能产生多路同步信号,现有的示波器多为双踪示波器无法同时观测多路波形,用Multisim软件仿真解决了这一问题,所述方法具有实际应用意义。

-

74ls161引脚图及功能介绍2021-07-08 234761

-

74ls160和74ls161区别2018-05-08 127762

-

74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)2018-01-18 498644

-

基于74LS161的扭环形计数器自启动设计2018-01-17 43802

-

74ls161制作24进制计数器设计2018-01-16 129326

-

74ls161中文资料_74ls161计数器功能及其应用2018-01-02 563440

-

基于Multisim的计数器设计仿真2013-07-26 3963

-

求74ls161十进制减计数器接法2013-05-22 8886

-

74ls1612013-05-20 5515

-

基于可编程计数器74LS161的循环码计数器设计2012-02-29 4771

-

74LS161异步置零法构成任意进制计数器的Multisim仿真2011-08-05 10548

-

74LS161构成的五十(50)进制计数器电路图-原理图2009-03-28 37694

-

74LS161计数器及显示应用电路图2007-12-02 16109

-

二进制同步计数器74LS161引脚图及功能表(管脚图)2007-11-22 60329

全部0条评论

快来发表一下你的评论吧 !