除法运算电路设计方案汇总(九款模拟电路设计原理详解)

应用电子电路

描述

本文为大家带来九款不同的除法运算电路设计方案,包括这九款模拟电路设计的原理及设计过程。

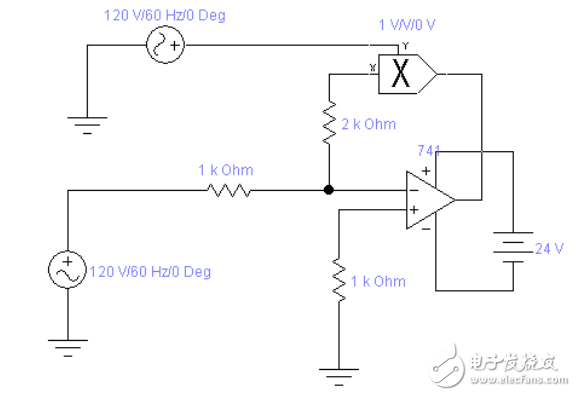

除法运算电路设计方案一:基于模拟乘法器的除法运算电路设计

该方案采用模拟乘法器做反馈支路,模拟乘法器有两个输入端,一个输出端。对于该除法运算电路,必须保证i1=i2,电路引入的才是负反馈。即当UI1》0时,,U0‘《0;而UI1《0时,U0’》0,由于U0与UI1反相,故要求U0’与U0同符号。因此,当模拟乘法器的k小于零时,UI2应小于零;而k大于零时,UI2应大于零;即k与UI2同符号。同理,若乘法模拟器的输出端通过电阻接集成运放的同相输入端,则为保证电路引入的是负反馈,UI2与k符号应当相反。

在上述电路图中,设集成运放为理想运放,则Un=Up=0,为虚地,i1=i2,则

UI1/R1=-Uo/R2=-kUI1UI2/R2

整理上式,得出输出电压

Uo=-R2UI1/kR1UI2

令R1=1K,R2=2K

则Uo=-2UI1/kUI2

除法运算电路设计方案二:二输入的除法电路

设计一个二输入的除法电路,需要利用对数和指数运算电路实现或者用模拟乘法器在集成运放反馈通路中的应用来实现。

接通电源后,将电路板的各管脚接好,u11、u12分别接两个输入端。由于有两个变量对观察u0带来不变,在研究u0的变化趋势是常常用控制变量法,即u11、u12中的一个不变,一个变化引起u0变化并观察它的变化趋势。

除法运算电路设计方案三:基于减法的除法器的算法

对于32的无符号除法,被除数a除以除数b,他们的商和余数一定不会超过32位。首先将a转换成高32位为0,低32位为a的temp_a。把b转换成高32位为b,低32位为0的temp_b。在每个周期开始时,先将temp_a左移一位,末尾补0,然后与b比较,是否大于b,是则temp_a减去temp_b将且加上1,否则继续往下执行。上面的移位、比较和减法(视具体情况而定)要执行32次,执行结束后temp_a的高32位即为余数,低32位即为商。

verilog HDL代码

/*

* module:div_rill

* file name:div_rill.v

* syn:yes

* author:network

* modify:rill

* date:2012-09-07

*/

module div_rill

(

input[31:0] a,

input[31:0] b,

output reg [31:0] yshang,

output reg [31:0] yyushu

);

reg[31:0] tempa;

reg[31:0] tempb;

reg[63:0] temp_a;

reg[63:0] temp_b;

integer i;

always @(a or b)

begin

tempa 《= a;

tempb 《= b;

end

always @(tempa or tempb)

begin

temp_a = {32‘h00000000,tempa};

temp_b = {tempb,32’h00000000};

for(i = 0;i 《 32;i = i + 1)

begin

temp_a = {temp_a[62:0],1‘b0};

if(temp_a[63:32] 》= tempb)

temp_a = temp_a - temp_b + 1’b1;

else

temp_a = temp_a;

end

yshang 《= temp_a[31:0];

yyushu 《= temp_a[63:32];

end

endmodule

/*************** EOF ******************/

testbench代码

[html] view plain copy/*

* module:div_rill_tb

* file name:div_rill_tb.v

* syn:no

* author:rill

* date:2012-09-07

*/

`timescale 1ns/1ns

module div_rill_tb;

reg [31:0] a;

reg [31:0] b;

wire [31:0] yshang;

wire [31:0] yyushu;

initial

begin

#10 a = $random()%10000;

b = $random()%1000;

#100 a = $random()%1000;

b = $random()%100;

#100 a = $random()%100;

b = $random()%10;

#1000 $stop;

end

div_rill DIV_RILL

(

.a (a),

.b (b),

.yshang (yshang),

.yyushu (yyushu)

);

endmodule

/******** EOF ******************/

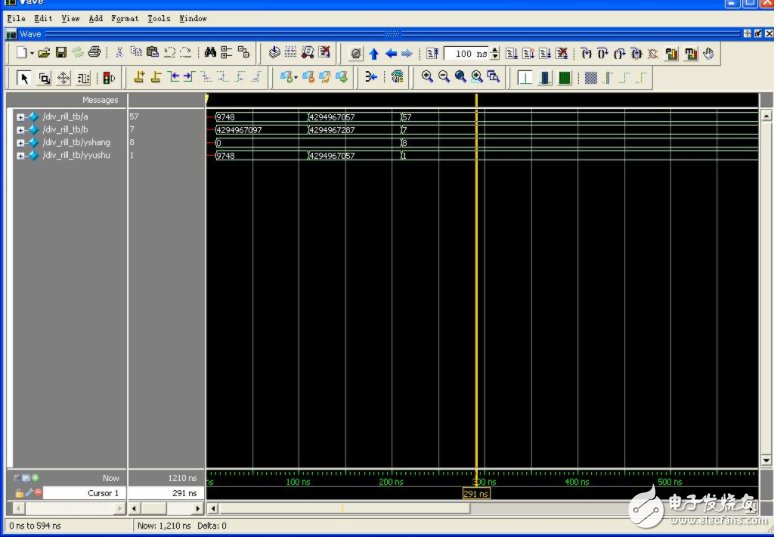

仿真结果

除法运算电路设计方案四:反相输入除法运算电路

反相输入除法运算电路原理图

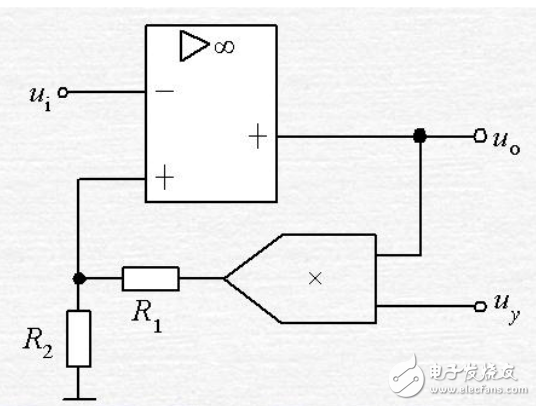

除法运算电路设计方案五:同相输入除法运算电路

同相输入除法运算电路原理图

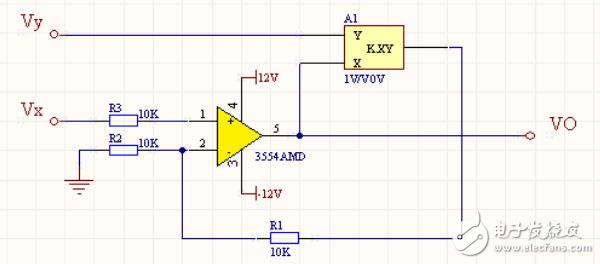

除法运算电路设计方案六:除法运算电路

信号源Vx经过运算放大器放大后与Vy一起经过乘法器处理后再反馈到运算放大器的输入端,最后从运算放大器的输出端输出,得到相应的结果。

除法运算电路设计方案七:模拟除法器电路图

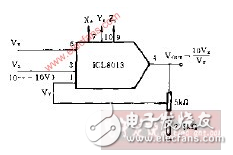

除法运算电路设计方案八:采用ICL8013的除法运算电路图

详细电路设计方案:采用ICL8013的除法运算电路图

采用ICL8013的除法运算电路图

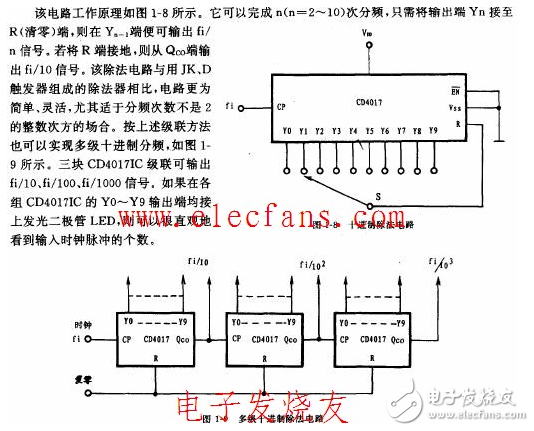

除法运算电路设计方案九:十进制除法电路

详细电路设计方案:十进制除法电路

-

小信号放大电路设计方案汇总2021-09-14 3261

-

电流检测电路设计方案汇总(六款模拟电路设计原理图详解)2018-02-06 330157

-

简单过流保护电路设计方案汇总(七款模拟电路设计原理图详解)2018-02-01 152809

-

断水报警器电路设计方案汇总(四款模拟电路设计原理图详解)2018-01-29 11819

-

停电报警器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-28 43106

-

五人表决器电路设计方案汇总(五款模拟电路逻辑图及原理图详解)2018-01-18 114730

-

减法器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-17 94880

全部0条评论

快来发表一下你的评论吧 !