利用74LS161实现复杂状态机

IC应用电路图

描述

状态机的写法

有限状态机FSM思想广泛应用于硬件控制电路设计,也是软件上常用的一种处理方法(软件上称为FMM有限消息机)。它把复杂的控制逻辑分解成有限个稳定状态,在每个状态上判断事件,变连续处理为离散数字处理,符合计算机的工作特点。

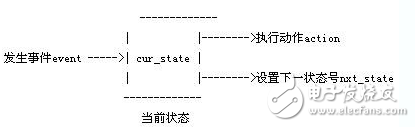

有限状态机的工作原理如图所示,发生事件(event)后,根据当前状态(cur_state),决定执行的动作(action),并设置下一个状态号(nxt_state)。

图 有限状态机工作原理

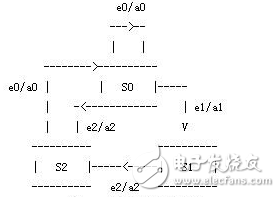

下图为一个状态机实例的状态转移图,它的含义是:

在s0状态,如果发生e0事件,那么就执行a0动作,并保持状态不变;

如果发生e1事件,那么就执行a1动作,并将状态转移到s1态;

如果发生e2事件,那么就执行a2动作,并将状态转移到s2态;

在s1状态,如果发生e2事件,那么就执行a2动作,并将状态转移到s2态;

在s2状态,如果发生e0事件,那么就执行a0动作,并将状态转移到s0态。

图0一个有限状态机实例

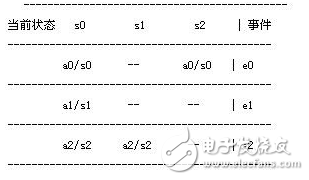

有限状态机不仅能够用状态转移图表示,还可以用二维的表格代表。一般将当前状态号写在横行上,将事件写在纵列上,如表1所示。其中“--”表示空(不执行动作,也不进行状态转移),“an/sn”表示执行动作an,同时将下一状态设置为sn。下表和图0表示的含义是完全相同的。

表 图2状态机实例的二维表格表示(动作/下一状态)

时序逻辑电路的数学模型是有限状态机(FiniteStateMachine)。时序逻辑电路的设计通常用触发器来实现,状态机越复杂,设计过程也越复杂。利用MSI(Medium-ScaleIntegration)也可以实现复杂状态机,虽然设计过程比利用触发器实现要复杂,但电路相对简单。在数字逻辑系统中,计数器是基本部件之一。集成计数器芯片类型很多,文中主要讨论使用MSI同步计数器74LS161进行复杂状态机的设计。

74LS161功能介绍

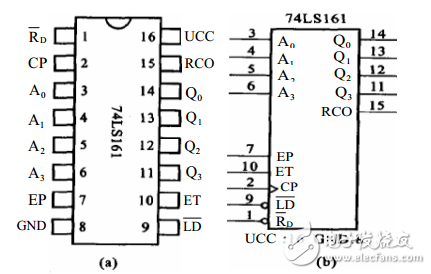

74LS161的引脚排列和逻辑功能如图1所示。各引出端的逻辑功能如下。1脚为清零端/RD,低电平有效。2脚为时钟脉冲输入端CP,上升沿有效(CP↑)。3~6脚为数据输入端A0~A3,可预置任意四位二进制数。7脚和10脚分别为计数控制端EP和ET,当其中有一脚为低电平时计数器保持状态不变,当均为高电平时为计数状态。9脚为同步并行置数控制端/LD,低电平有效。11~14脚为数据输出端QQ30~。15脚为进位输出端RCO,高电平有效。

图1 四位同步二进制计数器74LS161

(a)引线排列图;(b)逻辑功能图

设计过程

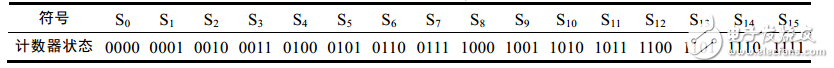

计数器的状态转换一般为顺序转换,电路也很成熟,例如S1→S2、S4→S5等。在实现模M的计数器时,一般也是利用连续状态进行顺序转换。但如要实现复杂状态机,则需要充分了解计数器的特性,利用置零端和置数端,完成非顺序状态转换,例如S1→S0、S4→S6等,从而实现复杂状态机。下面讨论对计数器74LS161的功能进行扩展,实现非顺序状态转换(图2)。计数器状态与符号的对照见表1.

表1 计数器状态与符号的对照表

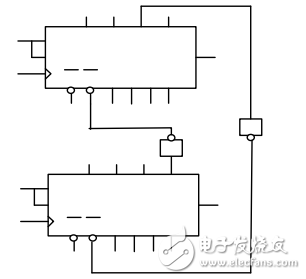

图2中,74LS161(0)片和74LS161(1)片的初始状态均设为0,两片在CP脉冲到来时同时开始计数,当(1)片循环至状态S4时,会给(0)片一个置位信号,当第5个CP脉冲到来时,(0)片被置位状态S7.之后,一直到第9个CP脉冲到来前,由于(1)片Q2端始终为1,故(0)片始终保持状态S7.当第9个CP脉冲到来时,(1)片和(0)片的状态分别为S9和S8,此时,(1)片得到(0)片Q3端的置位信号,当下一个CP脉冲到来时,(1)片和(0)片的状态分别为S4和S9.在第10个CP脉冲作用下,(1)片和(0)片的状态分别为S4和S9.在第11个CP脉冲作用下,(1)片和(0)片的状态分别为S4和S7,如此往复。这样,两片74LS161(1)片和(0)片并行输出状态变化为01000111→01010111→01100111→01110111→10000111→10011000→01001001→01000111,7种状态非顺序的转换。

图2 非顺序状态转换电路

如实现非顺序更多状态的转换,就需要使用更多MSI芯片,图3为使用三个74LS161芯片实现的复杂状态机。在图3中,三个芯片的初始状态均设为0,并且在CP脉冲到来时同时开始计数,当第7个CP脉冲到来后,实现有效状态循环000001001001→000001001010→000001001011→000001001100→000001001101→000001001110→000001001111→000001000000→000001010001→000001100010→000001110011→000010000100→000110010101→001010100110→001110110111→010011000111→000011011000→000001001001,为17种非顺序状态的转换。可见,实现越复杂的状态机,转换的非顺序状态越多,电路越复杂。

图3 复杂状态机电路图

可能出现的问题

在实际的电路中,由于使用多个集成电路,可能会出现置0不可靠的情况,这是由多个触发器的负载不同,置0时间也不完全相同引起的,此时需要在以上电路设计中做一些改进。另外,MSI与负载门电路的连接等问题,可以通过增加上拉电阻、接地电阻及电平转换等措施解决。

-

8.9.4 74LS161介绍(1)#硬声创作季学习硬声知识 2022-12-03

-

74ls161引脚图及功能介绍2021-07-08 235124

-

74ls161商品批发价格 74ls161引脚图与管脚功能测试2021-06-08 11624

-

三片74LS161怎么级联计数2400?2019-04-24 4224

-

74ls160和74ls161区别2018-05-08 127873

-

基于74LS161的扭环形计数器自启动设计2018-01-17 43865

-

74ls161制作24进制计数器设计2018-01-16 129459

-

74ls161中文资料_74ls161计数器功能及其应用2018-01-02 563609

-

求助关于74ls161的分频电路2013-07-05 12981

-

74ls1612013-05-20 5530

-

基于可编程计数器74LS161的循环码计数器设计2012-02-29 4789

-

74LS161计数器及显示应用电路图2007-12-02 16128

全部0条评论

快来发表一下你的评论吧 !