74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

IC应用电路图

描述

74LS161功能介绍

74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端,可以串接计数器使用。

74LS161的引脚排列和逻辑功能如图1所示。各引出端的逻辑功能如下。1脚为清零端/RD,低电平有效。2脚为时钟脉冲输入端CP,上升沿有效(CP↑)。3~6脚为数据输入端A0~A3,可预置任意四位二进制数。7脚和10脚分别为计数控制端EP和ET,当其中有一脚为低电平时计数器保持状态不变,当均为高电平时为计数状态。9脚为同步并行置数控制端/LD,低电平有效。11~14脚为数据输出端QQ30~。15脚为进位输出端RCO,高电平有效。74LS161可编程度数器的真值表如下。

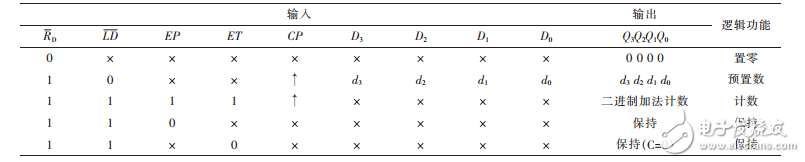

表 74LS161可编程度数器的真值表

一、74LS161集成计数器电路(十进制计数器)

单片161可以实现16以内任意进制的加法计数功能。实现途径有清零法和置数法两种。以实现十进制加法计数器为例:

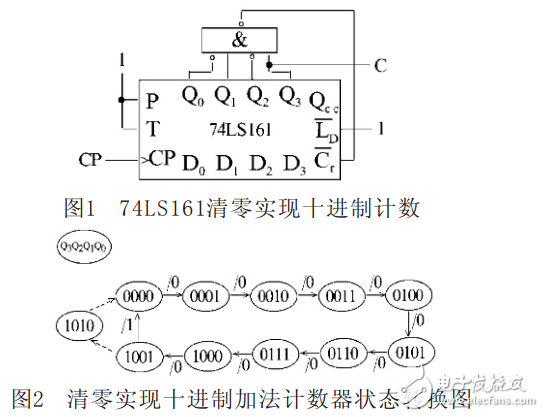

1)161的是异步清零端。当Q3Q2Q1Q0=1010(即10)状态时,通过译码电路给出低电平信号,将计数器清零回到0000状态。电路图和状态转换图如图1,图2所示。

由于置零信号随着计数器被置零而立即消失,所以置零信号持续时间极短,可能触发器还未来得及复位,置零信号已经消失,导致电路的误动作。因此,这种电路的可靠性不高。为了克服这个缺点,时常在译码电路和之间加一个SR锁存器,延长置零信号的宽度,从而增加电路的可靠性。

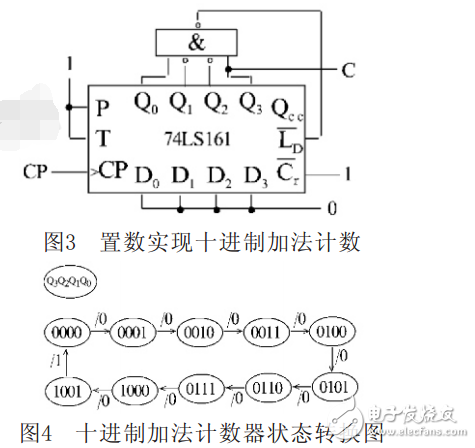

2)161的是同步置数置数端,可以用置数法实现十进制加法计数功能。161共有16个状态,采用置数法实现十进制加法计数功能时只要跳过其中任意6个状态就可以,方法有很多,这里仅举一种。当Q3Q2Q1Q0=1001(即9)状态时,通过译码电路给出低电平信号,将计数器置0回到0000状态。电路图和状态转换图如图3,图4所示。

由于161的置数是同步式的,所以不存在异步置零法中因置零信号持续时间过短而可靠性不高的问题。

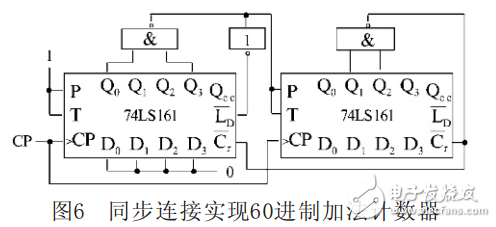

二、74LS161集成计数器电路(60进制计数器)

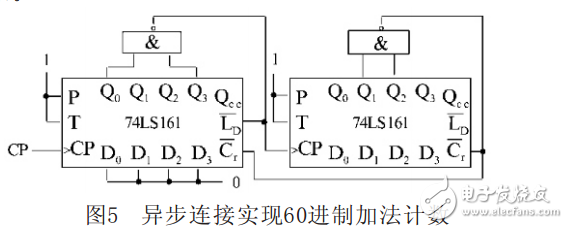

实现60进制加法计数器需要2片161,它们之间的连接方式又分同步和异步两种。

1)异步连接方式。低位的161通过置数法设计为十进制加法计数器,每十个CP向高位161进一。当高位161计数到0110(即6)时,对两片161同时清零,电路回到0状态。电路图如图5所示。

异步连接方式实现60进制时,高位161的CP与低片译码电路相连,译码可能丢失高频成分,导致译码电路因吉布斯过冲在一个时钟周期产生多个上升沿,从而引起电路的误动作,计数器出现错误。可以在低位161的与非门和高位161的cp之间加一个滤波电容来增加异步连接方式的可靠性。

2)同步连接方式。两片161的CP都连接到计数脉冲输入端,当低位161计数到1001(即9)时,通过译码电路让高位161加1。当高位计数到0110(即6)时,对两片161同时清零,电路回到0状态。电路图如图6所示。

同步连接方式中高位161和低位161的CP一起连接在时钟信号源上,则杜绝了异步连接方式中的重复计数的可能。

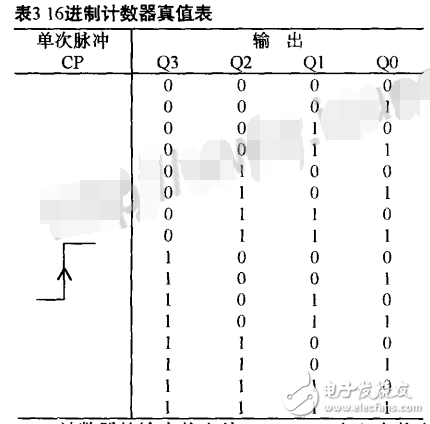

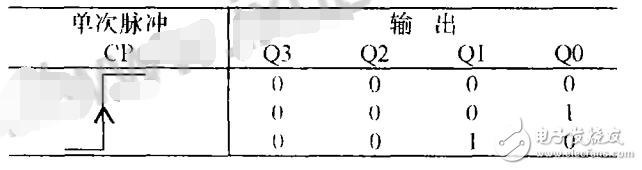

三、74LS161集成计数器电路(16进制计数器)

线路图如图3(注意:以下电路连接的图3为此图3.16进制加法计算器)

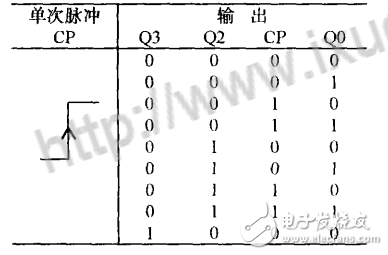

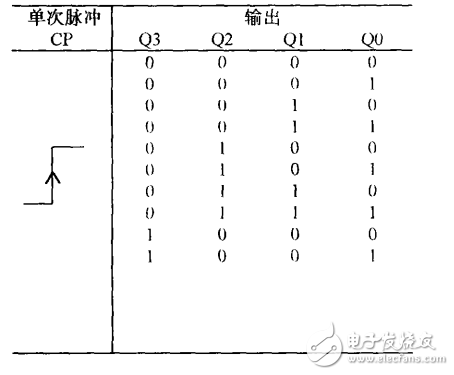

图3中的CTP=CTT=/LD=1,/CR端接复位脉冲端,按动单次脉冲CP,则LED显示十六进制十数状态,其真值表如表7所示。

计数器的输出状态从0000~1111十六个状态,其应用电路可做为4位的地址码或数据,若位数不够可采用两片以上的74LS161芯片扩展为8位、16位或更多的位数。

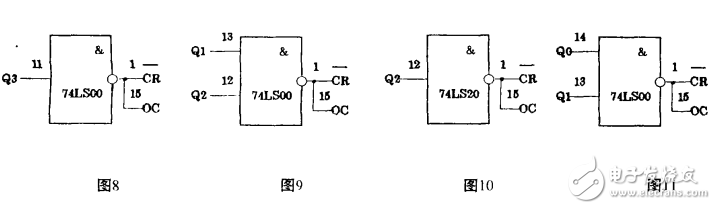

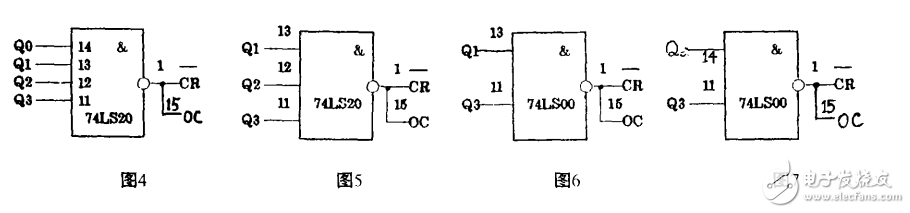

四、74LS161集成计数器电路(3进制计数器)

从表1的真值数不难看出图11所示的74ls00连接方式为3进制计数器。

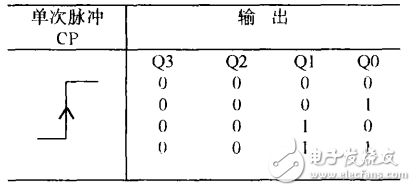

表1 3进制计数器真值表

五、74LS161集成计数器电路(4进制计数器)

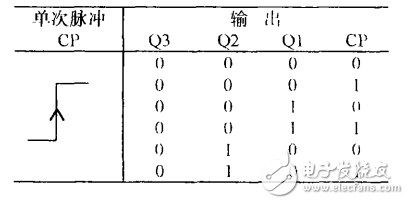

将74ls00接成图10方式与74LS161连接、输出的状态如表2所示。

表2 4进制计数器真值表

六、74LS161集成计数器电路(6进制计数器)

用74ls00与74LS161连接如图9所示,所测得的真值表如表3所示。

表3 6进制计数器真值表

七、74LS161集成计数器电路(8进制计数器)

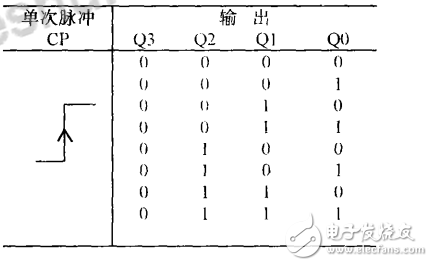

将74ls00的与非门输人端和输出端如图8接至图3中组成8进制计数器,其用途可用作模数转换器例ADC0809的输入通道地址码的8个通道,其真值表如表4。

表4 8进制计数器真值表

八、74LS161集成计数器电路(9进制计数器)

将与非门74ls00如图7接入图3中,组成9进制计数器,其真值表如表5所示。

表5 9进制计数器真值表

九、74LS161集成计数器电路(10进制计数器)

利用74ls00(2输人与非门)与74LS161组成十进制计数器,此种进制计数器使用广泛,例如其输出可接译码驱动显示电路的计数输人端完成十进制数码的显示,其连接方式如图6,其真值表如表6。

表6 十进制计数器真值表

-

74ls160和74ls161区别2018-05-08 127783

-

基于74LS161的60进制计数器设计方案介绍2018-01-17 71487

-

74ls161制作24进制计数器设计2018-01-16 129360

-

74ls161中文资料_74ls161计数器功能及其应用2018-01-02 563466

-

采用归零法的N进制计数器原理2012-03-20 3103

-

基于可编程计数器74LS161的循环码计数器设计2012-02-29 4776

-

74LS161异步置零法构成任意进制计数器的Multisim仿真2011-08-05 10553

-

74LS161构成的五十(50)进制计数器电路图-原理图2009-03-28 37708

-

集成计数器实验2009-03-20 933

-

74LS161计数器及显示应用电路图2007-12-02 16115

-

二进制同步计数器74LS161引脚图及功能表(管脚图)2007-11-22 60343

全部0条评论

快来发表一下你的评论吧 !