如何利用Verilog-A开发器件模型

描述

文章来源:SPICE 模型

原文作者:若明

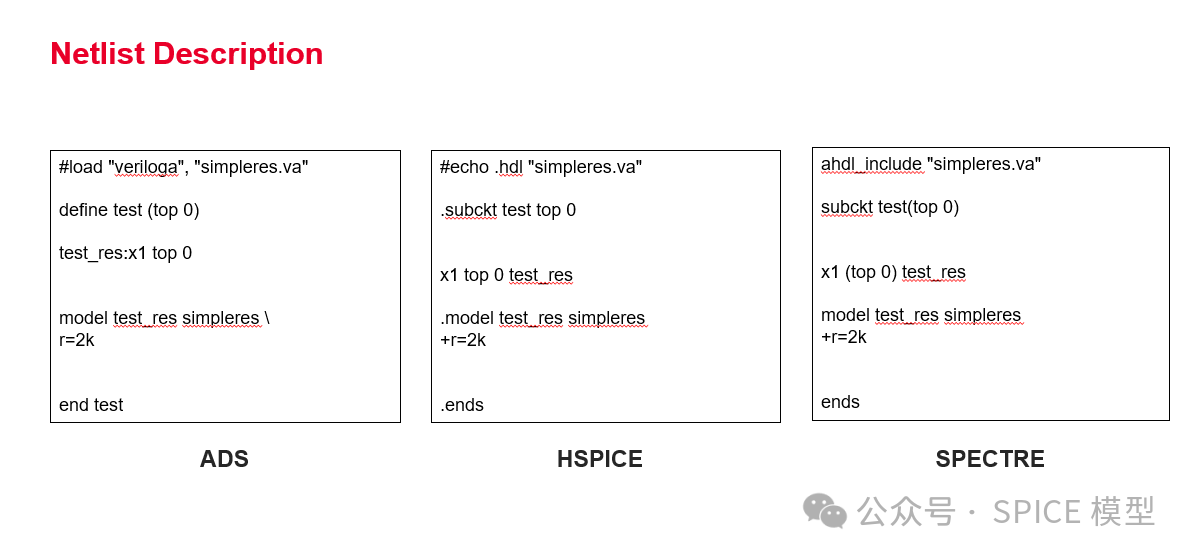

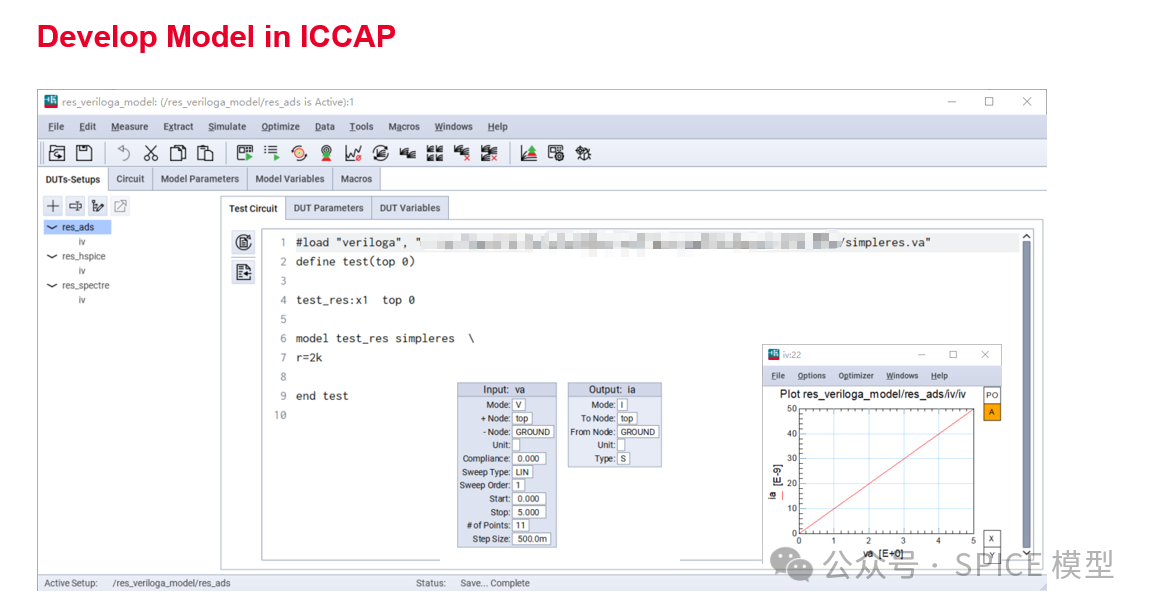

Verilog-A对紧凑型模型的支持逐步完善,在模型的实现上扮演越来越重要的角色,已经成为紧凑模型开发的新标准。而且Verilog-A能够在抽象级别和应用领域中扩展SPICE建模和仿真功能,因此学会如何用Verilog-A来开发器件模型在建模领域将尤为重要。今天就来以简单的例子来介绍如何开发一个Verilog-A Model。

SPICE电路元件模型通常称为紧凑型模型。它们应该足够简单,以提供有效的电路仿真,并足够精确,使仿真结果对电路设计者有用。随着在LRM 2.2中引入语言扩展以支持紧凑的器件建模,Verilog-A已成为电子行业中用于开发有源和无源半导体器件紧凑模型的标准语言。

假设:

您是一个器件工程师/研究者

您需要的是一个Compact Spice Model(而不是TCAD Model)

您对一个器件的物理特性比较了解

您已经有一组方程来描述器件端口的电压电流特性

您需要理解的是:

什么是Compact Model

电路仿真器如何使用一个Compact Model

如何将器件的电路方程编写为Verilog-A Model

需要了解一些常见的错误和Debug的能力

需要知道如何测试您的Model

一个简单的例子

Amplifier Model的例子

对一个放大器建模是一个比较基础的例子,但是要增加额外的效应,则是具有挑战性的。如果简单的来考虑放大器,可以简单的认为输出为增益乘以输入。我们从电路设计的角度,自下而上地来看一个放大器的模型:Spice晶体管级模型,功能级模型,结构级模型,行为级模型。

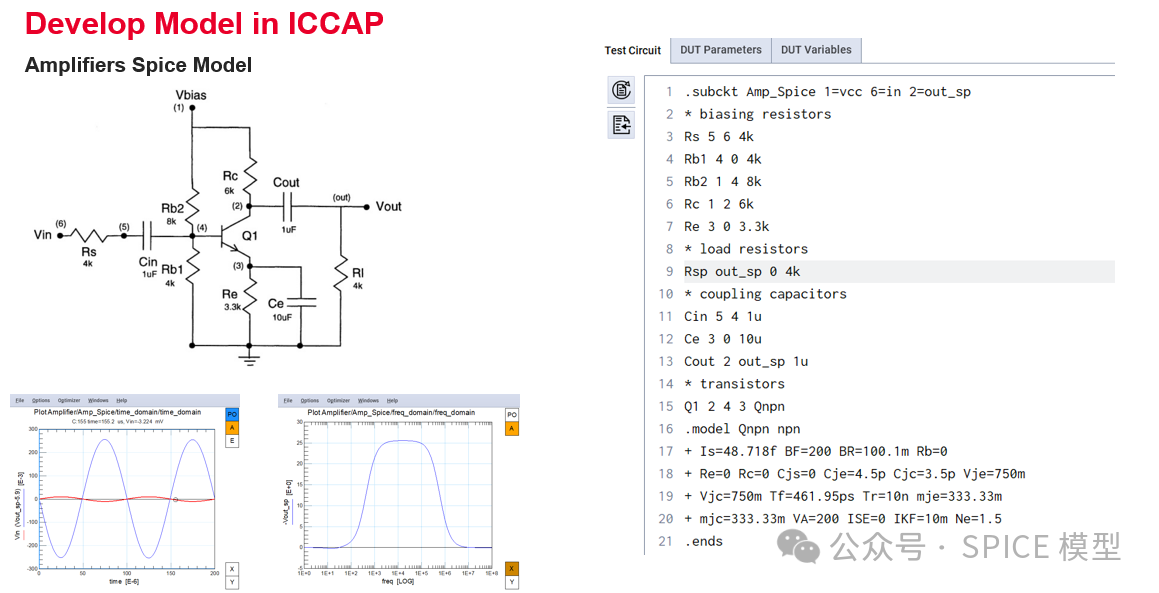

Spice晶体管级模型

在晶体管级模型,首先要非常清楚最底层的放大器的电路是如何设计的,并且要有每一个最底层的元器件的Spice Model。要按照电路使用Spice语法描述电路,搭建Subckt Model。Spice Model多用于IC设计领域。

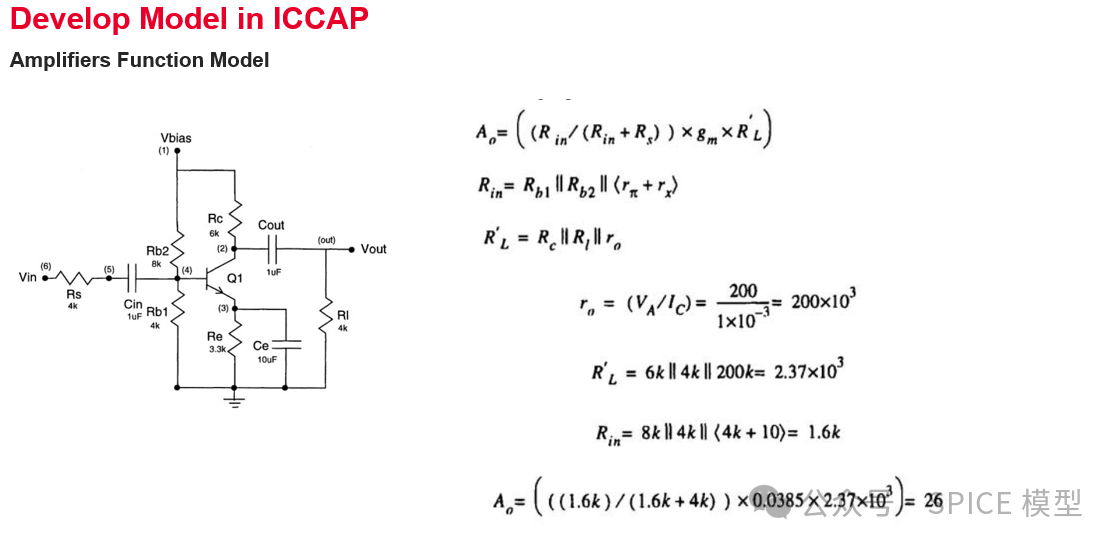

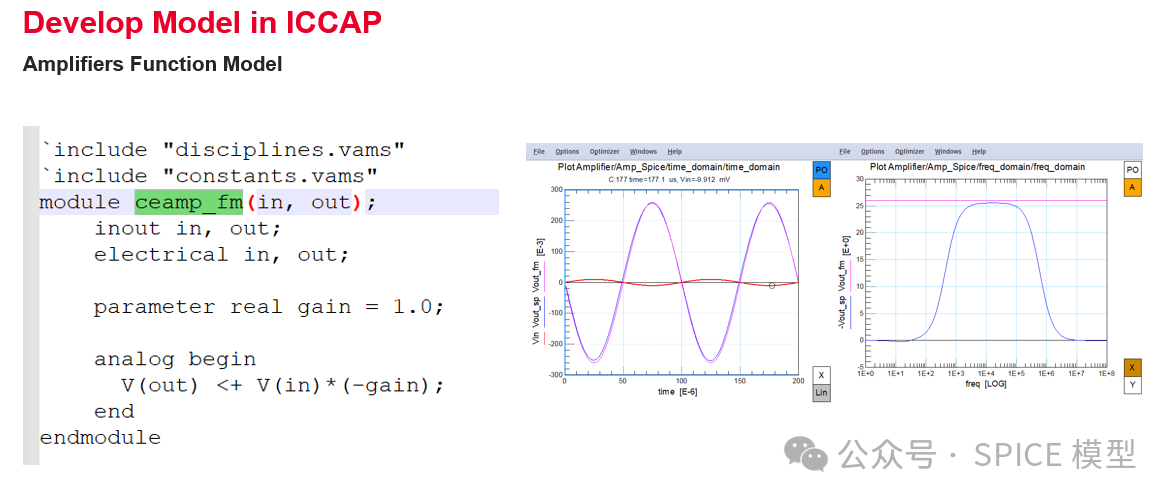

功能级模型

在功能级模型,首先要对电路功能进行分析。以放大器为例,我们最关心的功能是其放大增益,经过推导,推导出增益,然后以Verilog-A来实现。

在这里gain作为放大器的参数,可以改变。如下图所示,与Spice Model比较,只反映出放大特性,没有考虑频率的响应。

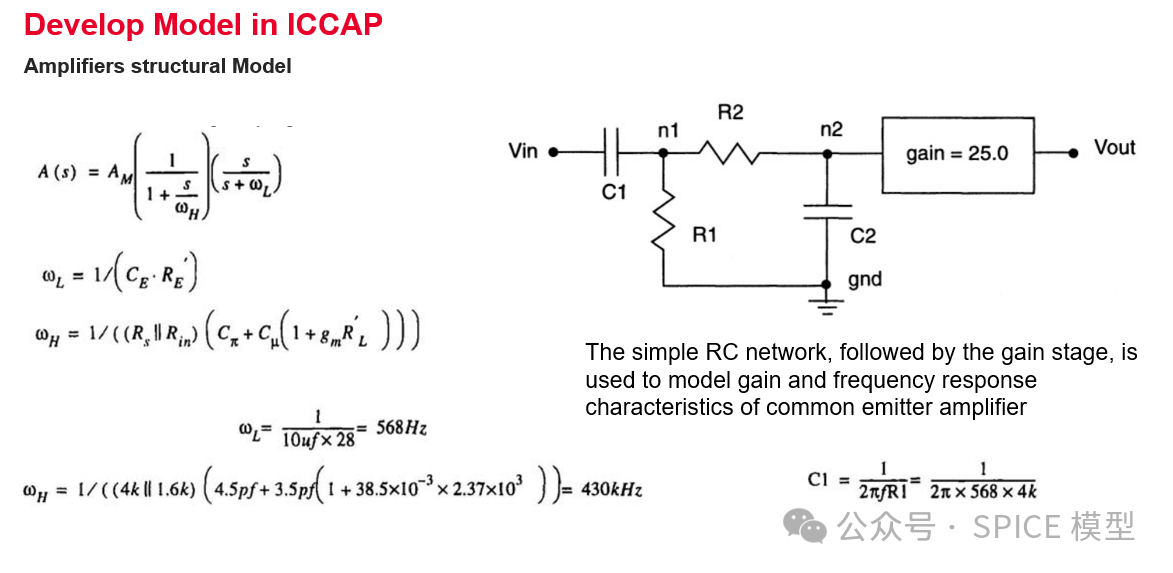

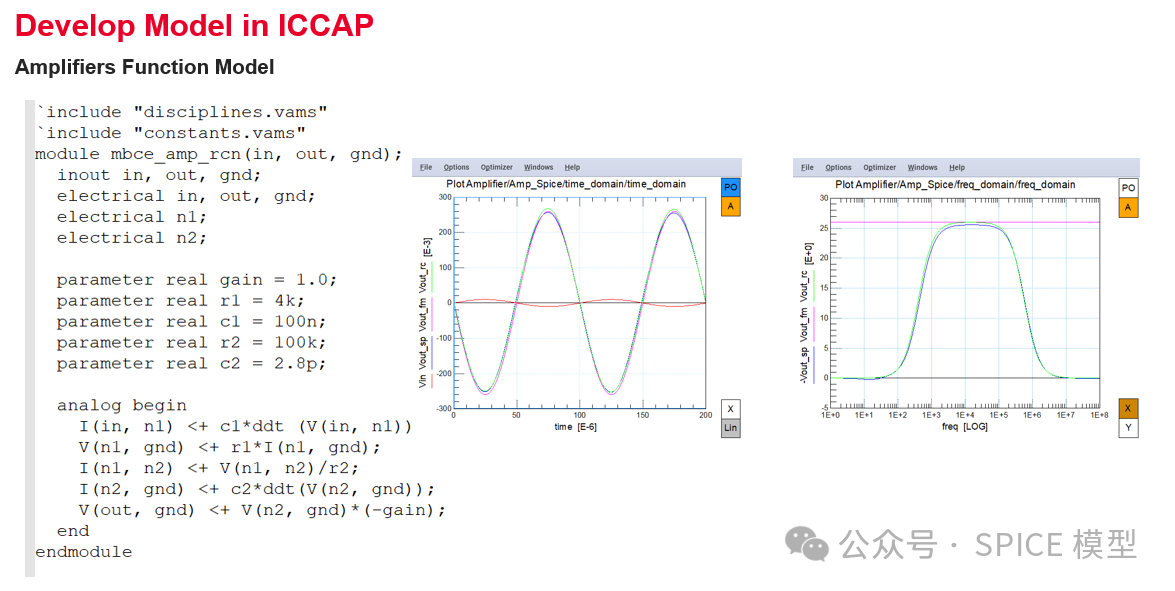

结构级模型

如果在简单的增益模型的基础上考虑频率的响应,我们可以通过结构级模型实现。首先,要考虑放大器对频率的特性,通过推导,发现其频率相应可以通过RC网络来实现。

在这里增加RC网络的参数,来表征放大器对频率的响应。如下图所示,通过调谐RC网络参数,可以达到和Spice Model接近的效果。

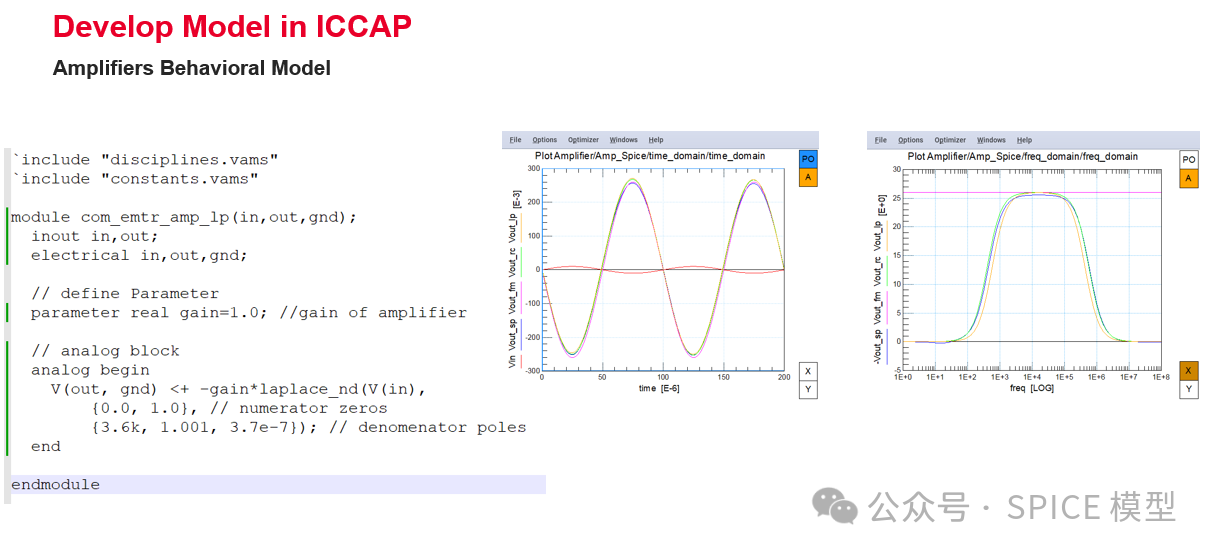

行为级模型

Verilog-A语言包括实现集总线性连续时间滤波器的内置拉普拉斯变换函数。该变换用于模拟放大器的频率效应,将其行为视为一个简单的带通滤波器。此类模型我们可以认为是行为级模型,通常在更顶层的系统级电路中使用。如下图所示,与Spice Model比,也能够达到接近的效果。

-

Verilog 测试平台设计方法 Verilog FPGA开发指南2024-12-17 2024

-

DataFlash Verilog 模型用户手册2023-03-13 349

-

ST公司的M25Pxx SPI flash memory的verilog仿真模型2021-07-30 2278

-

业界领先的半导体器件SPICE建模平台介绍2020-07-01 4165

-

Cadence中Verilog语言参考使用教程免费下载2020-06-10 1463

-

Verilog HDL虚拟器件和虚拟接口模型2017-02-07 842

-

Verilog-A 将设计精度推向一个新的水平2017-01-14 626

-

基于Verilog_A与Matlab的行为描述模型的CDR设计2017-01-07 1122

-

利用LINGO开发高级模型选讲2010-11-13 690

-

Verilog-A Reference Manual2010-08-22 677

-

Verilog-A的模拟电路行为模型及仿真2009-11-21 941

全部0条评论

快来发表一下你的评论吧 !