三星联手IBM搞5nm新工艺叫板台积电 台积电5nm工厂已经启动

电子说

描述

晶圆代工龙头台积电昨(19)日发出邀请函,5 纳米新厂将在下周五(26日)动土,董事长张忠谋亲自主持动土典礼,未来将有三期厂房生产5纳米制程产品,显示看好产业需求。台积电在日前法说会中,不但第1季淡季效应不显著,还提前预告「第2季更好」,昨日股价应声大涨,市值冲破新台币6.6兆元,再写新高。

台积电日前举行法说会,公布去年第4季和全年财报,虽然汇率波动,但包括全年营收、税后纯益和每股纯益等三项财务指标都写下历史新高纪录,成为张忠谋今年6月最好的退休礼物。

台积电第1季营收季减幅度在一成以内,张忠谋亲自预告,第2季将会强劲成长。若以美元计价,2018年在高效能运算、物联网、车用电子等三大领域驱动下,全年业绩至少成长10%。

张忠谋对前景看法乐观,外资纷纷喊买,昨日收盘价大涨7元、收255.5元,刷新历史新高价位,市值突破6.6兆元,同样创新高。

除了营运趋势和股价表现亮眼,台积电昨日发出邀请函,预定26日举行晶圆18厂动土典礼,当天活动将由张忠谋主持。

台积电总经理暨共同执行长刘德音于去年供应链管理论坛就曾透露,5纳米制程发展符合进度,位于台南科学园区的晶圆18厂将于今年动土,将有三期厂房生产5纳米,预计2019年上半年风险性试产。

5nm工厂是南科12寸超大型晶圆厂Fab 14的延伸,预计将兴建第8期至第10期等共3个厂区,5nm合计月产能可望上看9~10万片。

台积电5nm新厂今年9月动土,占地超过40公顷,由于建厂及设备成本愈来愈高,5nm 3个厂区的总投资金额将创下新高纪录,设备业者推估应达新台币2,000亿元。

除5纳米外,台积电去年9月也宣布3纳米相关计划,3纳米新厂同样座落于南科,投资金额将超过200亿美元。

台积电出货与产能目前都保持积极状态,中国大陆南京厂提前于5月开始出货,位于***的5纳米厂将动土,3纳米新厂建厂计划也加速进行中,持续挑战全球半导体业两大霸主英特尔和三星。

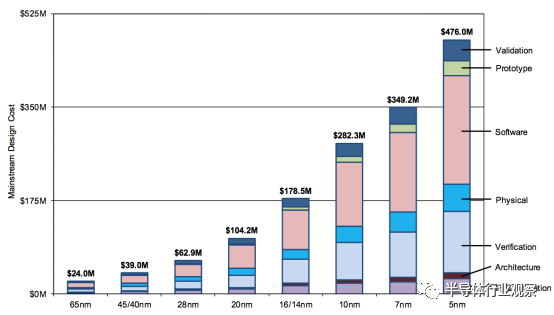

张忠谋也表示,5nm规划使用极紫外光(EUV) 微影技术,以降低制程复杂度。但根据IBS的估算,在5nm节点,设计一款主流芯片的成本将高达4.76亿美元水平,而7nm节点的成本仅3.492亿,28nm则是0.629亿。

三星联手IBM搞5nm新工艺叫板台积电

作为台积电最有竞争力的竞争对手,三星联手IBM打造5nm新工艺叫板台积电。

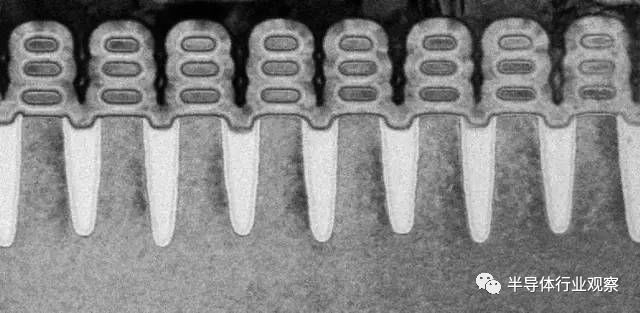

为了实现这个壮举,就必须在现有的芯片内部构架上进行改变。研究团队将硅纳米层进行水平堆叠,而非传统的硅半导体行业的垂直堆叠构架,这使得5nm晶体管的工艺有了实现可能,而这一工艺将有可能引爆未来芯片性能的进一步高速发展。

实际上,从工艺架构本身来说,这种从垂直架构到水平层叠的转换相当于在硅晶体管上打开了第四扇“门”,使得电信号能够在芯片中通过不同的晶体管。而从尺寸上来说,这些晶体管的宽度不大于两三根并排在一起的DNA分子链。

那到底能为我们的生活带来怎样的改变?根据 IBM 官方的说法,比较直观的描述是,当我们在阅读这篇文章时,假设正在使用的移动设备只剩下 10% 的电量,但基于 5 纳米制程技术的芯片将使得移动设备在需要充电之前仍然可以使用数小时,而不是几分钟。未来配备此类新型芯片的移动设备续航时间将比现在要延长数天。

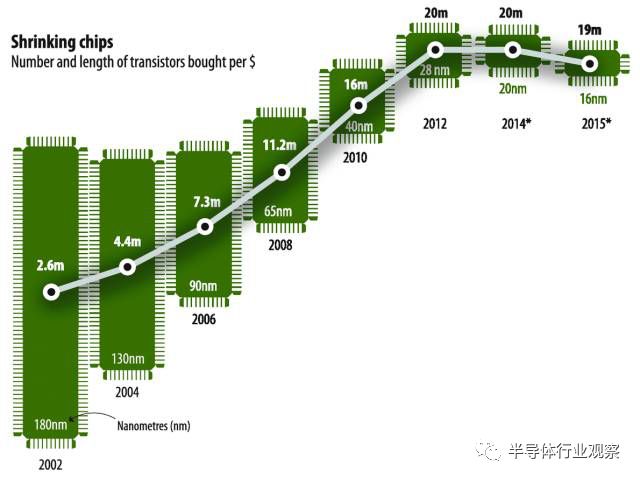

数十年来,半导体产业对缩小电子元件的狂热追求是有原因的。芯片上集成的电路越多,电子产品的速度越快、效率越高、成本越低。而著名的摩尔定律在 1965 年首次提出之时则认为,芯片上的晶体管数量每年翻一番,该预测在 1975 年被更改为每两年。

尽管半导体行业集成技术的发展速度越来越达不到摩尔定理的预期,但不管怎么说,晶体管的尺寸还是在变得越来越小。

图丨摩尔定律

其实,半导体的缩小并不是什么高技术活儿。上一个主要突破就发生在 2009 年,研究者们发明了一种叫做FinFET的晶体管设计方式,而其第一次大规模制造则开始于 2012 年——这给整个行业打了一剂强心针,为 22 纳米这一尺寸上的处理器创造了可能。FinFET是晶体管行业的革命性突破——其关键在于,在三维结构而非二维平面上控制电流的传递。

IBM半导体研究小组副组长 Mukesh Khare 表示,“原则上说,FinFET的结构就是一个简单的长方形,其中的三条边上各有一个小门”。如果把晶体管想象成一个开关,不同的电压就会控制这道门“开启”或“关闭”。在三个不同方向上加上门能够最大化这个开关的电流量,并最小化电流的漏出,所以增加了整体的效率。

但在五年后,这一技术也几乎发展到了尽头。对此,半导体制造公司 VLSL Research 首席执行官 Dan Hutcheson 表示,问题在于 FinFET 就像一条流淌的小溪。FinFET在目前常见的 10 纳米处理器上正常工作,在 7 纳米上应该也没有问题。“但在5纳米的尺度上,我们就需要一个新的结构了。”Hutcheson说。

图丨IBM Research Alliance 在几层硅芯片上的 5 纳米晶体管

终于,在 FinFET 的垂直结构发展终结之后,IBM 宣布在与 Global Foundries 和三星的合作下开发出了水平排布的硅纳米板,并以这种结构在晶体管上加了第四道门。你可以想象 FinFET 的结构调转了过来,元件相互叠在了顶上。在尺度上来说,电信号在一个和 DNA 螺旋一样大的开关上流动。

“这是一个巨大的进步”,Hutcheson说。“如果我们能把晶体管变得更小更密集,我就能在同等面积的芯片得到更快的处理速度。”也就是在一个指甲的芯片上,从 200 亿个 7 纳米晶体管飞跃到了 300 亿个 5 纳米晶体管。对此,IBM 预计,会在同样功率上把处理效率提高 40%,或者在同样效率上减少 70% 的功耗。

图丨IBM 科学家 Nicolas Loubet 握着使用业界一流制程工艺生产的 5nm 硅晶体管芯片

虽然根据行业内的预估,基于新架构所开发的可商用处理器不会在2019年前投入市场。但不可否认的是,5 纳米处理器工艺的成熟与否将决定未来自动驾驶和5G通讯等行业的商业化程度。

“整个社会的发展全靠它了!因为未来即将出现的人工智能、自动驾驶等技术都对计算能力提出了更高的要求,”Hutcheson说。“没有新的处理器生产技术,人类文明将就此停滞。”

就拿自动驾驶技术来举例,虽然我们现在已经可以实现自动驾驶汽车的上路行驶,但不得不说,其所依赖的智能芯片的价格仍然高达数万美元,这对于准备大规模商业化的产品来说,显然不太现实。而 5 纳米制程工艺的出现将有希望将这一成本大幅降低。

再比如,IoT(物联网)传感器设备由于需要不间断地收集实时的数据流,所以必须保持一直在线的状态,而要做到这一点,也必须依靠高性能的处理器。

IBM半导体研究小组副组长 Mukesh Khare 对此有一个精辟的评价:“摩尔定律所衍生的超高经济价值是毋庸置疑的,其关键之处就在于效率的提升和价值的创造是依赖于架构的创新,而非传统的扩大规模的方式。”

-

台积电5nm架构设计试产2019-04-24 4150

-

全球进入5nm时代2020-03-09 3647

-

台积电开始建设新的5nm工厂,并将于2020年启动3nm工厂2018-01-25 5566

-

台积电宣布新5nm工厂开工 三星联手IBM欲与台积电一争高低2018-01-26 1370

-

台积电5nm将开工,三星与IBM开始展开合作,中国芯何时突破重围?2018-05-28 1250

-

台积电5nm新工艺工厂开工 2020年开启批量生产2018-01-29 1203

-

台积电5nm工艺预计会在2020年量产 再降低20%的能耗2018-05-04 4283

-

台积电正在为新款iPhone生产基于5nm工艺制程的处理器2019-06-17 726

-

台积电宣布7nm及5nm增强版新工艺2019-07-31 3484

-

台积电2nm工艺制程研发启动,预计2024年可实现投产2019-08-26 3628

-

苹果与华为将包揽2020年台积电的整个5nm产能2020-03-05 3255

-

台积电5nm工艺预计今年贡献10%的营收2020-04-20 3320

-

台积电5nm与三星5nm的本质差异 三星5LPE与台积电N5详解2021-01-30 34520

-

台积电将在美国建设5nm晶圆厂,计划2024年量产2020-11-04 1941

-

高通:骁龙888将由三星5nm独家代工 比台积电更适合2020-12-03 4007

全部0条评论

快来发表一下你的评论吧 !