结合实际时统项目提出了一种基于FPGA的高速时间统一系统设计方案

电子说

描述

时间作为物理学的基本量纲之一,是系统运行的重要参考指标,而IRIG-B码作为国际标准时间码,其性能优越,实现和使用方法简单易行,十分适合应用于高精度时间传输系统中。

FGPA具有编程方便、集成度高、速度快等特性,可反复编程、擦除及使用,在不改动硬件设计的情况下,可实现不同的功能需求。采用FPGA实现授时、分频,产生时间信号和各种同步信号,可以使时统接口模块集成度更高,可维护性更强。

本文结合实际时统项目提出了一种基于FPGA的高速时间统一系统设计方案,它以Altera[1]公司Cyclone系列FPGA[2-3]芯片为核心,采用原理图和Verilog语言编程[4]实现。通过接收GPS、北斗、B码等外部基准,并选择其中一路产生与其同步的IRIG-B码信号和各脉冲信号,供其他分系统使用。

1 系统总体设计

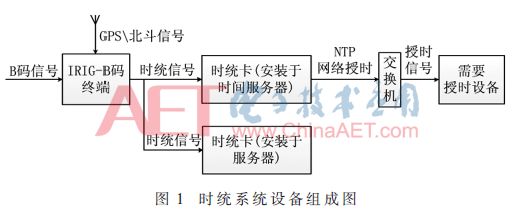

时统系统硬件包括时统卡(安装于服务器)和IRIG-B码终端[6]。图1为时统系统设备组成图。

IRIG-B 码终端可以实现GPS卫星系统与北斗卫星系统的双系统时间信号冗余接收以及外来B码信号的直接接收,产生多路直流或交流IRIG-B码发送给时统卡。

时统卡通过直接接收IRIG-B码并通过解码电路自动获取标准时间信息,通过VPX总线向配有时统卡的服务器发送时统信息,服务器接收时统信息后,向服务器自身、网络内各工作站和终端进行网络授时,实现对设备自身信号严格的监控和输出,以提高系统的可靠性及满足时间同步要求。

2 IRIG-B码编码原理

IRIG-B码是国际通用的一种常用串行传输方式时间格式码,与并行传输方式相比,其物理连接简单、信息量大、分辨率高、传输距离远、抗干扰能力强、具有标准化接口。根据时间精度的不同要求及B码传输距离的不同,B码采用了两种码型:B(DC)直流码和B(AC)交流码。B(DC)码的每个码元是一个脉冲信号,可以实现较高精度的时间同步,但脉冲信号频谱丰富,窄带信道无法传输,适用于短距离电缆传输;B(AC)码则可以使用标准语音带宽(0.3 kHz~3.4 kHz)信道传输,传输距离更远,但传输精度有一定损失。B(AC)码可由B(DC)码对标准正弦波载波进行幅度调制得到。根据不同要求可选择不同码型传输,在本时统系统中,两种码型均有应用。

3 B码终端

B码终端可以接收GPS/北斗的授时信号和外来B码信号,通过编解码处理生成1PPS脉冲信号与DC/AC时间编码信号,以供时间同步设备使用。

3.1 B码终端系统原理及组成

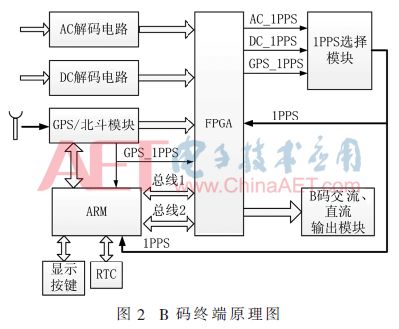

B码终端系统原理图如图2所示。

B码终端可同时接收GPS/北斗信号和外来B码信号。当GPS/北斗信号到来时,GPS/北斗模块通过天线接收授时信号,向ARM和FPGA发送1PPS脉冲信号,同时以串行方式向ARM发送时间信息;ARM将解出的时间信息及有效标志,通过自定义总线和通信协议发送至FPGA; FPGA在接收到1PPS与时间信息后,根据信息的有效性决定选用该时间信息或自守时的方式,生成多路AC/DC码和1PPS信号向外输出。当外来B码到来,通过AC/DC解码电路,将外来B码信号整形运放,然后传给FPGA进行编解码。

3.2 B码终端单元模块设计

(1)GPS/北斗模块

选用精度为30 ns、1 PPS的GPS/北斗模块,向FPGA和ARM传输时间信号,并支持通过串口命令对芯片进行配置。

GPS/北斗模块输出包含UTC年、月、日、时、分、秒。ARM处理器通过模块提供的1PPS中断接收整秒信号,并通过异步串行通信方式获取时间信息。

(2)外部B码解码电路

当采用外部B码信号作为产生IRIG-B码的基准时,需要对外部B码基准进行接收解调,以产生基准秒和串行时间数据。在本设计中,采用硬件电路完成对外部B码基准的解调工作。

(3)1PPS选择模块

FPGA对GPS/北斗信号及外来B码信号进行处理,产生AC_1PPS、DC_1PPS、GPS_1PPS信号,作为ARM与FPGA之间通信基准。

(4)FPGA各功能模块设计

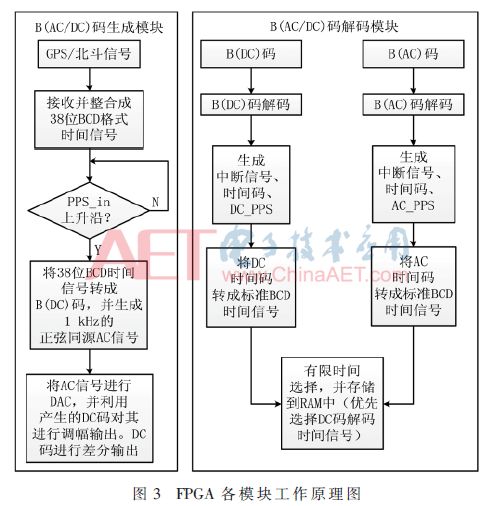

FPGA作为B码终端的核心,实现了时码产生、同步分频、外来B码信号解码等功能,主要包含B(AC/DC)码生成模块、B(DC)码解码模块、B(AC)码解码模块等。各模块工作原理如图3所示。

B(AC)码生成模块:FPGA根据GPS/北斗模块的时间信息产生AC码,其每一位的高低电平的AC码实际输出对应ROM中一个周期的正弦波形,FPGA输出的波形控制字发送至DAC,DAC输出对应电流值,经运算放大电路转换后生成对应AC码高低电平的正弦波形,最后经1:1变压器将波形输出。

B(DC)码生成模块:FPGA根据GPS/北斗模块的时间信息直接产生DC码的TTL输出,经单端/差分转换后,输出至多路DC码输出。

B码解码模块:FPGA通过完成外来B码的解码,以实现精准时间信息的提取并输出。

4 时统卡

时统卡设计采用通用的VPX接口,可接收标准化时统的IRIG-B(DC)码、IRIG-B(AC)码输入,设备可以通过上层驱动从VPX总线[5-6]上捕获当前时间信息,采集不同频率的中断信号。针对时统卡的具体要求,将时统卡划分为两个主要部分:硬件电路设计及IRIG-B码解码、时间获取软件设计。

4.1 硬件电路设计

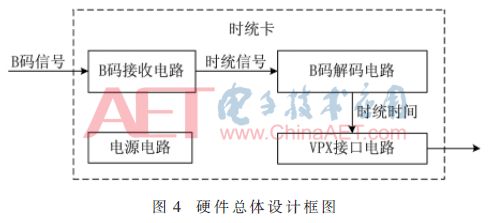

时统卡硬件总体主要包括B码接收电路、VPX接口电路、B码解码电路和电源电路。具体硬件结构设计框图如图4所示。

B码接收电路包含两部分,即B(AC)码和B(DC)码两种码型的接收,通过接收电路后,最终两种码型都以TTL电平方式传输到B 码解码电路。

B码解码电路主要由FPGA芯片和外围电路组成,通过FPGA编程开发完成B码的解码,实现时间信息的提取。

4.2 FPGA

FPGA通过完成B码的解码,以实现精准时间信息的提取,并与VPX接口通信。

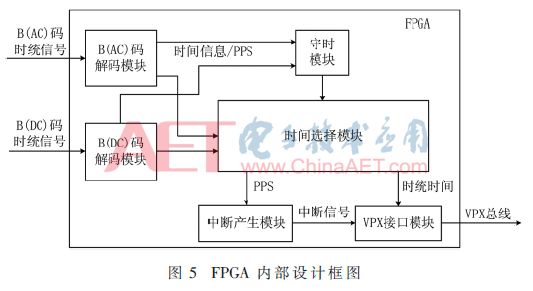

FPGA内部设计框图如图5所示。

FPGA的B码解码模块主要包括:B(DC)码解码模块、B(AC)码解码模块、时间选择模块、中断产生模块和VPX接口模块。FPGA程序可以完成时间信息的提取、B(DC)码和B(AC)码的自动切换,还可以通过B码解码过程产生的PPS 秒脉冲,实现不同时间的中断信号。VPX接口程序完成时间信息和中断信号的接收并传输到VPX总线。

B(AC)码解模块和B(DC)解码模块分别对两种时统信号根据B码的码型特点进行时间信息提取,并输出有效时间信息、时间有效标志和PPS秒脉冲。

有效时间选择模块根据B(AC)和B(DC)码解码输出的时间有效信号选择输出有效时间信号,这里优先选择B(DC)码时间信息。

中断产生模块根据PPS秒脉冲产生准确的、不同周期的中断时间信号,为上位机提供更高分辨率时间信号。

守时模块是FPGA在没有B码输入时,通过内部时钟计数产生秒脉冲和时间的更新。B码解码模块在没有成功解码时间信息时输出相应信号,通过时间选择模块完成守时时间的切换。守时模块在有B码输入时每个秒周期自动更新时间,并且自行进行时间计数,完成守时功能。

5 实验结果

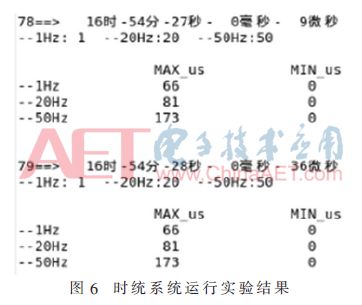

将B码终端与时统卡相连接,在接入GPS/北斗信号条件下,采用上位机对时统卡输出的信号进行读取。在读取过程中,为了显示直观性与简洁性,只在每秒初始时刻打印一次信息。另外,为了更加准确地反映时统系统及上位机读取的延时,上位机测试软件中加入了每秒读取时各个中断的最大及最小延迟。图6为时统系统运行实验结果。

经过多次长时间的测试,各个中断最大延迟均满足设计要求。

6 结论

本文的时统系统,其外围硬件电路简单, 可靠性高,时统卡使用VPX总线进行通信,满足靶场计算平台高性能、高带宽、抗恶劣环境的性能要求,有巨大的发展应用前景,已成功应用于某设备之中。经过长时间工作检验可知,设备工作稳定,指标满足要求。

-

求分享一种集中式插入法帧同步的FPGA的设计方案2021-06-02 2111

-

基于FPGA的VPX时间统一系统设计与实现2021-06-01 911

-

分享一种不错的无线语音传输系统设计方案2021-05-31 1082

-

分享一种FPGA的动态配置方案2021-05-27 1799

-

分享一种基于Actel Flash FPGA的高可靠设计方案2021-05-10 2401

-

怎么用ARM和FPGA实现一个实时图像采集传输系统的设计方案2021-05-07 1160

-

求一个基于FPGA的高速数据中继器设计方案2021-04-29 1423

-

分享一种不错的基于FPGA和USB的通用CCD采集系统设计方案2021-04-22 1461

-

一种基于FPGA和DSP的高速数据采集设计方案介绍2019-07-05 2596

-

一种基于FPGA的振动信号采集处理系统设计介绍2019-07-01 1824

-

一种基于FPGA的任意锁相倍频算法2013-12-04 5442

-

一种并行帧同步设计方案的提出、设计与应用2010-07-05 894

-

基于DSP和FPGA的GPS-B码时统终端系统设计2010-02-24 470

-

一种基于Flash型FPGA的高可靠系统设计2010-01-20 428

全部0条评论

快来发表一下你的评论吧 !