集成电路(IC)设计之后端设计步骤

电子说

描述

从理论上来说,物理综合工具拥有关于布局的所有必要信息;在实践中,它们也必须非常小心地与实际布局数据关联。

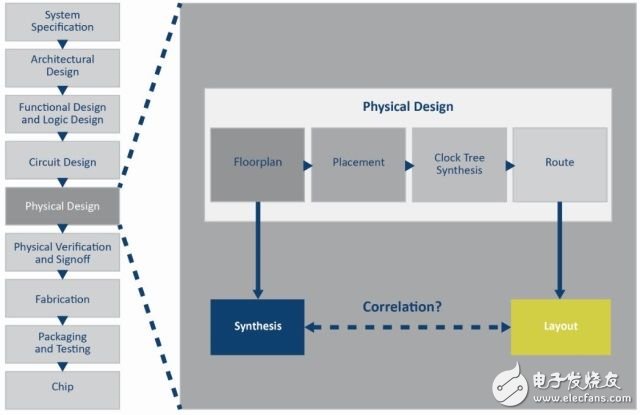

一个芯片的设计涉及到许多阶段,从系统规范和架构设计,各种制造方法以及最终装入设备的芯片成品的封装。在这个周期中,准确估计时序和面积将至关重要,因为这样才能制订准确的计划并使产品符合各方面的需求。本文将介绍这个过程的物理设计(或称后端设计)部分,特别是在与物理设计相关的步骤中将时序与面积关联起来。

集成电路 (IC) 设计流程和物理设计步骤 (图1)

综合与布局之间的关联问题

大型设计的整个物理设计流程可能需要很多天才能完成。因此,如果能够向设计和架构团队尽早提供反馈,让他们可以规划好时序限制,自由地快速利用布局选项,将能够创造宝贵的价值。为了实现这些目标,必须可靠地估计时序和面积。

在过去,我们已经很好地掌握了综合布局与布线之间的相关性。对于时序,准确度在3%至4%左右,而面积的结果甚至更好。但在新的先进工艺中,从28 纳米工艺节点开始,我们遇到了越来越多意想不到的结果。我们不仅看到了物理综合结果与布局和布线的实际时序之间更大的差距,而且还看到一部分时序路径明显变得更快,而其他时序路径则变慢很多,这相当令人费解。在观察面积时,结果更令人担忧。从综合到布局,相关性已经变得相当差,如下图所示:

布局规划阶段(顶部)与布局阶段(底部)的综合单元密度比较 (图2)

上面的图片是CEVA-XM4内核的单元密度图,比较了综合阶段(顶部)与布局阶段(底部)的单元密度。布局阶段图像的橙色部分显示了面积的显著增长。在这种情况下,面积的整体增长在18% 左右。这很不好,但也许还能忍受。但考虑到大部分设计是固定面积(内存和寄存器),从综合到布局根本不会改变,就很清楚某些部分确实会超过最高限制。把缓冲器单元面积分离之后我们发现综合面积增加了118%,这意味着缓冲器数和面积增加了一倍以上。

在达到极限单元密度(标记为橙色)的领域,布局工具发现很难确定单元的合理布局和进行多次迭代,因此需要花费大量时间进行收敛。

设法增强时序和面积的相关性

解决这个问题的第一次尝试是收紧频率。也就是说,我们尽量以较高的频率进行综合,然后在布局和布线阶段再切换到稍微低一些的频率。但这个解决方案并没能解决问题。另一个尝试是降低线网和单元的时序。实际上,降低时序就是增加让单元处理速度更慢或更快的系数。我们尝试了几个数字。我们探索的另一个方向是提高提取数字的相关性。这是通过将系数应用于被提取的线网电阻和电容 (RC) 值来实现的。这些值通过更改其 RC 值直接影响线网的延迟,并通过改变其负载电容从而影响单元的延迟。

从电气工程的角度来看,我们知道,随着制程工艺的收缩,电阻的作用会越来越突出。一方面,导线的电容保持大致相同(或至少采用相同的顺序)。另一方面,电阻会变得越来越高。除此之外,在先进的工艺节点上,最上面两个金属层的电阻比其他层的电阻低得多。而这也意味着对于布局工具来说,决定哪些电线进入更高层,哪些电线仍留在较低层会越来越成问题。最受影响的,当然是加了缓冲的长线网。这就是为什么缓冲器面积会有这样显著的增长,而与长线网相关联的时序会变差。

布局规划阶段(顶部)与应用系数后布局阶段(底部)的综合单元密度比较 (图3)

我们发现,越来越多的电阻提供更好的面积相关性和时序相关性。不同设计用于实现良好相关性的因素各不相同。如上图所示,将系数应用于阻力后,综合与布局之间的相关性显著改善。我们将综合面积(顶部)与布局面积(底部)再次进行了比较。从布局图像的橙色区域可以看出,仍有相当数量的高利用率负载,但比以前少得多。在这个示例中,准确度达到了5%左右,这是相当合理的,而且会实现良好、高效的工作流程。

把结果投入应用

我们已经看到,在先进工艺中,电阻对时序和面积有着巨大的影响。虽然从理论上来说物理综合工具拥有关于布局的所有必要信息,但在实践中它们仍必须非常小心地与实际布局数据关联。这个过程可能比较耗时,但好处显然超过了成本。在一天工作结束时,最好的做法是保持设计流程各步骤之间有一个可靠的相关性,从而获得快速、灵活的设计,并且从一开始就对最终目标有一个明确的认识。

-

集成电路IC芯片的三大测试环节2023-06-26 2964

-

如何选择数字电源集成电路 (IC)2022-11-04 810

-

集成电路ic是什么?2022-08-26 7730

-

东莞收购集成电路 回收集成电路2021-10-14 1485

-

什么是集成电路?集成电路的分类2021-07-29 3820

-

回收IC集成电路 收购IC集成电路2021-06-07 1695

-

后端集成电路SAA7158电子资料2021-04-08 831

-

珠海回收IC集成电路 珠海IC集成电路回收2020-07-11 1247

-

集成电路的设计与分工2018-08-20 3293

-

拆卸集成电路的方法及步骤2016-10-26 770

-

【招聘】集成电路IC设计——摩尔精英2016-04-28 2759

-

集成电路前端及后端设计培训2012-05-16 3151

-

集成电路IC卡规范设计2009-12-21 6330

-

集成电路2009-09-30 1472

全部0条评论

快来发表一下你的评论吧 !