基于FPGA工程的EDA设计

可编程逻辑

描述

以QuartusII13.0EDA软件为例,介绍Verilog文本输入的EDA设计流程。

1.首先在D盘或G盘等新建一个文件夹,用英文字母命名,例如建立文件夹SY1。

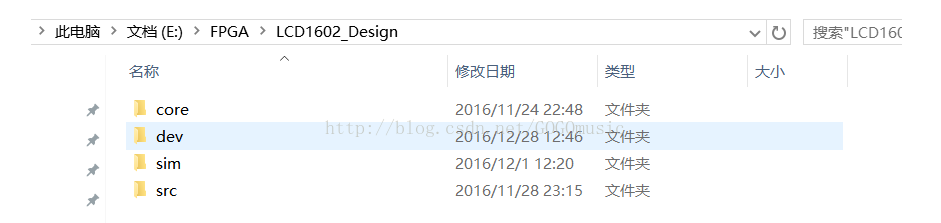

FPGA工程目录 : dev: 工程建立在此文件夹,工程设置

core:IP核保存区

src:用户代码保存区

sim:testbench仿真测试文件

doc:设计参考文档

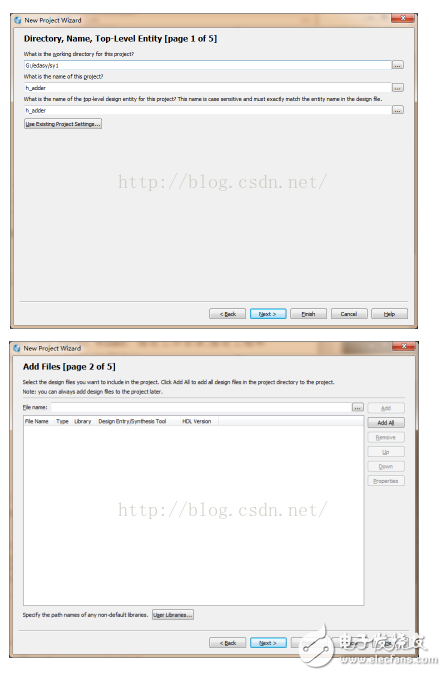

然后打开QuartusII软件,选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体;注意:工作目录名不能有中文。如图4-3所示。

图4-3 新建工程 图4-4 添加设计文件

2.添加设计文件。将设计文件加入工程中。单击“Next”,如果有已经建立好的Verilog等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL ,.Verilog原理图等)。如果没有直接点击“Next”,等建立好工程后再添加也可,这里我们暂不添加,如图4-4所示。

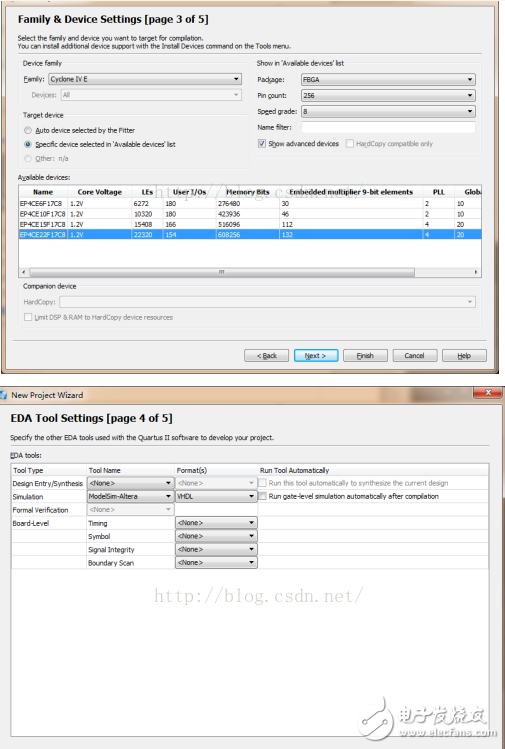

3.选择FPGA器件。EP4CE22F17C8器件选择如下:(Family选择CycloneⅣE,Available device选EP4CE22F17C8,Packge选择FBGA,PinCount 选择256,Speedgrade选择8);EP3C80F484C8器件选择如下:(Family选择CycloneIII,Available device选EP3C80F484C8,Packge选择FBGA,PinCount 选择484,Speedgrade选择8);笔者至今就用过这两种。如图4-5所示,点击“Next”。

图4-5 选择器件 图4-6 选择仿真器

4.选择外部综合器、仿真器和时序分析器。Quartus II支持外部工具, Quartus II 9.1以上版本软件没有自带的仿真工具, simulation选择Modelsim-Altera, Format:Verilog,则采用Modelsim仿真,如图4-6所示,选择完毕后,单击“Next”。

单击“Next”,弹出“工程设置统计”窗口,上面列出了工程的相关设置情况。最后单击“Finish”,结束工程设置。

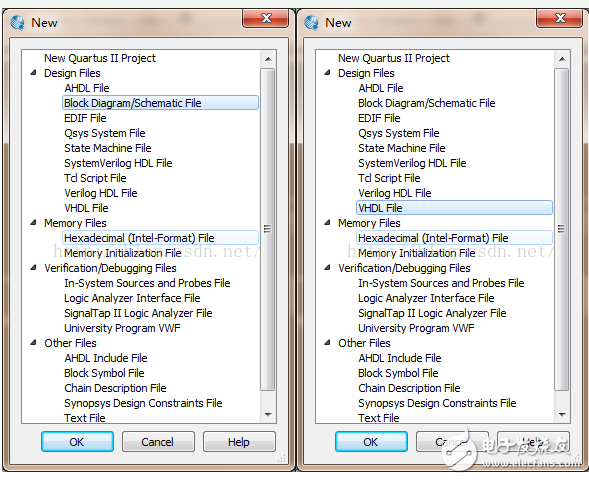

5.新建原理图/文本文件。如果在建立工程时没有添加设计文件,这时需要新建文件。点击“file”点击“new”选择,如果选择原理图输入,选择BlockDiaqram/Schematic File,如图4-7所示。如果选择Verilog文本输入,选择Verilog HDL File,如图4-8。

图4-7 新建原理图文件 图4-7 新建VHDL文本文件

6.点击“保存”,原理图或Verilog文本文件就被添加进工程当中。

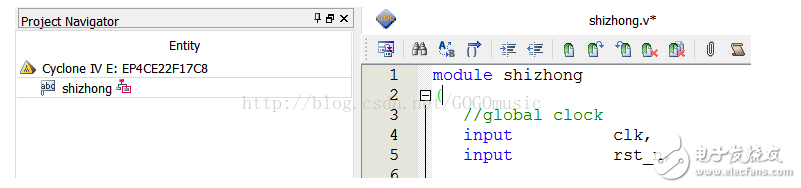

7.Verilog文本设计。

文本设计时,输入相应的Verilog程序,并保存,要格外注意保存的文件名与顶层文件module名保持一致。

8.编译。点击Processing/StartCompilation,进行编译。如果编译错误,重新检查和修改原理图或Verilog程序,保存并再次编译,提示编译成功后,开始进行管脚锁定和下载。

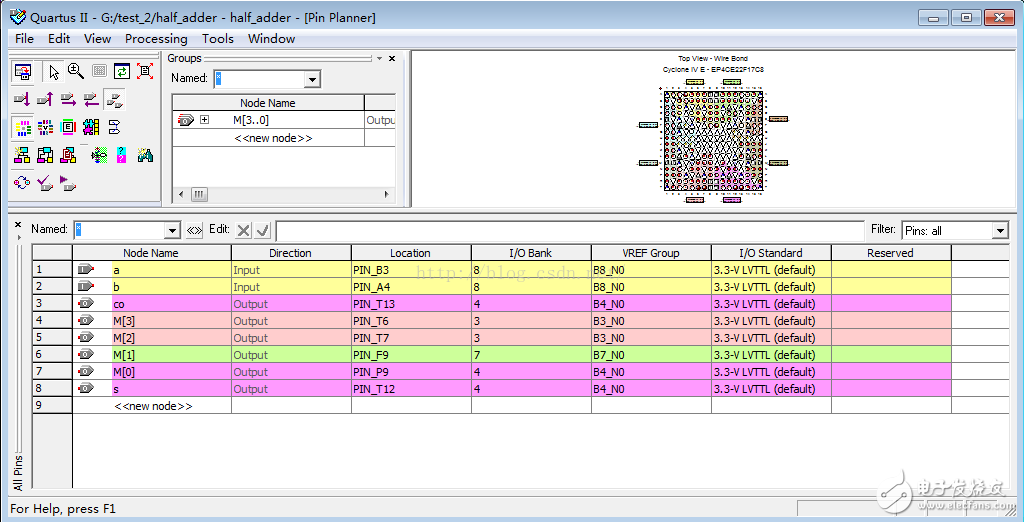

图4-13 管脚锁定

10.管脚锁定方法一:管脚锁定信息如图4-13所示,选择Assignments/PinPlanner进行管脚锁定,锁定所有的输入输出管脚。

管脚锁定方法二:见下次博客文档。

11.管脚锁定完成后,再次进行全局编译(包括综合、适配),点击Processing/StartCompilation。

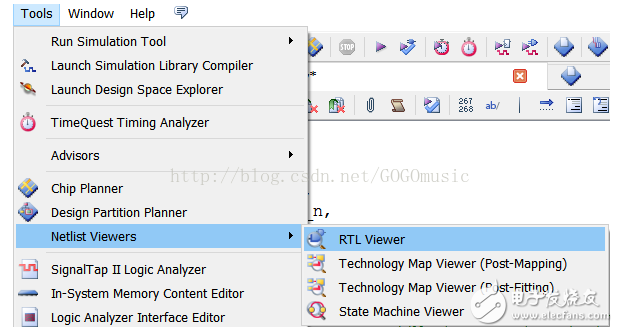

12. 全局编译完成,查看软件下方是否有编译错误。查看综合后RTL视图方法如图:

13.下载到EDA实验平台中。下载可以选择JTAG方式和AS方式(JTAG下载方式把文件直接下载到FPGA里面,AS下载方式把文件下载到配置芯片里面,因此可以掉电存储)。选择Tool/Programmer,选择JTAG下载方式,选择Add File,添加.sof文件(AS下载选择.pof文件)并选中Program/Configure,点击“Start”后开始下载。第一次使用下载时,首先点击“HardwareSetup.。。”,打开Hardware Setup对话框,然后点击Add Hardware,选择usbblaster后单击”Select Hardware”,选择下载形式为usb blaster。

14. 在做Quartus II工程时必须将未分配的管脚置为三态输入。Quartus II --》 Assignments --》 Device…--》 Device --》 Device & PinOptions… --》 Unused Pins --》 Reserve all unusedpins : AS input tri-stated。如未将未分配管脚置为三态输入,将可能导致主芯片或外围芯片损坏。

-

FPGA可以用来对FPGA EDA进行加速设计2022-09-02 1172

-

基于EDA技术的FPGA设计计算机有哪些应用?2019-11-01 2653

-

基于EDA技术的FPGA该怎么设计?2019-09-03 2279

-

EDA技术与FPGA设计应用的详细阐述2019-06-18 2639

-

基于FPGA的EDA综合实验系统设计赵刚2017-03-19 894

-

FPGA设计新需求走热 EDA战况升温2013-04-17 2979

-

多种EDA工具的FPGA设计方案2010-05-25 939

-

EDA Tools in FPGA2009-12-05 775

-

多种EDA工具的FPGA协同设计2009-06-20 957

-

基于多种EDA工具的FPGA设计2009-05-14 1073

-

EDA(CPLD/FPGA)技术概述2008-09-24 3398

全部0条评论

快来发表一下你的评论吧 !