1200字彻底掌握运算放大器电路的关键参数选型计算:共模抑制比 CMRR

1200字彻底掌握运算放大器电路的关键参数选型计算:共模抑制比 CMRR

描述

Part 01

前言

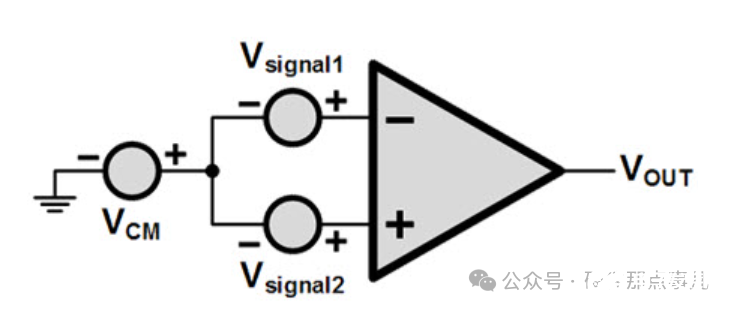

运放的共模抑制比 (CMRR) 是一个重要参数,它表示运放抑制共模信号对运放输出影响的能力。理想的运算放大器应具有无限大的CMRR,也就是说当运放的两个输入具有相同的电压时,则放大器的输出应该为零,但是事实上,由于运放的差分输入级中晶体管参数的不匹配,导致当运放的两个输入具有相同的电压时,在运放的差分输入级中也会产生偏移电压,经过电路放大以后,会在运放输出端产生较大的输出偏移电压。

Part 02

共模抑制比的定义

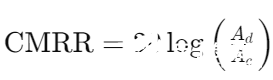

关于共模抑制比的定义,我们经常会看到两种不同的定义方式,第一种是下面的定义,其中Ad是运放的差模输入电压增益,Ac是运放的共模输入电压增益。运算放大器对+输入端和-输入端的电压差进行放大,但实际运算放大器中由于共模输入电压的变化,运放输入级电路的直流工作点会发生发生变化,因此差模电压增益和共模电压增益会发生变化。理想运放的共模增益为0,差模增益为无穷大,但是实际的运放差模增益是有限的,共模增益由于上面的原因也不为0,为了表征运放共模增益的大小,所以就有了CMRR的概念,它表示的就是运放对共模信号抑制能力的大小,Ac越小,Ad越大,CMRR也就越大。

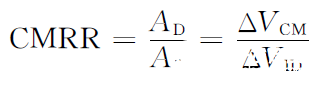

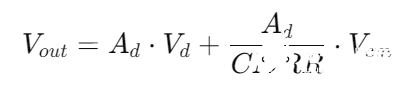

从上面第一种对于CMRR的定义,我们可以理解CMRR存在的意义是什么,从实用性的角度来说下面这种定义方式将可以让我们方便的定量计算CMRR对于输出偏移电压的计算:

这个公式是如何推理得到的呢?

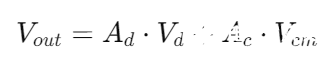

1.运放的输出电压Vout可以通过以下公式计算:

2.基于CMRR=Ad/Ac,带入上面的式子就能得到:

3.整合一下上面的式子可以得到:

这样就能得到输入共模电压在运放输入端以及输出端产生的偏移电压:

输入端:偏移电压=Vcm/CMRR

输出端:偏移电压=Ad*Vcm/CMRR

通过上面的推导可以看出较高的CMRR会显著降低共模信号对输出的干扰。

比如运放的共模输入电压为20V,CMRR为100dB,运放电路放大倍数为100,那么在运放输入端的偏移电压为:

100dB=20*log(Ac) ->Ac=10^5

输入端偏移电压=20V/10^5=0.2mV

输出端偏移电压=0.2mV*100=20mV

所以虽然共模电压在运放输入端引起的偏移电压不大,但是经过径路放大之后可就不小了。

Part 03

如何得到运放电路的共模抑制比

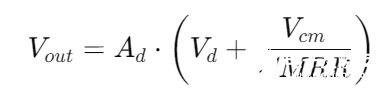

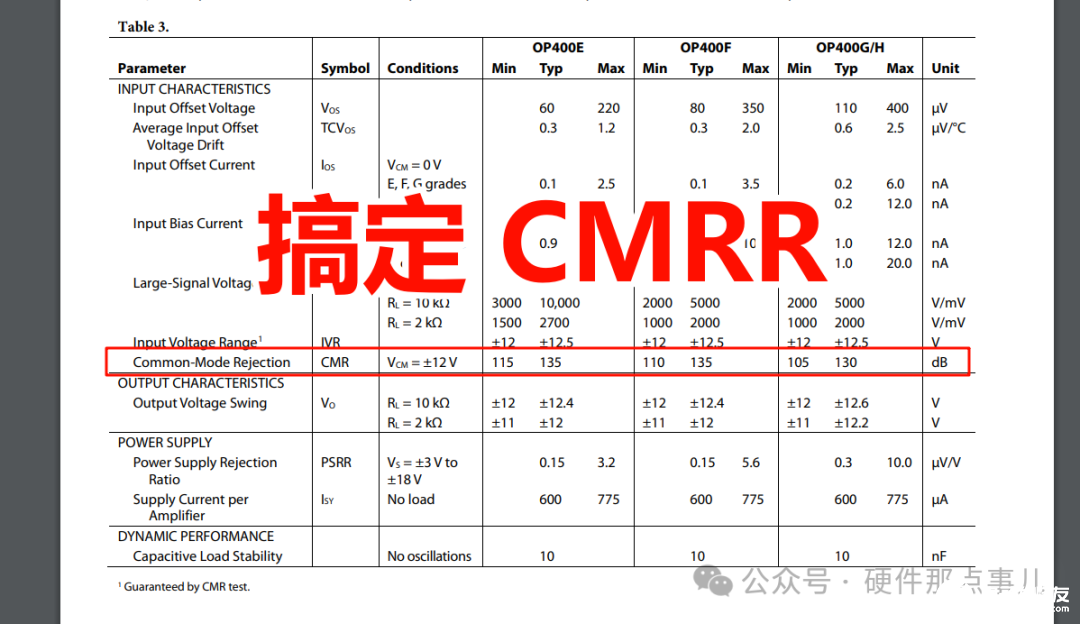

1.规格书查阅,比如下图中运放的共模抑制比最小为80dB。

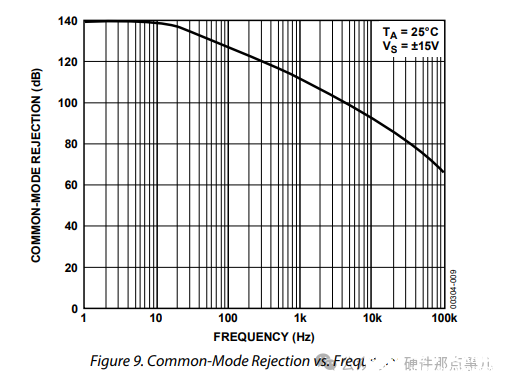

2.需要注意的是运放的共模抑制比会受到输入信号频率的影响,比如下面是运放规格书中给出的CMRR-频率曲线,频率越高,CMRR越小。

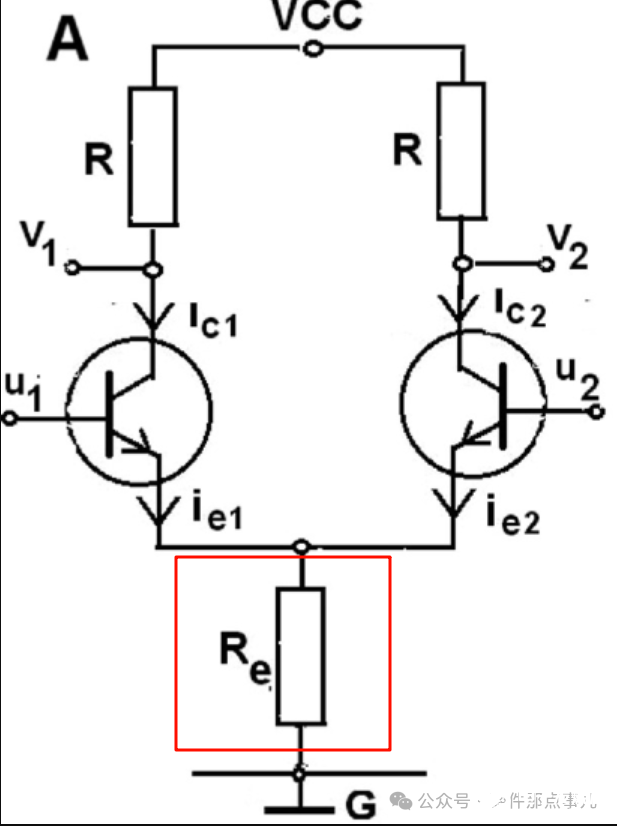

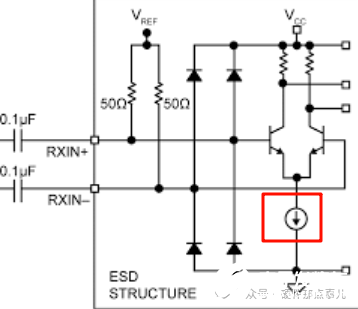

简单说一下运放的CMRR为什么会受到输入信号频率的影响,下图是运放输入级的拓扑电路,如果你能想起模拟电路课本里的知识,Re电阻的作用就是降低输入级两个晶体管不对称(参数有差异)的影响,所以Re越大越好,但是毕竟是电阻做不到非常大,所以一般是用恒流源来替代Re,因为恒流源来替代(恒流源的高输出阻抗使得恒流源能够在负载变化时维持稳定的输出电流),但是恒流源的缺点就是运放中的拖尾恒流源存在寄生电容,进而导致频率会影响恒流源等效阻抗的大小。

Part 04

留个问题

是不是在规格书中看到的运放的共模抑制比就是运放电路的实际共模抑制比呢?共模抑制比还受到哪些不可忽视的关键因素的影响呢?知道答案的可以在留言区回复哈,下一篇文章我们会详细说明。

-

放大器共模抑制比参数定义及影响电路共模抑制的因素分析2020-10-14 13796

-

一文详解运算放大器共模抑制比(CMRR)2023-02-12 7364

-

理解运放电路的共模抑制比CMRR2023-05-18 6582

-

高共模抑制比(CMRR)仪表放大器电路原理图讲解2023-08-09 6596

-

集成运算放大器电子教案2009-09-16 14601

-

AD-运算放大器共模抑制比CMRR2012-04-01 5307

-

运算放大器测试基础之自测试电路与双运算放大器测试电路配置2018-09-07 2630

-

放大器的电源抑制比和共模抑制比2018-09-19 6439

-

零漂移精密运算放大器的相关资料推荐2021-12-31 1344

-

放大器的共模抑制比的定义2009-04-22 2604

-

运算放大器测试基础第3部分:适用于运算放大器测试的电路配置2017-04-08 5919

-

网络变压器共模抑制比CMRR概念及原理2019-02-25 2580

-

MT-042:运算放大器共模抑制比(CMRR)2021-03-21 2053

-

仪表放大器共模抑制比怎么计算?2023-09-05 4819

-

什么是共模抑制比CMRR?什么是电源抑制比PSRR?2023-10-29 11581

全部0条评论

快来发表一下你的评论吧 !