分享跨分割设计对高速电路信号的影响

电子说

描述

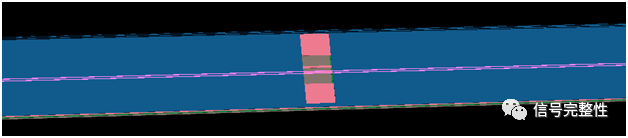

在高速电路中经常会遇到跨分割设计,在2017年的时候也写过一篇跨分割设计的文章。

今天给大家分享一篇跨分割设计对信号的影响。

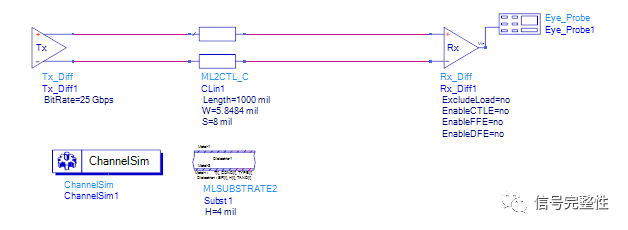

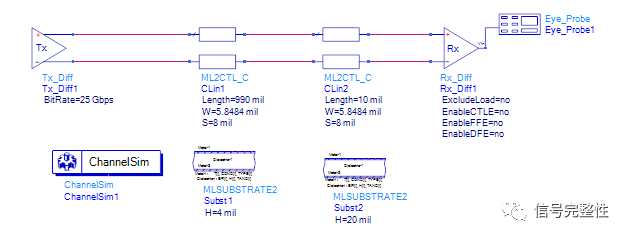

随着高速电路的信号速率也越来越高,那么在高速电路设计中是否也需要进行渐变线的设计呢?为了验证这个问题,特意在ADS中设计了如下原理图(为了说明问题的严重性,把信号的速率设置为25Gbps)。

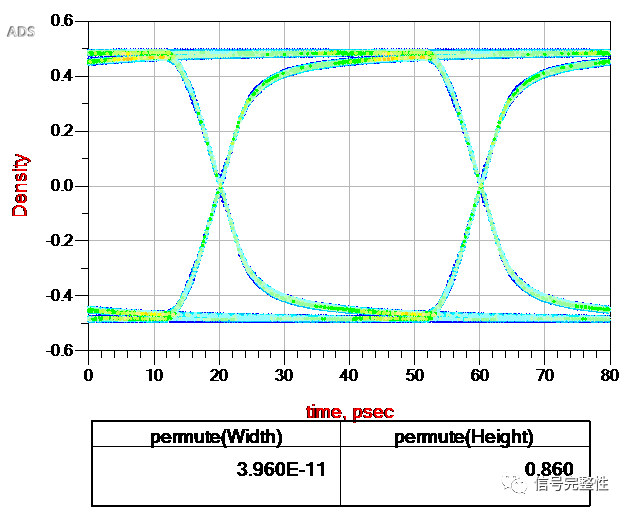

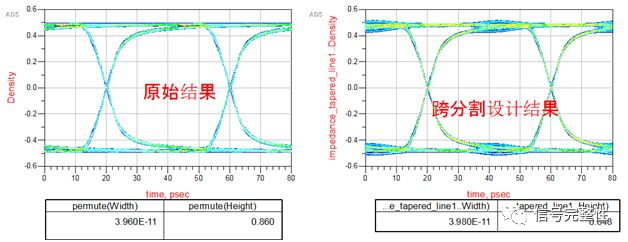

仿真得到的结果如下图所示:

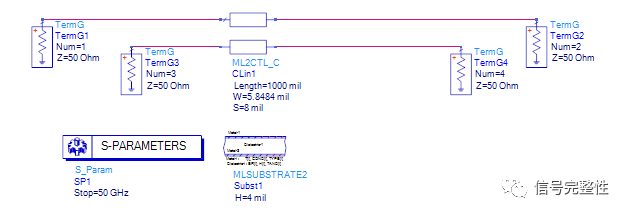

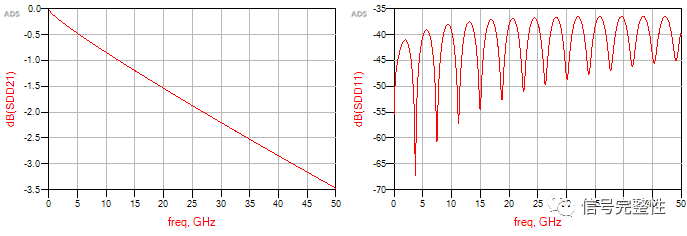

眼图的宽度和高度分别为39.6ps和860mV。再通过无源链路的仿真,获得其S参数的结果。其无源链路的原理图为:

其插入损耗和回波损耗的结果如下图所示:

为了表示其跨分割,加了一段新的传输线,修改了传输线到参考层的距离,修改后的原理图如下所示:

结果如下图所示:

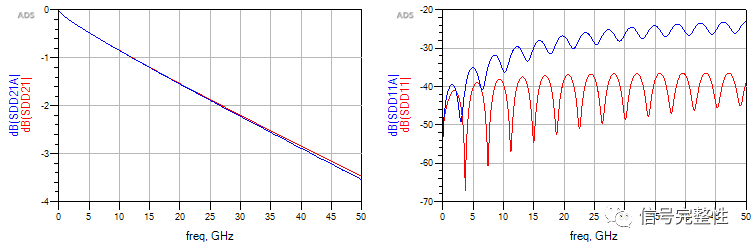

从上图的结果可以看出,在信号线只有10mil跨分割设计时,在25Gbps时,噪声和抖动都有增加。同样,仿真其无源链路的结果如下所示(蓝色的为跨分割设计的结果):

插入损耗的结果在25GHz之前几乎没什么差异,但是回波损耗的结果差异比较大。当然,由于跨分割的传输线比较短,其回波损耗也都在-20dB以下。

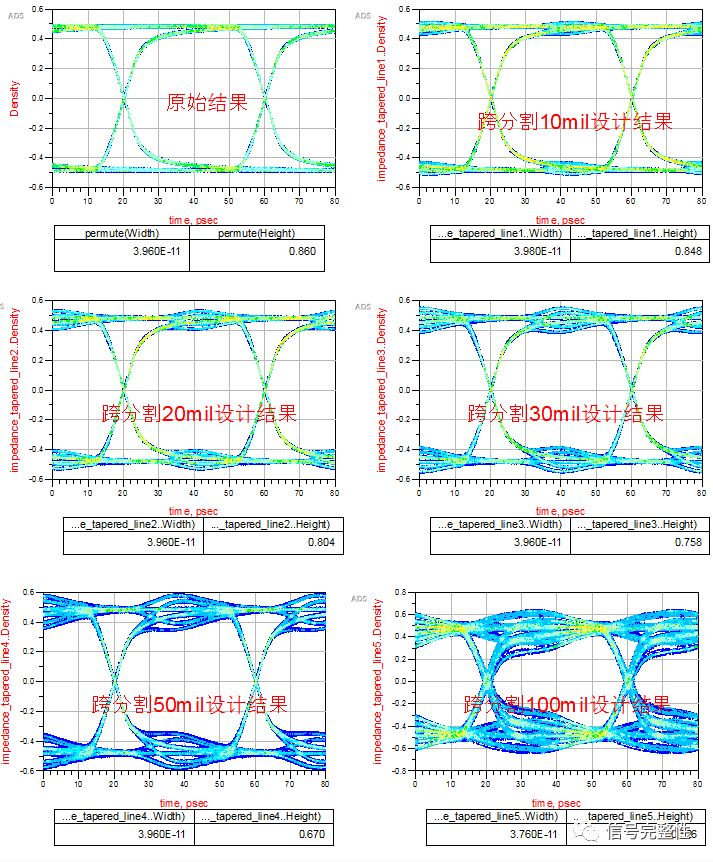

很显然,从上述的结果可以看到跨分割设计引起了实实在在的问题。如下是从通道有源仿真的角度,分别对不同跨分割的宽度仿真的结果对比:

总长1inch的传输线,在25Gbps的信号速率下,只要有跨分割设计,其信号都会受到影响。当然,当速率比较低速时,跨分割设计的影响也会小一些。

对于跨分割设计其它的相关研究,比如所跨分割时,传输线到参考层的距离、信号的速率、传输线总的长度等等因素,也可以研究跨分割对阻抗、损耗、串扰等的影响。由于时间和篇幅的关系,我就不做过多的赘述。有兴趣的工程师可以继续往下研究,也可以与作者进行交流。

-

手机板 layout 走线跨分割问题2025-09-16 5580

-

凡亿Allegro Skill布线功能-检查跨分割2025-06-19 1976

-

PCB信号跨分割线需要怎么处理?2024-01-10 2266

-

PCB设计信号线跨分割会有什么影响2024-01-03 1969

-

在高速电路设计中,如何应对PCB设计中信号线的跨分割2023-12-04 1507

-

高速PCB中的地回流和电源回流以及跨分割问题分析2021-04-25 2489

-

PCB设计中跨分割的处理2021-02-19 1685

-

PCB信号跨分割线怎么处理?2020-09-02 7856

-

什么是ICT测试点 PCB设计信号线跨分割的影响2020-03-08 6228

-

不管是高速电路还是射频电路,当微带线跨分割时信号将会引起什么样的问题2018-02-27 9125

-

PCB中的平面跨分割2016-10-09 9317

-

高速PCB中的信号回流及跨分割2009-11-17 1183

-

请教高手:关于信号线跨分割的问题2009-02-10 7641

全部0条评论

快来发表一下你的评论吧 !