瀚海微SD NAND之SD 协议(42)SPI总线时序

电子说

描述

SPI总线时序图

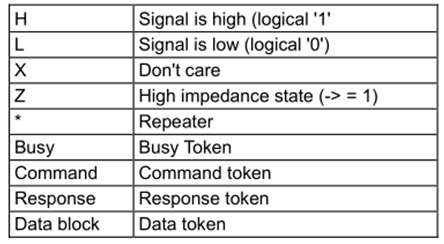

所有时序图使用以下原理图和缩写:

所有定时值的定义如表所示。

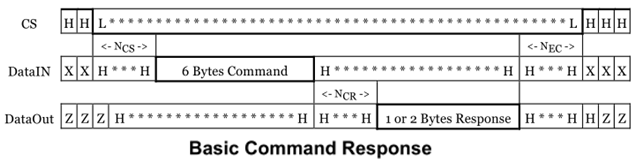

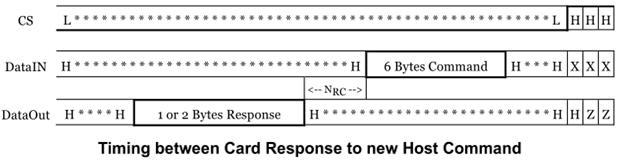

主机在收到卡响应后,应保持时钟运行至少NcR时钟周期。此限制适用于命令和数据响应令牌。

命令/响应

主机对卡的命令响应-卡已准备好

下面的时序图描述了基本的命令响应(无数据)SPI事务。

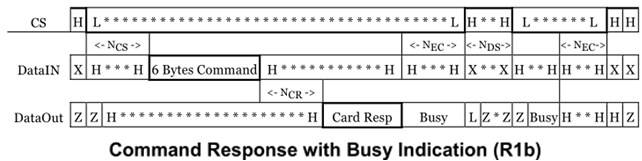

主机命令到卡响应卡忙

下面的时序图描述了R1b响应的命令响应事务(例如SET_WRITE_PROT和ERASE)。

当卡信号繁忙时,主机可以在任何时候取消选择它(通过提高CS)。

卡将释放数据线一个时钟后,CS走高。

要检查卡是否仍然繁忙,需要通过断言(设置为低)CS信号来重新选择它。

卡将在下降沿后一个时钟恢复忙信号(拉低数据输出)。

卡对主机命令的响应

数据读取

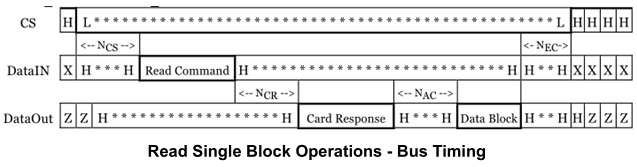

单块读操作的时序图下面是除SEND_CSD和SEND_CID命令外的所有单块读操作的时序图。

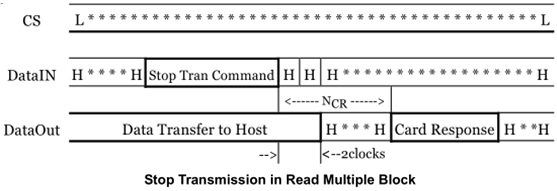

多块读操作的停止传输时间

下表描述了多块读操作的停止传输操作。

读数据块之间的时钟周期由NAC定义(如下图所示)。

为避免CMD12响应与下一个数据块发生冲突,CMD12的时序控制如下:

SPI主机应在CMD12结束位与数据块结束位重叠的时间发出CMD12。

如果(1)不可能,SPI主机应等待收到令牌(开始块令牌或数据错误令牌),然后在令牌发出一个时钟周期后发出CMD12。

在(2)的情况下,读到最后一个块后,主机收到数据错误令牌(out of range Error)。

但是,如果成功接收到数据错误令牌之前的数据块,则可以认为它是有效的。

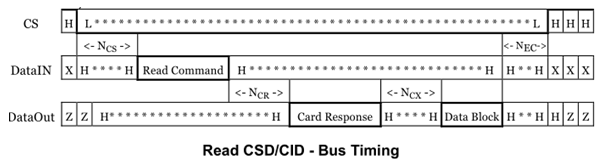

读取CSD或CID寄存器

下面的时序图描述了SEND_CSD和SEND_CID命令总线事务。

响应和数据块的超时值分别为NcR和Ncx(因为Nac仍然未知)。

审核编辑 黄宇

-

基于SPI协议的SD卡读写2016-01-06 1094

-

基于SPI协议的SD卡读写说明2021-03-17 1789

-

SD nand 与 SD卡的SPI模式驱动2023-05-10 3057

-

SD NAND和SPI NAND的区别2024-06-04 4124

-

瀚海微SD NAND之SD 协议(29)硬件接口2024-09-24 1504

-

瀚海微SD NAND之SD 协议(31)总线的信号和时序2024-09-25 920

-

瀚海微SD NAND之SD 协议(32)1.8V信令的驱动强度和总线时序2024-09-26 975

-

瀚海微SD NAND之SD 协议(36)SPI模式2024-10-08 1490

-

瀚海微SD NAND之SD 协议(37)SPI总线保护和读写2024-10-09 1460

-

瀚海微SD NAND之SD 协议(39)SPI模式 Transaction Packets2024-10-12 1224

-

瀚海微SD NAND之SD 协议(40)SPI模式CMD8的操作2024-10-14 1226

-

SD NAND、SPI NAND 和 Raw NAND 的定义与比较2025-01-15 2150

-

瀚海微SD NAND/TF卡——数据世界的全能搭档2025-10-13 583

-

瀚海微SD NAND/TF卡:赋能全场景数据存储,定义高效安全新基准2025-10-14 467

-

SD NAND 接口协议解析:SPI 与 SDIO 模式区别及适配方法2025-10-31 1704

全部0条评论

快来发表一下你的评论吧 !