基于Atlas的MFIS结构器件电学性能模拟设计

描述

近年来,由具有金属-铁电-绝缘层-半导体(MFIS)结构的铁电场效应晶体管(FeFET)组成的铁电存储器,以其非破坏性读出、存储密度高等优点,成为最具潜力的下一代非挥发性存储器件之一。MFIS结构作为FeFET的核心部件,其电学性能将影响到铁电存储器的存储能力和稳定性。在已有的研究中,研究者一方面采用实验方法研究MFIS结构器件的电学性能,另一方面试图从理论上对器件的电学性能进行研究。

本文将利用Silvaco公司的Atlas器件模拟软件,结合Miller等人的铁电极化模型及电荷薄片模型,对MFIS结构器件的C—V特性及记忆窗口进行模拟,讨论应用电压、绝缘层厚度及材料对MFIS结构器件的影响,探讨提高MFIS结构器件性能的有效途径。

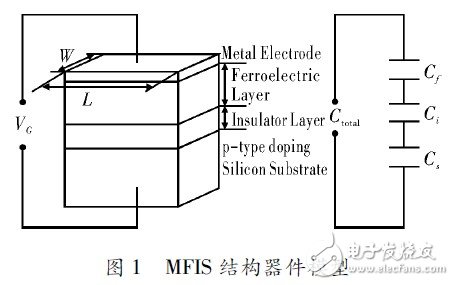

1 MFIS器件结构

MFIS结构是在传统MOS电容器的基础上,在金属电极和绝缘层之间增加具有极化行为的铁电材料,利用铁电层的极化行为进行二进制数据存储。图1为典型MFIS结构及其等效电路,铁电层厚度为df,绝缘层厚度为di。理想情况下,不考虑各层之间的界面捕获电荷、界面态及各层内部空间电荷和杂质的影响。电容器的上电极为肖特基接触,下电极为欧姆接触。基底采用均匀掺杂的p型硅,厚度达到要求。

2 模拟方法

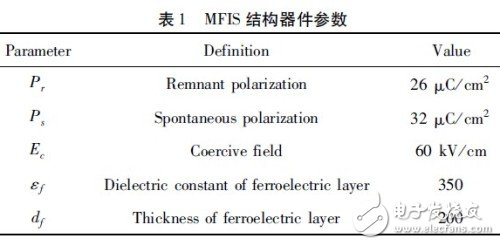

Silvaco公司的器件模拟软件Atlas,可以对二维和三维模式下半导体器件的直流、交流及时域响应等进行仿真和分析。为考虑MFIS结构器件中铁电层计划行为的饱和状态及非饱和状态,Miller等人提出的铁电极化模型被改进。在Model语句中引入两种状下的极化模型Ferro和Unsat.Ferro,器件的相关参数在Material语句中进行设置。由于MFIS结构器件在实际应用中多工作于高频状态,需要设置Ferro模型中Fer-roDamp参数为1。考虑到铁电薄膜、半导体基底及金属电极之间的功函数关系,MFIS结构的上电极和下电极分别被设定为肖特基接触和欧姆接触。铁电层采用BNT铁电薄膜,厚度为200 nm,其参数可以由文献中得到,具体参数如表1所示。

3 结果与讨论

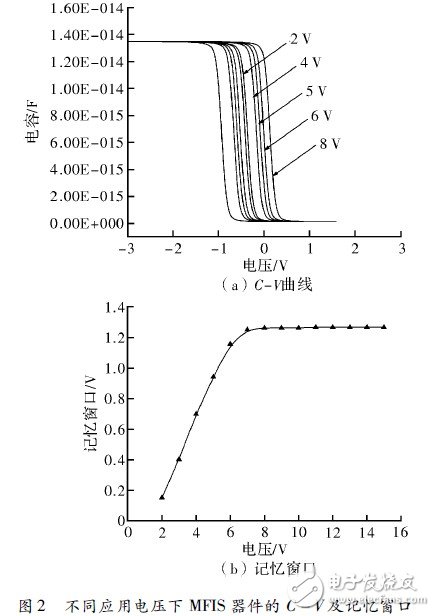

3.1 应用电压对MFIS结构器件的影响

应用电压的大小不仅能影响铁电存储器的存储能力及稳定性,还会影响到其与半导体集成电路的兼容性。图2中给出了不同应用电压下MFIS器件的C—V特性及记忆窗口。绝缘层为CeO2,应用电压从2V增加到5 V。由图中可以看出,由于铁电层的极化行为,MFIS器件的C—V曲线在不同的扫描电压方向上出现平移,呈现顺时针的回线状,并且其宽度随应用电压的增加逐渐变宽。MFIS器件的记忆窗口随应用电压的增加而逐渐增大,并在8 V时达到饱和。记忆窗口的大小直接影响着MFIS器件的稳定性。在较小的记忆窗口下,存储器的“0”和“1”两个逻辑态容易出现混淆,导致数据存取失败,因此适当增加应用电压,有利于提高MFIS器件的存储稳定性。

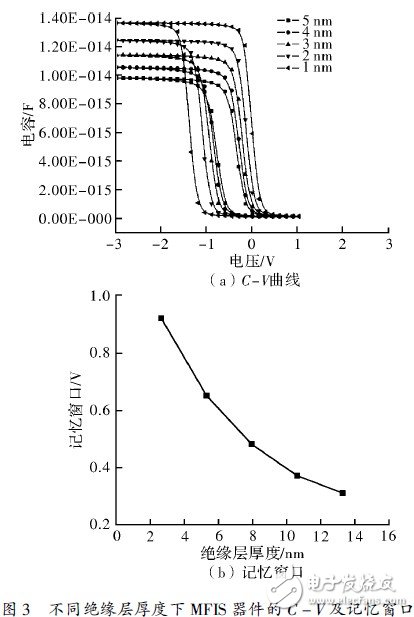

3.2 绝缘层厚度对MFIS结构器件的影响

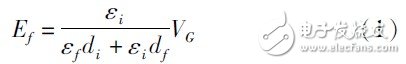

MFIS器件绝缘层的厚度会影响到MFIS结构的性能。图3中给出了不同绝缘层厚度下MFIS器件的C—V特性及记忆窗口。器件的应用电压为5 V,绝缘层采用CeO2,厚度从1 nm增加到5 nm。从图中可以看出,在一定的应用电压下,MFIS器件的C—V曲线随绝缘层厚度的增加变窄,记忆窗口随之减小,这与文献中报道的绝缘层厚度对MFIS器件电学性能的影响一致。这可以由加在铁电层上的有效电场进行解释。铁电层上的有效电场Ef为

其中,CG为应用电压;εf和εi为铁电层和绝缘层的相对介电常数。显然,铁电层上的有效电场随着绝缘层厚度的增加而减小,从而导致铁电层逐渐远离饱和状态,使得电容器的记忆窗口减小。

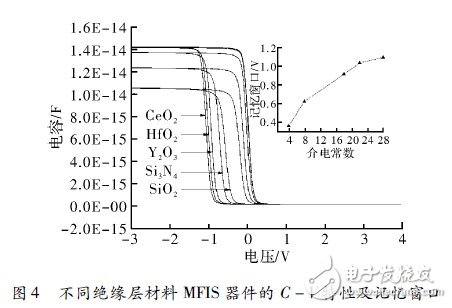

3.3 绝缘层材料对MFIS结构器件的影响

由式(1)可以看出,具有高介电常数εi的绝缘层,能够使分配在铁电层上的有效电场增加,从而使铁电层趋于饱和,产生一个较大的记忆窗口。为研究不同绝缘层材料对MFIS器件相关性能的影响,利用Arias软件对采用SiO2、Si3N4、Y2O3、HfO2及CeO2作为绝缘层的MFIS器件的C—V特性及记忆窗口进行了模拟和分析。

图4给出了在5 V的应用电压下,分别采用不同绝缘层材料时MFIS器件的C—V特性及记忆窗口。从图中可以看出,MFIS器件的C—V曲线随绝缘层介电常数的增加逐渐变宽,其记忆窗口从0.36 V增大到1.09 V,并逐渐趋于饱和。

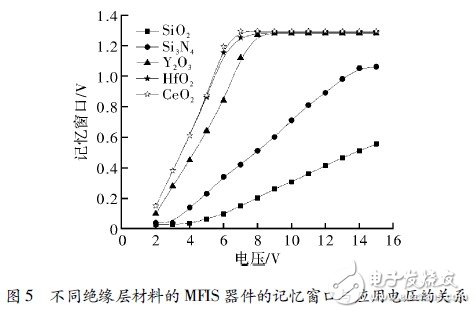

图5为不同绝缘层材料时MFIS器件的记忆窗口随应用电压的变化。从图中可以看出,高介电常数为绝缘层jf,MFIS器件的记忆窗口在7 V时达到饱和,而低介电常数为绝缘层时,记忆窗口在15 V时仍未达到饱和。这意味着在一定厚度下,高介电常数的绝缘层能够使MFIS器件的记忆窗口在一个较低的应用电压下达到饱和,从而减小工作电压,使得其与现代集成电路设计工艺相兼容。

4 结束语

利用器件模拟软件Arias,结合饱和状态及非饱和状态下的铁电极化模型,研究了应用电压、绝缘层厚度及材料对MFIS器件的C—V特性及记忆窗口的影响。仿真结果表明,增加应用电压、减小绝缘层厚度及采用高介电常数材料,可以使器件的C—V曲线逐渐变宽,记忆窗口逐渐增大。但是考虑到MFIS器件与现代集成电路的工作电压的兼容性,以及过薄的绝缘层可能会引起的漏电流,使得采用高介电常数的绝缘材料作为MFIS器件的绝缘层成为一个提高MFIS器件性能的有效途径。

-

陶瓷的微观结构和电学性能2025-01-23 1726

-

模拟设计中噪声分析的误区及注意事项2023-02-14 925

-

模拟设备高速转换器2022-07-18 545

-

LED器件的电学指标有哪几项2021-08-03 4731

-

模拟设计中的噪声误区2021-03-02 1846

-

模拟设计的原则有哪些2021-02-25 1487

-

PSoC Creator模拟设计:引脚放置的模拟及注意事项2020-07-01 4531

-

模拟设计中噪声分析误区2019-07-23 1996

-

Cadence教程之如何使用VieloSo模拟设计环境进行设计2018-09-20 1825

-

TI各种模拟设计工具介绍2017-10-16 912

-

求微电网模拟设计电路图和元器件清单,拜托了2017-08-09 3655

-

精密模拟设计中的噪声分析2017-01-14 1105

-

基于Atlas的MFIS结构器件电学性能模拟2011-07-13 2608

全部0条评论

快来发表一下你的评论吧 !