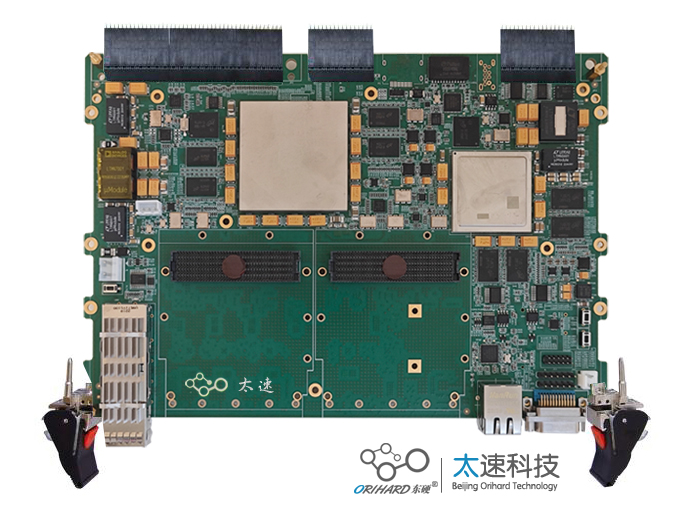

XCVU9P 板卡设计原理图:616-基于6U VPX XCVU9P+XCZU7EV的双FMC信号处理板卡 高性能数字计算卡

电子说

1.4w人已加入

描述

| 基于6U VPX XCVU9P+XCZU7EV的双FMC信号处理板卡 |

|

一、板卡概述 板卡基于6U VPX标准结构,包含一个XCVU9P 高性能FPGA,一片XCZU7EV FPGA,用于 IO扩展接口,双路HPC FMC扩展高速AD、DA、光纤接口等。是理想应用于高性能数字计算,光纤加速的板卡。 板卡全工业级芯片,满足高低温要求。  二、处理板技术指标 ● 主FPGA采用XCVU9P-2FLGA2104I; 从FPGA型号为XCZU7EV-2FFVC1156I; ● 主 FPGA外挂2组DDR4 ,每组64bit 宽度、8GByte容量;BPI flash加载方式,容量128MByte;1个I2C的 E2PROM;4个LED指示灯; ● 主 FPGA 外挂2组FMC HPC 连接器,都支持LA、HA、HB,8个GTY接口; ● 主FPGA与VPX背板P1互联16个GTY,P2互联8个GTY,P3 互联16对LVDS; ● 主 FPGA ,前面板 引出1路QSFP28,数据速率支持25GbpsX4, 时钟支持156.25MHz; ● 主FPGA,前面板J30J连接器(J14),JTAG接口,两收两发的GPIO_LVTTL3V3; ● 主FPGA(bank70)与从FPGA XCZU7EV(bank68)之间互联24对LVDS, 互联2个GTY (H)X 4; ● 从FPGA与VPX背板P2 互联8个GTH,P3互联16对LVDS,P6互联44个GPIO_LVTTL_3V3; ● 从FPGA与VPX背板P6互联1路千兆以太网(PL端),1路RS422(PL端); ● 从FPGA 板内PL端1组DDR4,64bit,2GByte容量;4个LED指示灯; ● 从FPGA 板内PS端外挂1组DDR4,64bit,2GByte容量; 2x QFlash,每片64MByte容量;1路EMMC,8GByte容量;1路SD卡,16GByte容量;1路msata接口; ● 从FPGA 板内PS端出1路调试RS232 (Uart0),2路Can接口于连接器J11; ● 从FPGA板后PS端出1路USB3.0,1路DP接口(VPX方案不使用); ● 从FPGA前面板出1路千兆以太网RJ45(PS端); ● 从FPGA前面板J30J连接器(J14),1路RS232或者RS422(PS端), 两收两发的GPIO_LVTTL3V3;JTAG调试口; ● 硬件连接支持从FPGA对主FPGA进行BPI模式加载。 三、软件系统 ● 提供主FPGA的接口测试程序,包括 DDR4、光纤aurora、PCIe、FMC等接口; ● 提供从FPGA的裸跑接口测试程序,包括 DDR4、RS232,千兆网 接口。 四、物理特性 ● 尺寸:6U VPX板卡,大小为160X233.35mm。 ● 支持导冷,风冷散热结构和把手安装。 ● 工作温度:0℃~ +55℃ ,支持工业级 -40℃~ +85℃ ● 工作湿度:10%~80% 五、供电要求 ● 直流电源供电。整板功耗 120W。 ● 电压:+12V 10A,纹波:≤10% 。 ● 支持外部独立电源接口J8;支持风扇接口 JP4,12V。 六、应用领域 软件无线电系统,基带信号处理,无线仿真平台,高速图像处理,光纤加速计算等。  |

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA 信号处理板卡设计原理图:618-基于FMC+的XCVU3P高性能 PCIe 载板2026-01-30 428

-

3U VPX板卡设计原理图:821-基于RFSOC的8路5G ADC和8路9G的DAC 3U VPX卡2025-12-18 589

-

XCVU13P板卡设计原理图:509-基于XCVU13P的4路QSFP28光纤PCIeX16收发卡2024-11-23 1968

-

基于6U VPX XCVU9P+XCZU7EV的双FMC信号处理板卡2024-11-07 2507

-

基于VU9P的4路 100G光纤 6U VPX板卡2024-09-29 2180

-

智能加速计算卡设计原理图:628-基于VU3P的双路100G光纤加速计算卡 XCVU3P板卡2024-08-01 1412

-

信号处理板卡设计资料原理图:613-基于6UVPX C6678+XCVU9P的信号处理板卡2023-10-16 3103

-

芯片验证板卡设计原理图:基于XCVU440的多核处理器多输入芯片验证板卡2023-09-12 2200

-

XCVU9P板卡设计原理图:613-基于6UVPX C6678+XCVU9P的信号处理板卡2023-07-20 2611

-

高速图像采集设计资料原理图第613篇:基于6UVPX C6678+XCVU9P的信号处理板卡2023-06-20 1754

-

612XCVU9P板卡设计资料原理图:基于XCVU9P的32路光纤PCIeX16收发卡2023-01-06 1302

-

光纤加速卡设计方案原理图第410篇-基于XCVU9P+ C6678的40G光纤的加速卡2022-08-29 2287

-

高性能6U VPX高速信号处理平台2016-04-07 3677

全部0条评论

快来发表一下你的评论吧 !