电源芯片耗散功率与结温关系的探讨

描述

以下文章来源于慧智微电子 ,作者小慧

01如何仅通过EM仿真SNP文件获取传输线特征阻抗?

Q:请问目前通过EM仿真得到传输线的SNP文件,仅有这个的情况下能仿真得到传输线的特征阻抗吗?

A:一般来讲,只在这个端口加Term,然后设置这个Term的阻抗为Zo, 之后扫描Zo, 看什么时候,这个端口的反射系数最小。这时候的Zo,就是特征阻抗。(但是需要考虑其它的端口怎么连接 -- 这是一个问题)。如果是两端口,两个端口的连接传输线是一样的。那就加两个Term, 两个Term的阻抗都设置为Zo.....

Q:好的,谢谢你,我这就去试试。

02电源芯片耗散功率与结温关系的探讨

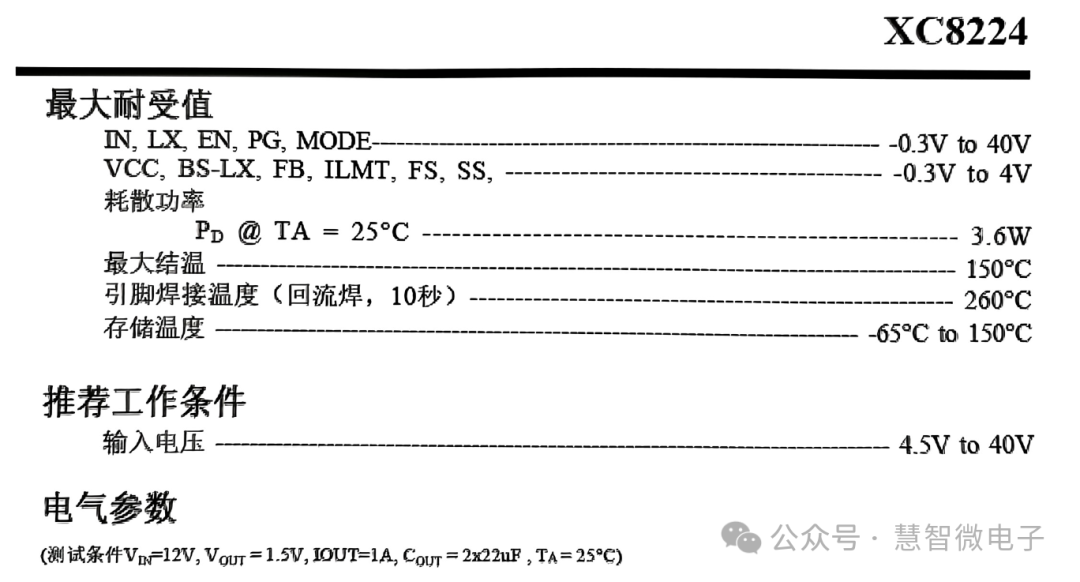

Q:请问下有人了解,电源芯片这个耗散功率是在结温150°C下算出来的吗?

A:不是,超过结温,pn结损坏。

Q:那他这个耗散功率是,结温多少的时候测出来的?

A:最大结温一般是晶元厂测出来的吧。实际上使用器件也不关心结温多少,也很难测出来。只要散热够好就ok。做什么产品啊,这么纠结功耗与结温的关系。

Q:因为他只给了个耗散功率,想算他的热阻,之前一版85度时电源自保护了,所以想先预算一下。

A:你说的这个 耗散功率 应该是 满载工作时的最大热耗。

可靠性考虑,半导体芯片针对 结温(TJ)规定了安全上限,通常为150°C(有时为175°C)。

裸芯片,结温可以用 显微红外热像仪测试。封装好的芯片热阻,可以用热阻测试仪(如t3ster)测试。

Q:好的,谢谢,多找了几份规格书反推了一下,有的是125度,有的是150度。所以按150度推算热阻系数保守一点。

03包络阻抗、基波阻抗与二次谐波阻抗的差异

Q:请问大家一个问题,包络阻抗是什么意思,和我们的基波阻抗,二次谐波阻抗区别在哪?

A:我理解包络阻抗应该是双音信号或宽带信号才有的概念,基波阻抗和谐波阻抗不论单音双音和宽带都要考虑。譬如有两个双音信号f1和f2,那它们的包络阻抗就是(f1-f2)和(f2-f1)频点处的阻抗,是宽带信号记忆效应的主要来源,可以参考下慧智微公众号之前有篇讲记忆效应的文章。

Q: 好的,谢谢哥,我看下文章。

04功率检测器指标与插入损耗的关系

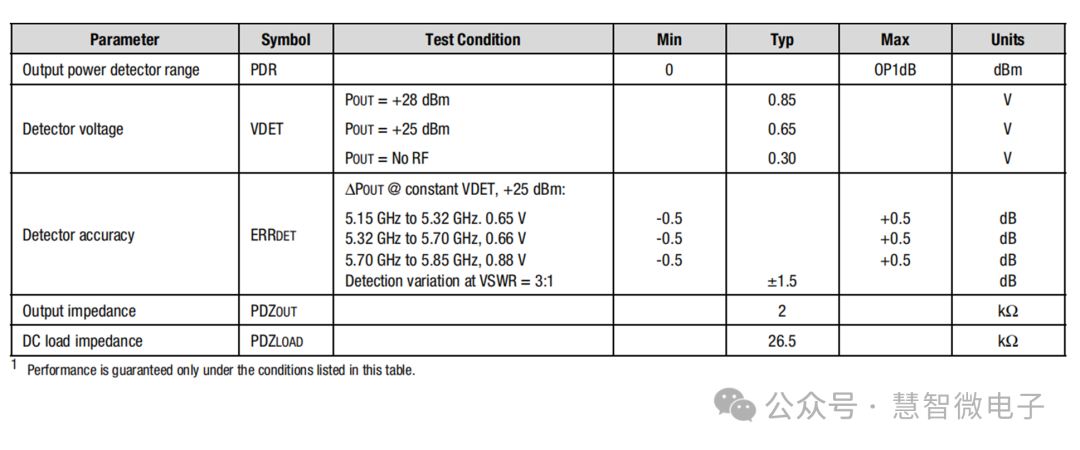

Q:有人了解功率检测器指标吗,这个检测的准确度(dB)是对主路的的插入损耗吗?

A:图片里这是耦合功率再经过检波电路后的规格。

“有人了解功率检测器指标吗,这个检测的准确度(dB)是对主路的的插入损耗吗?” 这里的检测准确度应该是这样理解:在检测电压为0.65v时,对应的输出功率在25dBm+-0.5dB。

Q:一下子就懂了,感谢大佬。

05电源线对ACLR影响分析及改进措施

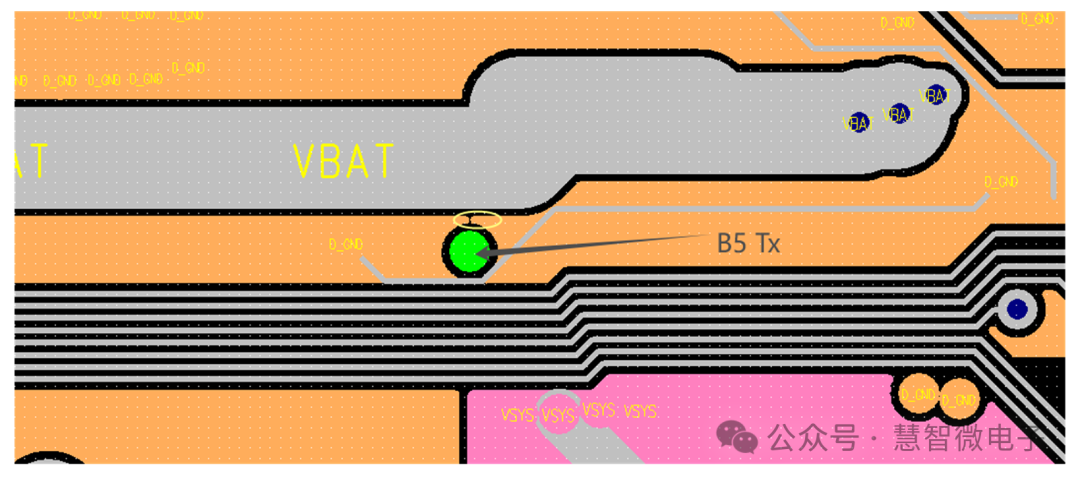

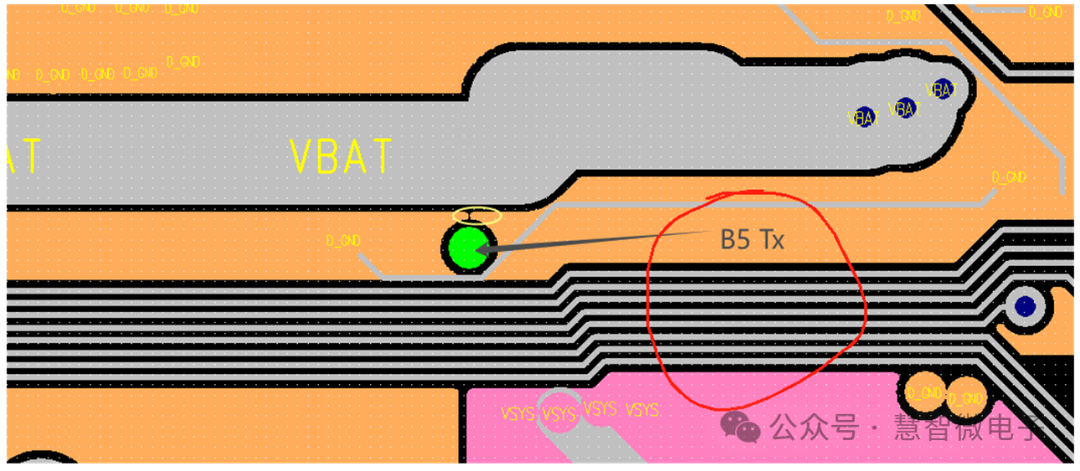

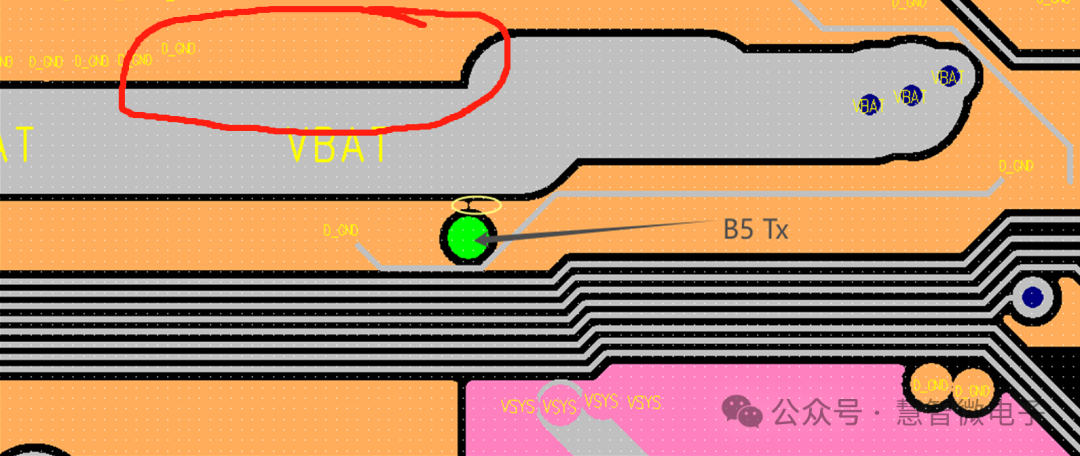

Q:B5 Tx走线这里包地没做好的话,会被影响到ACLR吗?

A:会,靠电源这么近的嘛,要多打低孔了哦。

Q:ACLR直接掉到20了。

A:这些是什么线?

A:旁边电源啊。

A:不会有耦合吗?

就算地连起来了也会有影响,VBAT线应该可以网上移动一点,然后中间打地孔呢。

Q:ok,叫人改一下,感谢大佬。

A:记得电源线和那个孔之前一定要用地孔隔开,要不还会被影响

Q:好的,为啥会被电源线影响啊?B5Tx 800MHz。

A:电能转磁能呗。

A:电源有噪声。

Q:是把E-UTRA 1的底噪抬太高了吗?

A:不是底噪。差的电源在被抽取电流的时候,会产生纹波。

Q:多谢大佬们解惑。

06功率检测电路设计与仿真中的关键因素探讨

Q:有人了解功率检测电路的运行规则吗?是不是 PA 正常工作的时候不开启,当 PA 出现异常就检测功率(。・ω・。)?

A:回环检测功率,CLPC校准,WIFI是这么用的。

Q:太深奥,没太明白。

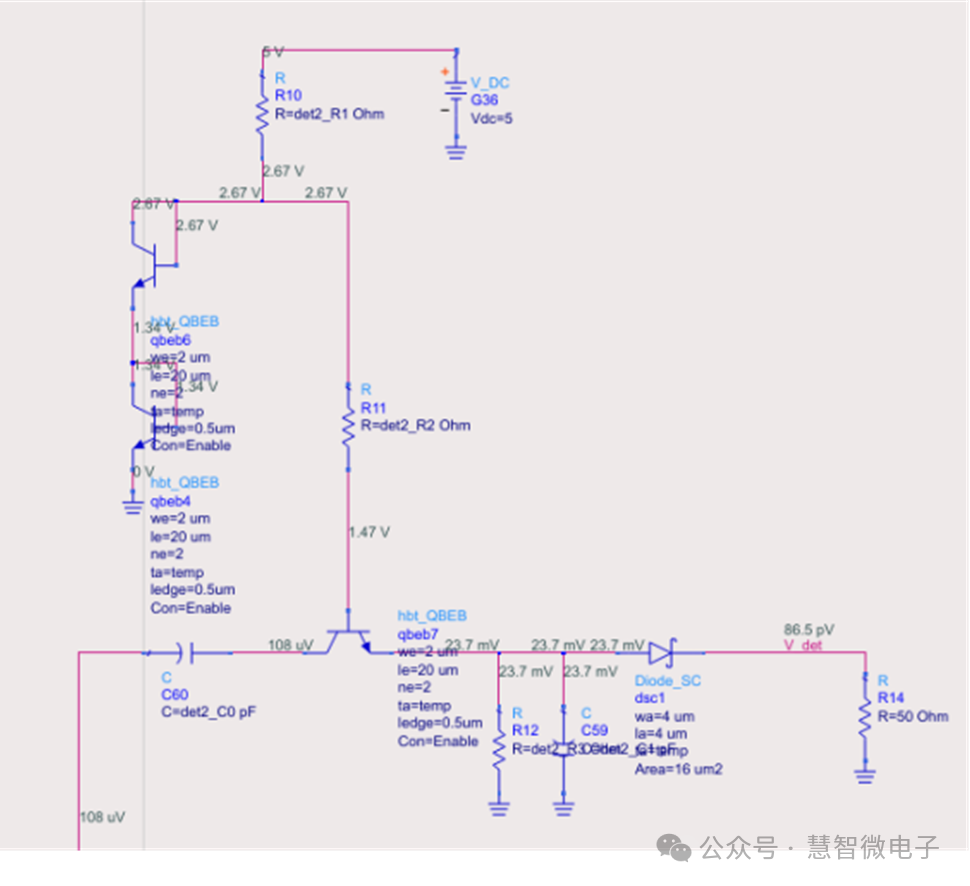

A:你就当这个det当成一个二极管。

Q:但设计的时候,不需要考虑检测电路对这个的影响吗?我仿真出来,加了检测电路直接调了几个 dB。

A:那说明det吸收的功率太大,电路问题。

A:检波器吗?检波器的话可以耦合一个线圈出来。

Q:这是我参考的电路,主要的影响还是这个耦合电容的问题,电容太小,检测的电压变化不大,电容太大,检测的电压正常,但对主路的影响很大。

A:主路耦合出来。

Q:耦合电容不行吗?

A:做检波器是为了做包络跟踪吗?

Q:wifi-pa 的功率检测,是不是包括跟踪的话,不是特别清楚。

A:一般0.5dB,放在级间。

Q:我是吧级间和这个放在一起仿真,但损耗太大了,要不就是检测的功率,不太对。

A:电路问题,自己想想。

Q:有没有那种讲关于这个功率检波电路的资料什么的,感觉我现在已经晕了。

A:有个log det的。好像,ieee搜一下。

Q:okok,多谢大佬。

07ADS模板仿真FT与Fmax遇到的问题及解决方法

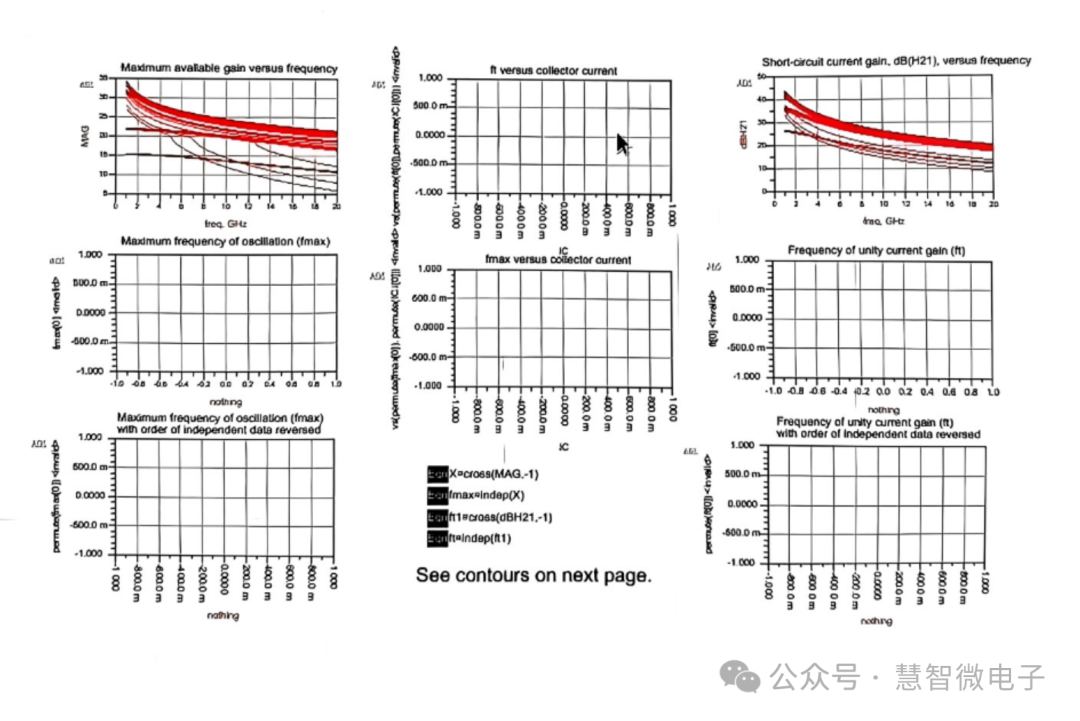

Q:有大佬用过ADS模板仿真ft与fmax,替换掉原来bjt,后没有仿真结果呢?

A:好好研究,没啥问题。

Q:啊?

A:看看下面的公式,分析下ADS怎么仿真ft和fmax的,你就知道为啥没数据了。

Q:嗯嗯好嘛,从这个X开始就没数据了。

A:哎,你把原理图的频率设置高一点,300g。

Q:好嘛,多谢多谢。

08如何在芯片测试中去嵌PCB影响并精确评估芯片性能

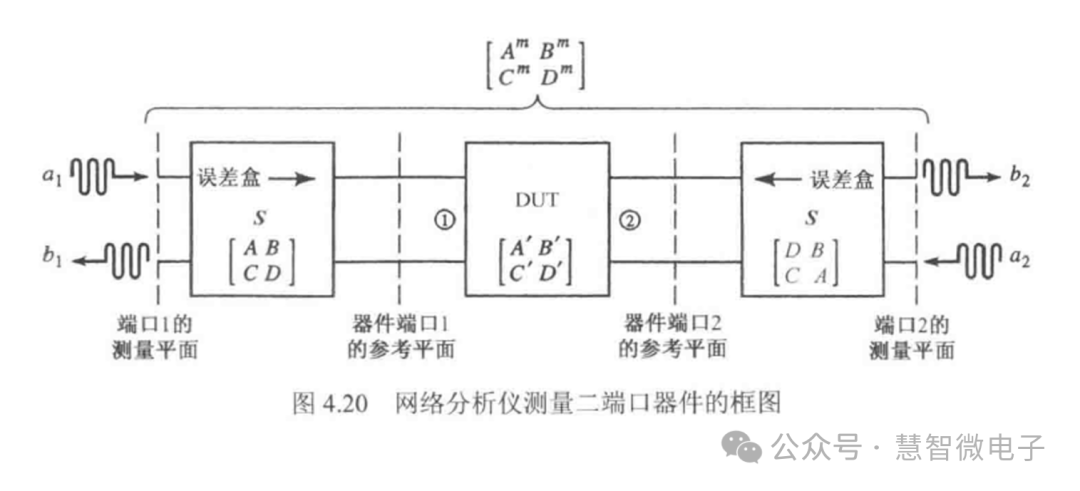

Q:咨询一下各位大佬,一般芯片测试都是要焊接在PCB上去测试,但这会引入PCB的影响(比如损耗等),怎么能在测试中尽可能去除PCB的影响、只考察芯片本身的性能呢?

A:去嵌,你可以在你测试的PCB上做TRL校准的校准件 然后测试的时候用TRL校准去嵌就可以测试到芯片端面了。

A:去嵌入,AFR会方便一点。

Q:类似于这样的原理是吗?PCB板相当于这里的误差盒?

我看《微波工程》这里讲TRL校准是可以将校准件和被测件级联,就是构造成3个二端口网络的级联,但实际的芯片是和PCB板焊在一起(PCB板上还可能有接地通孔),我就是不懂那这样的话PCB板怎么做校准件呢?

A:一般会按照PCB专门做一块校准板。

你这种夹具不好拆装的,那就是做前处理比较合适,做个TRL校准板。

Q:哦哦,好吧感觉我自己好像想复杂了。

A:你要做一块一摸一样的pcb做你的校准件的,国外好像有人专门做这个的。

A:看看xiaoning ye的文章吧,讲的很清楚。

Q:好的多谢各位大侠。

09负载牵引与功率效率圆分析及匹配策略

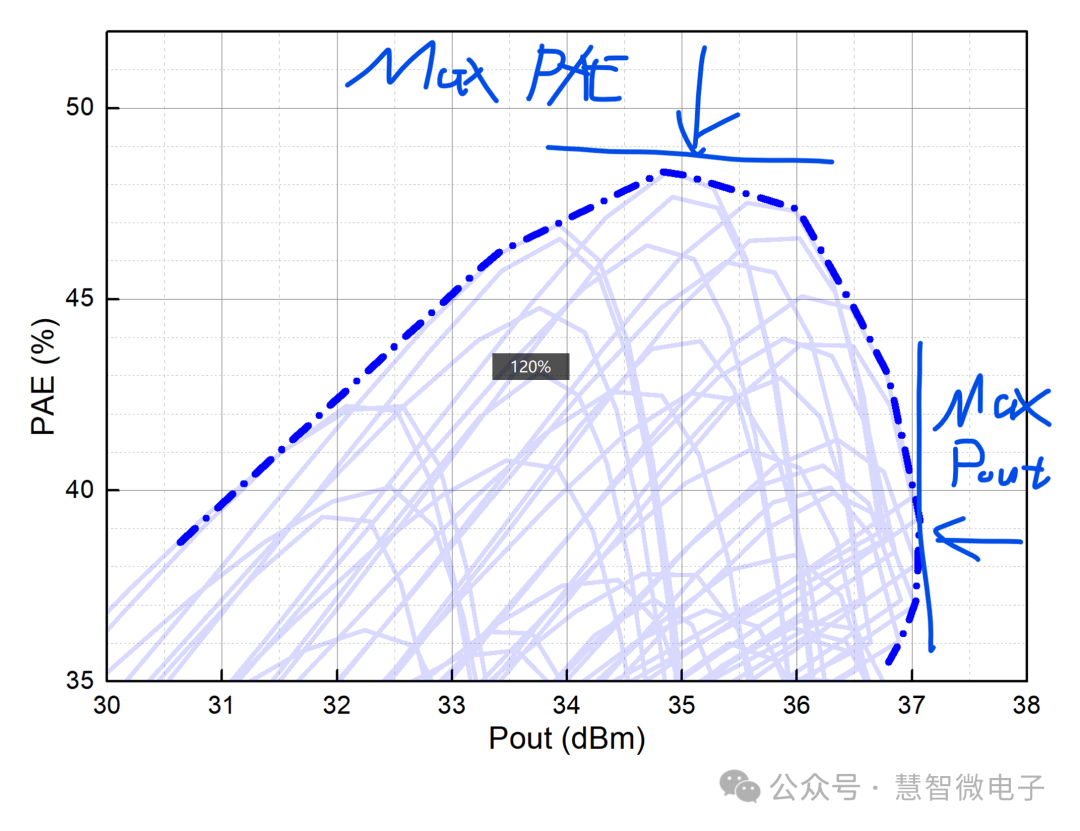

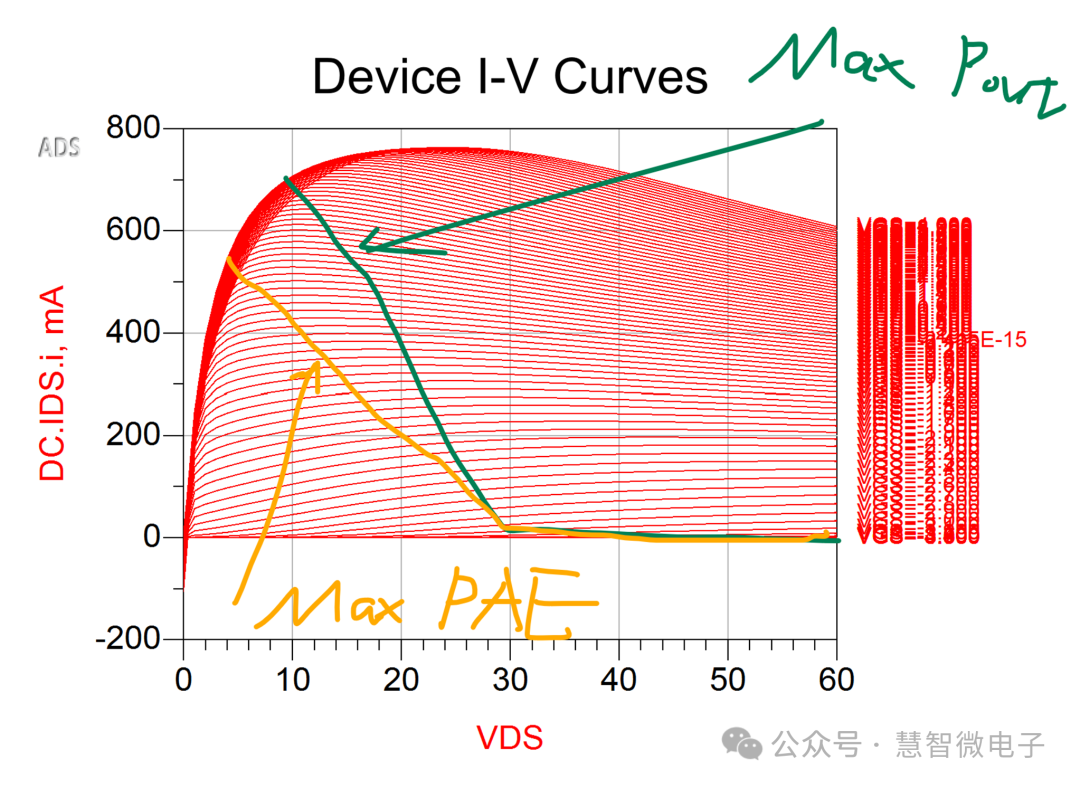

Q:求问:负载牵引得到的功率圆和效率圆为什么会错开,而不是重叠在一起。

A:好问题!

A:膝点电压吧?

A:对的。

Q:可以展开一下吗?大佬

A:从负载线的角度考虑呗。

Q:这个膝点电压和模集里的过驱动电压是一个意思么?

A:显然不是。

Q:应该是i-v曲线里的那个Vknee吧?

A:膝点电压是Vds的电流开启电压,过驱动电压是Vgs的电流开启电压。

A:就是功率管从线性区进入饱和区的拐点电压。

Q:前辈能详细讲讲吗?效率和功率圆怎么分析的。

A:那这数值上不就是过驱动电压么,就是饱和区那个分界电压呗。哦没事了,CMOS对线性饱和区的定义和模电不一样。

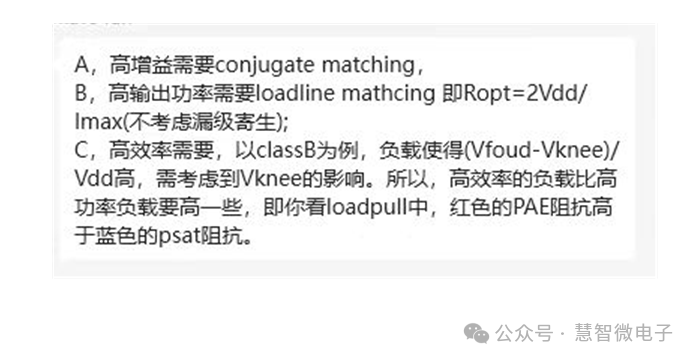

A:负载线匹配得最大功率,共轭匹配得最大效率,牵引的阻抗不同,在Smith圆上的位置不同。

A:共轭匹配不是最大功率传输吗?还是我记错了。

Q:不是吧 共轭匹配不是s11 s22最好吗?

A:是最大功率传输,所以增益应该是最大的。

A:共轭是让功率最大化传输。

Q:嗷嗷 但是小信号增益最大的话 输出功率也会最大吗?

A:不会啊,这个共轭的阻抗大概率不是loadpull负载线出来的Zopt。

A:Zopt应该是最大功率。

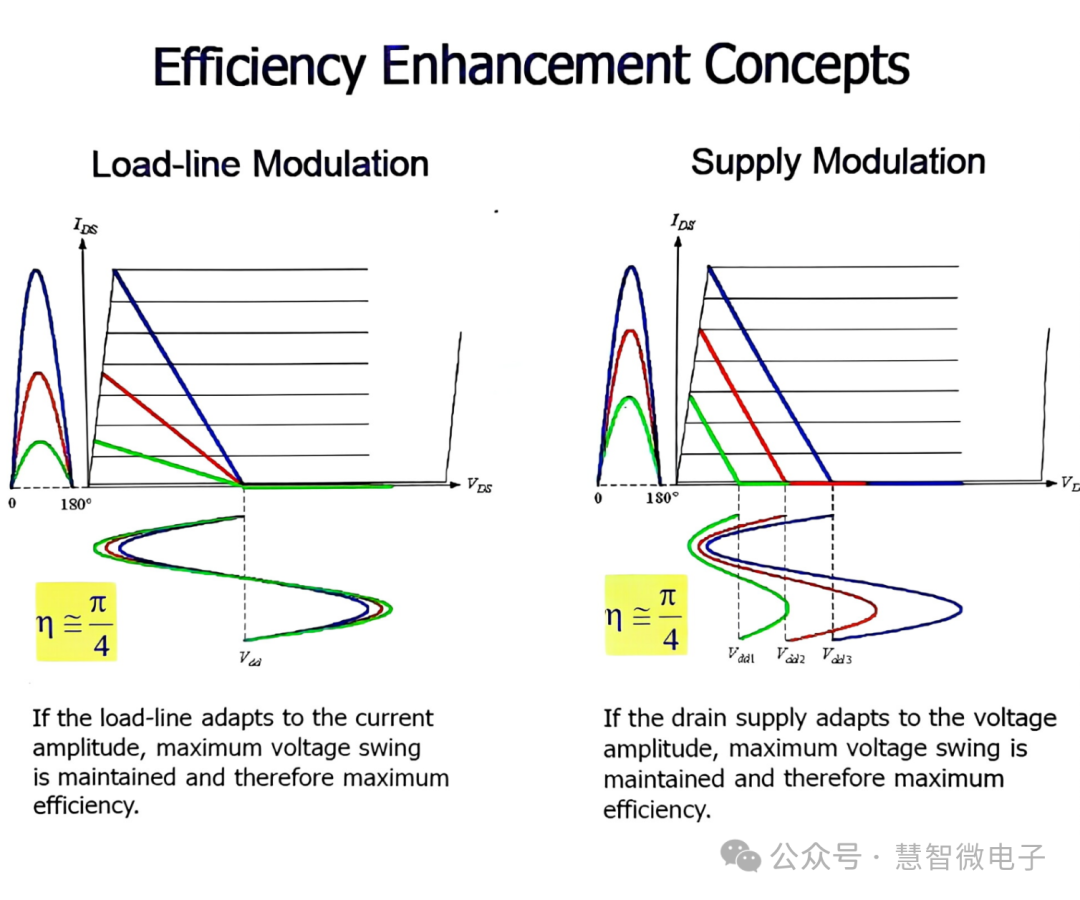

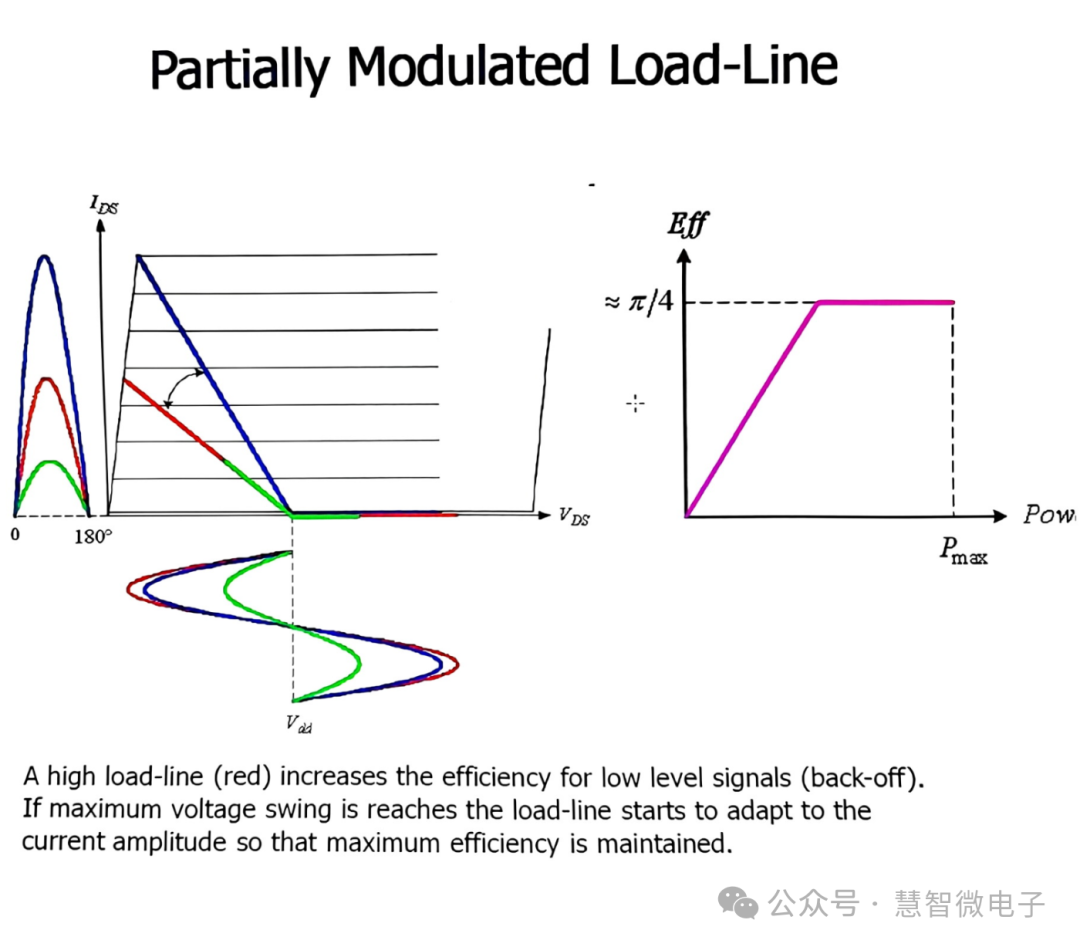

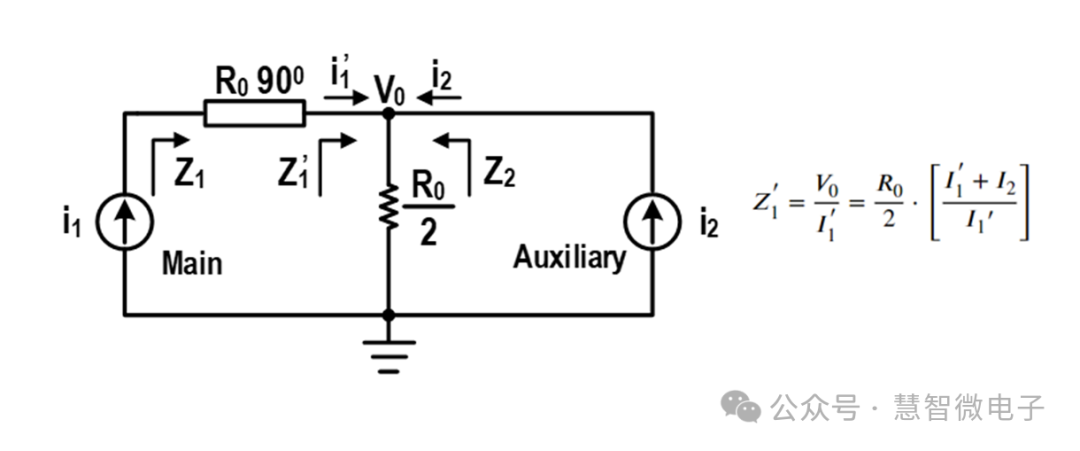

A:解释功率圆心和效率圆心不重合的原因:

A:之前看到的一张图:

Q:对于单级PA,高功率=高增益吧;power match获得的最大输出功率点,就是最高增益点?所以这里的A和B说法有矛盾吗?当然,高功率不等于高效率;

A:这张图很明显了,

这就是负载调制

看了一下12年,NXP给我们的培训资料。

Q:是的,这张图上,小功率下,共轭匹配下增益和输出功率比power match的要大;但是饱和输出时,比不上power match的输出功率;

A:个人理解负载调制是个广泛的说法,这里的调制和doherty的负载调制不是一个东西。

A:简单来说,负载调制就是电流源控制电压源端口看到的负载。

A:最大功率和最大PAE的圆心一般不会重合的,这个图就能说明问题。

A:因为PAE考虑了增益,而功率就只考虑了功率本。

A:对滴。

A:单级负载牵引增益对效率还是有点影响,有可能某个阻抗点的增益高输出功率也比最大功率小不了多少,那那个点的效率就比最大功率点的效率高。

A:是这样滴。

A:强。

A:老司机啊!

A:谬赞了各位,我只是之前想过。

10自行设计片内电感能否优化尺寸和Q值?

Q:有自己画过片内电感的同志嘛,请问自己画的同样感值的情况下能否比pdk自带的面积小些,Q值高些?

A:什么频段的?低频的话好像用pdk里的说不定更准些。

Q:2.4G,Pdk里的面积好大啊,tsmc65nm中电感外面还包围着其他东西。

A:可能就是因为这样才准吧 pdk自带了一些处理,自己绕应该也可以,不过可能自谐振频率会比较低 看形状和线宽了,应该有几nH了吧。

Q:3.5n,Pdk的感觉也不是很准,和理想的ind和R串联的模型不是很等效。

A:看你带宽多少了,自己绕一个也行。

Q:带宽80M,蓝牙频段。

A:有没有可能是你这个等效太简单了,肯定pdk的准啊20G以下都是实测出来的数据。

Q:啊,这样子啊,那我打算用片外的了。

A:实际电感的等效模型很复杂的。

Q:是的,跟我算的有差距。

A:你也没考虑寄生电容吧?

Q:没有的,我就用串联电阻等效的。

A:那么长的线圈走线寄生电容也不小的,片外的话就得考虑键合线的影响。

Q:感谢各位,Q值大一些就行,我主要是Q值对我的电路影响太大了,片内的3.5n的电感Q值才14.5,面积还贼大356×365。

A:那就片外其实这个频率片上电感能有十几的Q就不错了,线宽都得二十um吧。

A:片上电感Q值15基本极限了。

A:那不至于,毫米波能20+。

A:对Q值要求很高,用键合线比较好。

Q:电感小一点能15以上,电感越大Q值越小。

A:pdk里能有14.5已经不错了。

Q:是的。

11在谐波测试中,是否需要使用外部滤波器来滤除主频?

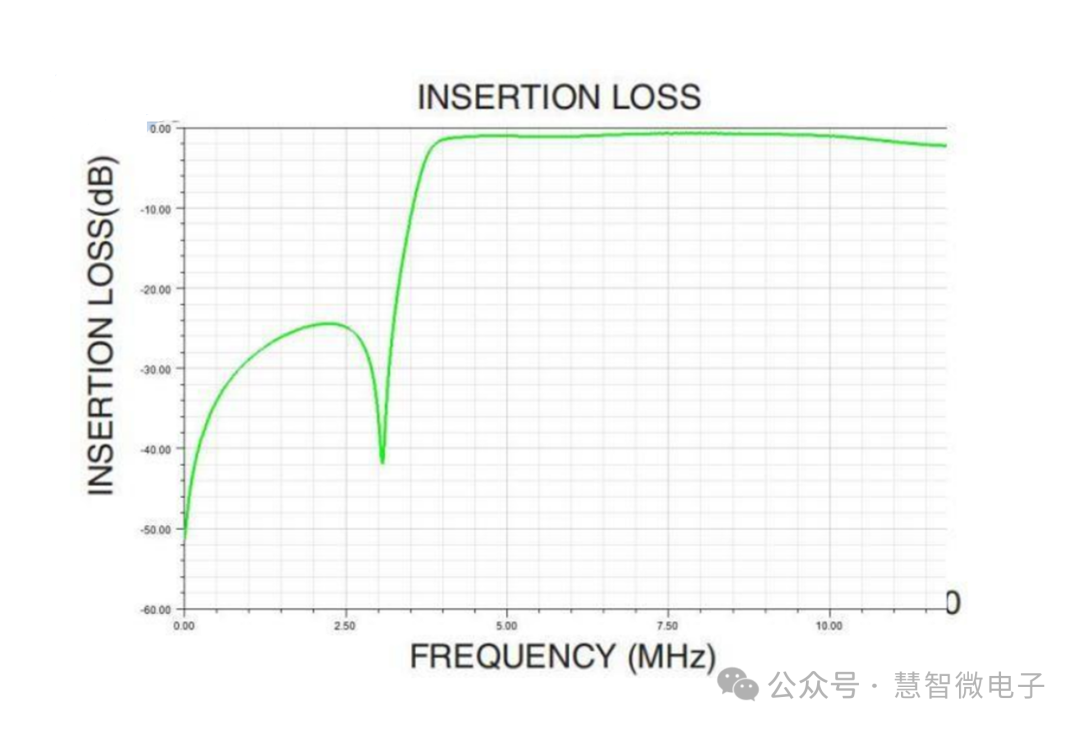

Q:请问各位老师,在做谐波测试时,是否需要在频谱仪前使用外部滤波器,把主频滤除掉?按道理频谱仪里面也有滤波器,用外部滤波器测试前后,谐波差异30dB,是不是可以判断主频的确在频谱仪里面混出谐波了?

这是我用到的高通滤波器。

A:主频肯定要滤掉的,不然主频进到频谱仪里面,产生非线性,这个谐波能量就不一定是你这产品产生的,有可能是频谱仪带来的。如果你的主频功率大,进到频谱仪里面,过载也会产生很多非线性。

A:单机+高通滤波器,中间最好再加一个隔离器。

Q:我的主频是2.4G,频谱仪只打4~8G看谐波,依然会有主频在频谱仪里面混出谐波意思是频谱仪里面的滤波器,在Freq Range里面并不能完全把主频能量抑制吗?谢谢各位老师

GPT还是需要改善呀

测试谐波时,需不需要加高通滤波器,把主频滤掉?

测试谐波时,通常不需要加高通滤波器来滤掉主频信号。谐波是指在电力系统中,由于非线性负载的存在,电流和电压波形发生畸变,产生频率为基波频率整数倍的额外频率分量。这些频率分量就是谐波。

在测试谐波时,我们通常关注的是这些额外的频率分量,而不是基波频率分量。因此,测试设备(如频谱分析仪、谐波分析仪等)本身就会包含高通滤波器,用于滤除基波频率以下的信号,只显示谐波频率分量。

高通滤波器的截止频率设置通常会高于所关注的谐波频率范围,以确保只显示谐波分量。例如,如果关注的是50Hz电网频率的谐波,高通滤波器的截止频率可能会设置在50Hz以上,比如100Hz或更高。

在实际测试中,确保测试设备正确设置,并选择合适的谐波分析功能,就可以直接获取谐波频率分量的信息,而不需要额外添加高通滤波器。

所以说,在做RE,RSE等认证测试时,是需要增加陷波器,把主频滤除,以免在频谱仪中混出其他杂散频点对吗?

A:有条件最好用腔体的带阻滤波器。

A:GPT回答的这个,滤波器应该不能覆盖到你这种高频的吧?这个就只陷掉主频,窄带陷波器,其他的高低频杂散才能看到,如果用高通滤波器,低频的杂散就看不出来了。

A:频谱仪主频不饱和的前提下 动态也有80左右,你是谐波抑制很大的话 需要滤掉主频再看,频谱仪里面按频率划分为几段 ,频率低的只有低通 ,其他段有YIG电调滤波器,最好是不指望用频谱仪的。

Q:明白了,感谢各位的指导!

-

什么是耗散功率?2025-07-31 1308

-

如何计算电源方案的耗散功率?2021-03-17 2993

-

如何去测量功率器件的结温?2021-03-11 2981

-

如何计算MOSFET的功率耗散2021-01-11 2484

-

如何准确测量到功率器件内部硅片的结温?2020-10-19 5001

-

详解芯片的结温2019-09-20 30046

-

MOS管耗散功率的计算2019-06-18 70532

-

结温计算与低热阻LED探讨2017-09-18 1072

-

芯片热阻计算/热与结温的关系2011-11-14 9055

-

晶体管耗散功率,晶体管耗散功率是什么意思2010-03-05 9109

-

利用仿真来估计功率半导体的结温2010-02-05 779

全部0条评论

快来发表一下你的评论吧 !