明明我说的是25G信号,你却让我看12.5G的损耗?

描述

高速先生成员--黄刚

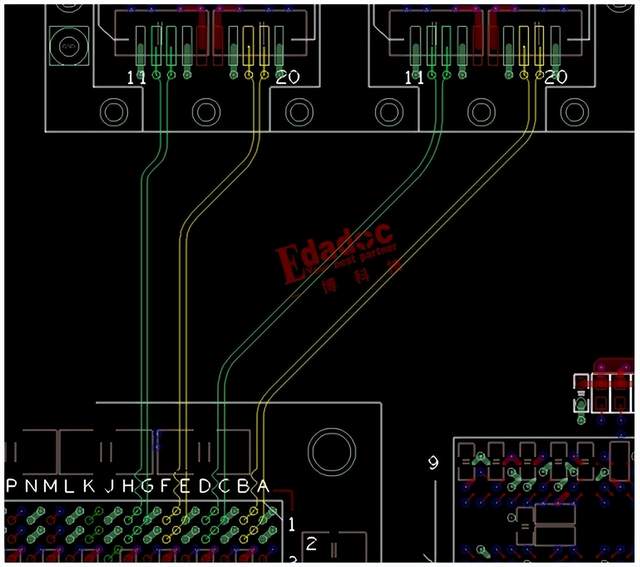

关于高速信号损耗要看哪个频点的问题,高速先生真的一年都要被咨询几十次!还是以我们比较熟悉的25G光模块信号为例子来开始我们今天这篇文章吧。下图是一个简单的25G光模块的PCB设计,从芯片到光模块连接器这一段链路,也就是我们高速先生常常称为host的光模块链路。

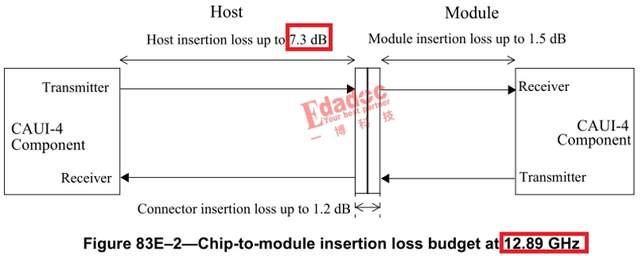

一些找我们仿真的客户也想了解下这种信号在PCB走线长度方面能允许的损耗值,由于高速先生都比较熟悉信号协议,就三下五除二脱口而出:12.5G是7.3dB。客户听完都会有这样的反应:等等,我说的是25G的信号哦,你告诉我12.5G干嘛?

是的,高速先生还真没弄错,一般这个时候我们就会直接拿出协议给客户看。吶,就是这样子的咯:12.89GHz(64B/66B编码方式,会多一丢丢),7.3 dB!

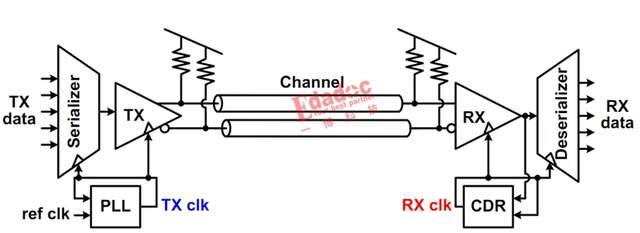

咋就不是25GHz啦,变成了12.5GHz?真的有点难理解。没关系,高速先生今天争取把这个事说明白哈!首先,我们还是从理论来说,我们这里提到的25G和12.5G其实不是一个概念。25G是说这对差分信号的传输速率,单位是bps,也就是我们常说的比特率。而协议上12.5G指的是频率,单位是Hz。那么重点来了,25G信号的bps和12.5G的Hz之间有什么关系呢?我们先看下面这个高速串行链路的示意图:

在上面这条典型的高速串行链路的示意图中,除了我们所关心的channel,当然离不开收发芯片模块。可能大家会觉得奇怪,为什么像DDR这种并行信号在数据传输时,时钟信号一起发送,也就是时钟信号会对数据信号进行采样,并且在原理图和PCB设计上都能看到实实在在的时钟信号的身影,例如和DQ信号一起等长的DQS信号。而高速信号就只是看到一大把的TX和RX信号呢?

其实这只是表象哈,像DDR模块这种叫源同步时钟系统,也就是时钟在伴随着数据信号一起发送,所以我们肉眼可见。但是高速信号采用另外一种更隐蔽的模式,叫嵌入时钟。也就是说时钟信号内嵌在高速数据信号里通过高速channel一并收发了,没有单独的时钟信号线。它是怎么做到的呢?举个例子哈,例如PCIE信号,当然有很多TX和RX的高速链路,不知道大家有没有注意,其实还有一对参考的时钟。没错,就是100MHz的那对。在高速信号发送过程中,发送芯片里有一个叫PLL(锁相环)的模块,会采样100MHz的时钟后进行倍频,倍频到可以采样到高速信号的频率,然后时钟内嵌到数据通道中一起发送,到了接收端之后,又有一个新的模块叫CDR模块,中文名叫时钟恢复模块。它主要是负责从收到的数据信号中恢复出内嵌的时钟,并用恢复出来的时钟对数据信号进行采样识别。

行吧,听不懂也不要紧,我们用一个具体的仿真链路给大家展开说说。

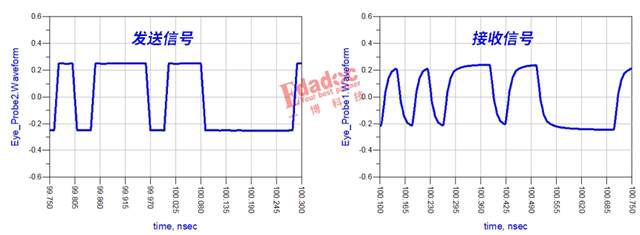

一般我们做这种高速信号仿真只会关注接收端的波形或者眼图,例如上面经过特定损耗channel的25Gbps高速链路,我们看发送和接收端的波形分别是下面这样的:

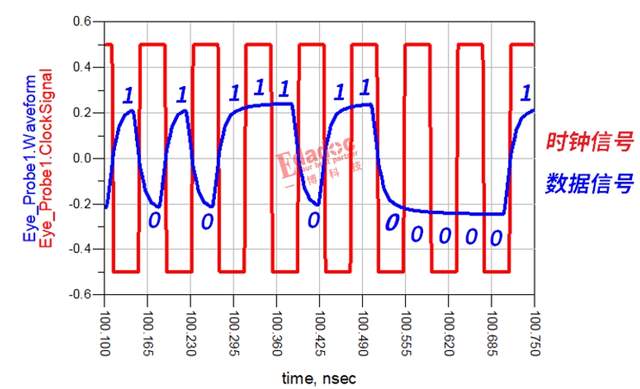

受到衰减之后,接收信号就变得不那么完美了,这个是正常的现象。除了关心接收端信号之外,你们有看过接收端进行CDR模块恢复出来的时钟信号吗?把恢复出来的时钟信号和接收端的高速信号放在一块看,是这样子的:

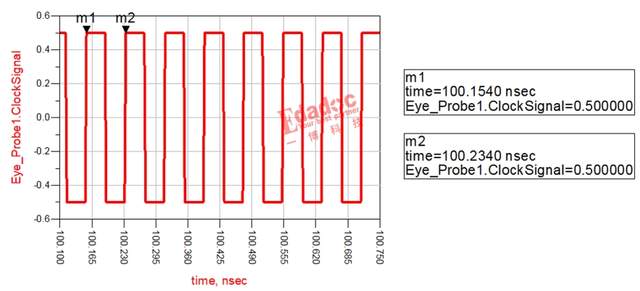

在截取的这一串数据信号中,时钟信号通过上升和下降沿对数据信号进行采样。对于高速信号来说,每一位的“1”或者“0”的位宽的倒数就是我们的速率25Gbps。那问题来了,时钟信号的上升和下降沿都对数据进行采样,那么时钟频率是多少呢?也就显而易见了,12.5GHz,如下图计算也可以得到。所以我们高速先生也经常会说,25Gbps信号的基频是12.5GHz,也就是为什么我们看通道损耗的时候要用12.5GHz来约束的原因了。

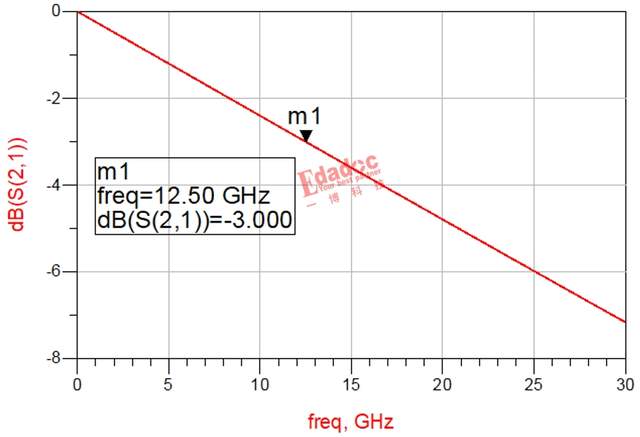

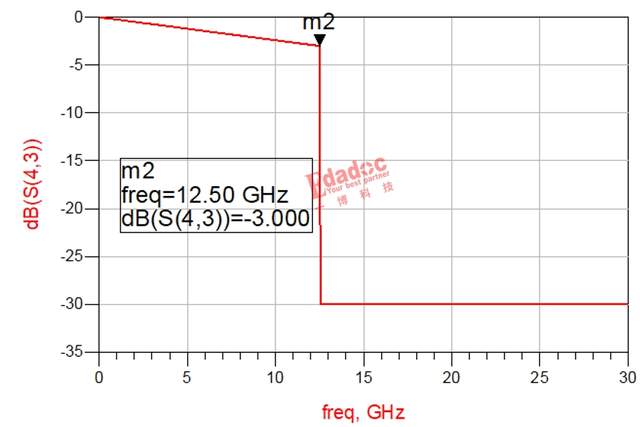

还不懂?那高速先生再举一个更直观的仿真例子。就以上面25Gbps眼图仿真为例,下面是比较理想情况下的channel的损耗参数,在12.5GHz是3dB的损耗,按照线性度来说25GHz处应该就是6dB了。

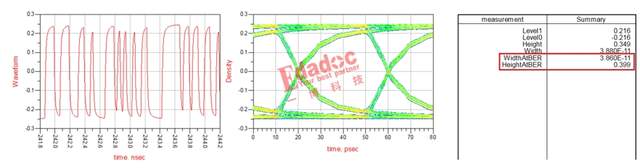

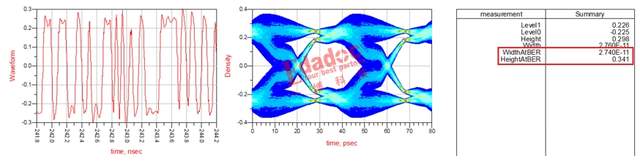

在发送端发送25Gbps的信号,在接收端看到的波形和眼图结果如下所示:眼高399mV,眼宽38.6ps。

那怎么证明我们是看12.5GHz-3dB的损耗,而不是看25GHz-6dB的损耗呢?很简单,我们另外做一个对比的通道参数,如下所示,我们让这个通道在12.5GHz位置还是3dB,但是过了12.5GHz后,立马变成30dB的超大衰减,在25GHz处也是30dB。

那如果25Gbps信号的损耗真的是要看到25GHz频点的话,30dB的衰减在眼图中估计你只能看到黑屏和雪花了。但是实际仿真却不是这样,你依然能得到还不错的眼图结果,如下所示,眼高341mV,眼宽27.4ps。眼高其实衰减得不多,主要是眼宽恶化很多,一方面说明了25Gbps的损耗肯定就不是看25GHz频点了,另外也证明了12.5GHz频点之后的损耗对眼宽影响是巨大的(1倍频之外主要影响上升沿)。

希望大家看完这篇文章之后,就不要老是要求看25GHz的损耗来了哈,如果硬是要把本来12.5GHz就可以保证的损耗变成了25GHz,那么你的走线长度就只能缩短一半,或者板材的等级要提升一倍,而且还要附加各种复杂的过孔工艺才能满足哦。然而这一切本来都是不需要的,是大家自己吓自己哈!

问题:是不是所有高速信号协议的损耗都是看速率的一半频点呢,或者大家有没有因为这个误区做过的傻事呢?都可以说说哈!

-

明明我说的是25G信号,你却让我看12.5G的损耗?2024-10-23 1552

-

PCB仿真相同损耗下,28G NRZ的产品不能直接升级到56G PAM4?2025-03-11 3466

-

【我是电子发烧友】【转】12.5G锁相环设计调试2017-04-28 3774

-

介绍:两款常见的25G SFP28G光模块2018-04-24 10334

-

教你设计一个25G系统2018-05-30 4070

-

12.5G锁相环设计调试经验分享2018-08-15 15278

-

设计25G系统的5个小窍门2018-09-03 1783

-

透视数据中心中的25G/50G和100G技术看完你就懂了2021-05-20 2308

-

推荐收藏:25G光互连——5G前传篇2021-07-08 2892

-

问答专栏丨25G光互连常见问题解答2021-07-12 1842

-

25G全系列产品解决方案2021-10-28 1622

-

设计一个25G系统的技巧分享2022-11-17 697

-

25G线缆有哪些分类?区别是什么?2018-12-13 7662

-

25G DAC高速线缆 vs 25G AOC有源光缆,哪个更好?2019-11-28 4419

全部0条评论

快来发表一下你的评论吧 !