SK Hynix的72L NAND快闪存储器与各家64L的对比分析详解

存储技术

描述

在SK Hynix的72层(72L) TLC NAND快闪存储器中,所谓的P-BiCS (Pipe-shaped Bit Cost Scalable)单元,是利用管线式(pipe)闸极连结每一个NAND字串(NAND string);从其布局可见,该芯片包含4个平面(plane)以及双面字元线开关/解码器(two-sided wordline switches/decoders)。

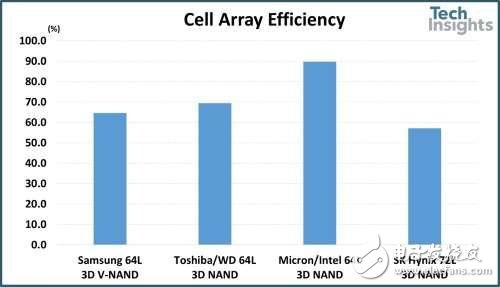

该存储器阵列的效率约57%,是因为相对较大的存储器与其他周边;而SK Hynix的36L与48L产品存储器阵列效率则分别为67.5%与64.0%。此趋势显示SK Hynix应该会为下一代芯片开发尺寸更小巧的设计。

三星(Samsung)以及东芝/WD (Toshiba/Western Digital)的64L 3D TLC NANS裸晶,有超过65%的存储器阵列效率;不过以上的存储器芯片尺寸以及功能则都差不多。

各家64L与72L 3D NAND快闪存储器单元阵列效率比较

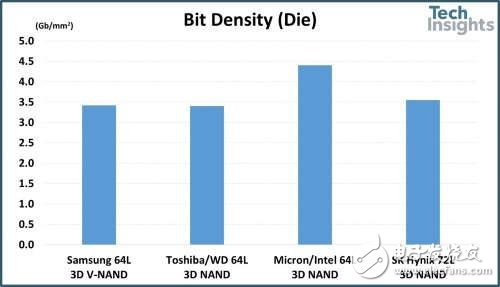

SK Hynix 72L NAND快闪存储器的位元密度为3.55 Gbits/mm2,高于Samsung/WD之64L芯片;而美光/英特尔(Micron/Intel)的64L 3D NAND芯片是4种解决方案中位元密度最高的,主要是因为采用名为CuA (CMOS under the array)的独特砖式(title)布局。

64L与72L 3D NAND存储器芯片位元密度比较

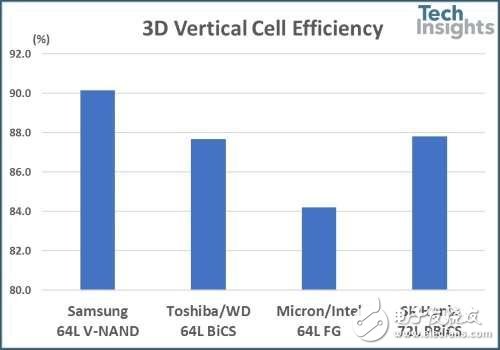

在3D NAND存储器单元架构方面,SK Hynix芯片堆叠了总共82个闸极,包括选择器(selector)与虚设字元线(dummy wordlines,DWL);我们知道有72个闸极是用于主动字元线单元,而最上方的三个闸极则是用于源极与汲极的选择器闸极(selector gates,SG),剩余的7个闸极应该是用于DWL以及隔离闸极(isolation gates)。

在各家厂商的64L NAND元件中我们看到:

Samsung采用了总数71个闸极,其中有3个用于SG,4个用于DWL;Toshiba/WD产品的闸极总数为73个,其中7个用于SG,2个用于DWL;Micron/Intel产品的闸极总数为76个,其中2个用于SG,7个用于DWL。

垂直单元效率计算方法,是主动字元线的数量除以垂直堆叠闸极的总数;其结果就是该3D NAND存储器单元架构的流程效率。SK Hynix 72L产品的垂直单元效率为87.8%,Toshiba/WD的64L BiCS产品也是一样;Samsung的64L产品效率则为90.1%,而Micron/Intel的64L产品效率则为84.2%,如下图所示。

64L与72L 3D NAND存储器产品的垂直单元效率

SK Hynix先前的36L与48L产品是采用单步骤蚀刻制程来制作分别为43个与55个闸极总数的通道电洞(channel holes);新一代的72L存储器单元则是采用两步骤蚀刻制程来制作通到电洞。在管线闸极上,较低的42个闸极以及较上方的40个闸极,分别是以两个不同的蚀刻步骤形成。而狭缝(slits)与子狭缝(sub-slits)则是以单步骤蚀刻形成,制程整合程序如下:

管线闸极铸模成形(下方部位)通道蚀刻(下方部位)牺牲层填入电洞;铸模成形(上方部位);通道蚀刻(上方部位);牺牲层移除;通道成形。

Micron/Intel的64L产品采用双堆叠NAND字串架构,在上部与下部堆叠之间有一个平板(plate);而SK Hynix的72L产品则是采用两步骤蚀刻制程,而非双堆叠NAND字串,工程师必须要严密控制制程步骤,以避免上下部位的通道电洞未对齐;该电洞的尺寸在256 Gbit 72L产品约只有10纳米。

-

存储器厂商发力,10纳米DRAM技术待攻克2014-04-04 1424

-

海力士第四代3D闪存芯片256-Gbit 72层TLC NAND介绍2018-08-29 9189

-

SK海力士开始采样128层3D NAND SSD2019-11-25 5807

-

SK Hynix展示DDR5存储器模组,支持DDR5的硬件预计明年推出2020-01-15 3285

-

SK Hynix & Spansion & JSC NAND FLASH参数对比2018-01-10 0

-

Micron美光公司因其DRAM和NAND快闪存储器技术创新2009-05-08 1015

-

旺宏电子推出全球首颗256Mbit序列快闪存储器2009-11-02 735

-

SK Hynix月底量产48层堆栈3D NAND闪存 三星后第二家2016-11-09 921

-

海力士发布72层256G 3D闪存芯片2017-04-11 1624

-

苹果闪存芯供应商推出256Gb 3D NAND 或用于未来iPhone2017-04-12 1088

-

美光新加坡兴建第3工厂,欲抢占NAND Flash快闪存储器市场2018-06-11 1065

-

快闪存储器控制器选择技巧2018-03-07 1421

-

手机、pc该怎样正确选择快闪存储器2018-03-12 1590

-

NAND Flash快闪存储器供应仍有缺口,多厂商扩产以增加产能2020-09-03 854

-

NAND存储种类和优势2024-03-22 903

全部0条评论

快来发表一下你的评论吧 !