74ls290构成60进制计数器电路

IC应用电路图

512人已加入

描述

数字钟表的分、秒计数都是六十进制,74LS290试利用两片74LS290接成六十进制计数电路。

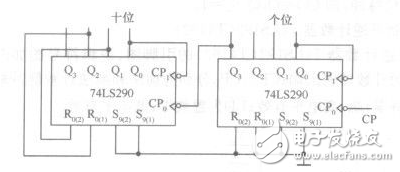

六十进制由二片74LS290组成,分别连成六进制和十进制。个位为十进制,十位为六进制。当十位计到6时,个位、十位同时清零,电路连接如下图所示。

计数脉冲由个位的CPo端加入,个位的Q3接十位的CPo,十位的Q2、Qi分别与其R0(2)端相接。当个位计数器每计满10个计数脉冲时,由Q3输出一个进位脉冲,其下降沿触发十位计数器进行计数。当十位计数器计到6时,其状态为0110,于是有将十位计数器清零,即Q3 Q2 QiQo =oooo,此时个位计数器也处于0000状态,从而实现了六十进制计数。

用多片集成计数芯片设计计数器时,用二进制计数器和十进制计数器有所不同。另外,在例8.3.4中,六十进制计数器的十位芯片的时钟来自于个位的Q3,是异步方式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成四位二进制计数器2021-07-29 5569

-

74ls290计数器电路大全(六种进制计数器电路)2018-01-26 133376

-

74ls290构成31进制计数器电路图文详解2018-01-25 22577

-

74ls160构成24进制计数器2018-01-18 174611

-

74ls90设计60进制计数器2017-12-22 171933

-

异步2-5-10进制计数器74LS2902016-07-13 4351

-

基于Multisim的计数器设计仿真2013-07-26 3963

-

求74LS193设计的60进制计数器2013-01-05 11458

-

七进制计数器电路2009-09-16 10840

-

74LS161构成的五十(50)进制计数器电路图-原理图2009-03-28 37695

-

74LS290中文资料.pdf2008-03-15 5097

全部0条评论

快来发表一下你的评论吧 !