使用aurora核的点对点通信应用设计

电子说

描述

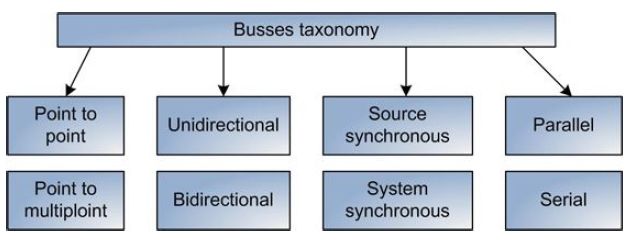

总线分类

总线是一个被用来连接两个或多个模块和设备的设计组成。下图展示了不同总线的分类。

01

点对点

只连接两个设备或模块的一种总线。点对点总线的优势在于更好的信号完整性。

02

点对多

连接至两个以上的模块或设备的总线。点对多总线的优势在于由于低数量轨迹带来的低引脚数量和更简化的板级设计。

03

单向

被单一模块和设备驱动的总线连接至另一个总线。单向总线的优势在于更简便的执行,以及更简便的板级终端方案。

04

双向

可被任何设备或模块驱动的总线连接至另一总线。其优势在于由于共用相同总线信号带来的更低的引脚数量。

05

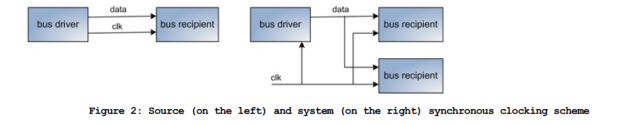

源同步时钟

是一种在一总线上产生伴随数据的时钟的技术。这一方法的一个优势在于它简化了系统的时钟设计,并且将总线驱动从接收方分离开。这一时钟方案被用在几个高速接口,如spi和pci接口。时钟信号可以被分开,或嵌入到数据中,并且在接收端恢复。

06

系统同步时钟

设备和模块连接到一个总线并使用一个单一时钟,不像源同步时钟方法,系统同步时钟方案不需要在接收端分离时钟域。

07

并行总线

并行总线一般被用于中低频总线中,对于中低频的组成并没有明确的定义,但经验法则认为低于100MHz为低频。100-300MHz为中频。

Xilinx 提供了几个可以被用来设计并行总线的元素:

1.IDDR:

一个专用寄存器,可在FPGA架构中将双速率数据转换为单速率数据输出。

2.ODDR:

一个专用寄存器,可将输入单速率数据转换为双速率外部输出。

3.IODELAY:

被用来给输入数据提供一个固定或可调节的延迟或给输出数据提供一个固定延迟的设计元件。IODELAY主要被用来做输入与输出数据的对齐。

4. IDELAYCTRL:

与IODELAY一起用于控制延迟逻辑。 其中一个IDELAYCTRL输入是一个参考时钟,它必须是200MHz才能保证IODELAY中的分接头延迟精度。在高频率校准并行总线的时候需要调整输入与输出的延时。调整过程是动态的,在电路板加电之后并在操作过程中定期执行。执行动态总线校准有几个原因。 例如,温度和电压波动会影响信号延迟。 此外,由于制造工艺的差异,PCB上和FPGA内部的跟踪延迟也会有所不同。 由于不同信号上的可变延迟,并行总线数据可能会偏斜。

08

串行总线

并行总线不能扩展到更高的运行频率和总线宽度。设计一个高频率的并行总线是有挑战性的因为多个数据信号之间的偏差,严格的时间预算,以及需要执行所有总线信号的长度匹配的更复杂的电路板布局。为了克服这些挑战,许多系统和几个众所周知的通信协议已经从并行迁移到串行接口。其中两个例子是Serial ATA,它是ATA或并行ATA的串行版本,PCI Express是下一代并行PCI。

串行总线的另一个优点是引脚数量较少。 串行总线的一个缺点是它的PCB设计要求更高。 高速串行链路通常以数千兆位的速度运行。 结果,它们产生更多的电磁干扰(EMI)并消耗更多的功率。

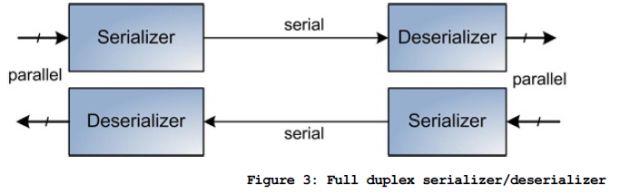

外部串行数据流通常转换为FPGA内部的并行数据。 这个被称为SerDes(串行器/解串器)的模块。 串行器将并行数据并行转换为串行输出,速率更高。 相反,解串器将高速串行输入转换为并行输出。 由于执行串行化和反序列化所需的额外步骤,使用SerDes的缺点是额外的通信延迟; 更复杂的初始化和定期的链路训练; 和更大的逻辑大小。

下图显示了实现为两个SerDes模块的全双工串行总线。

1.ISERDES

一个专用的串行到并行数据转换器,以促进高速源同步数据采集。 它具有SDR和DDR数据选项和2到6位数据宽度。

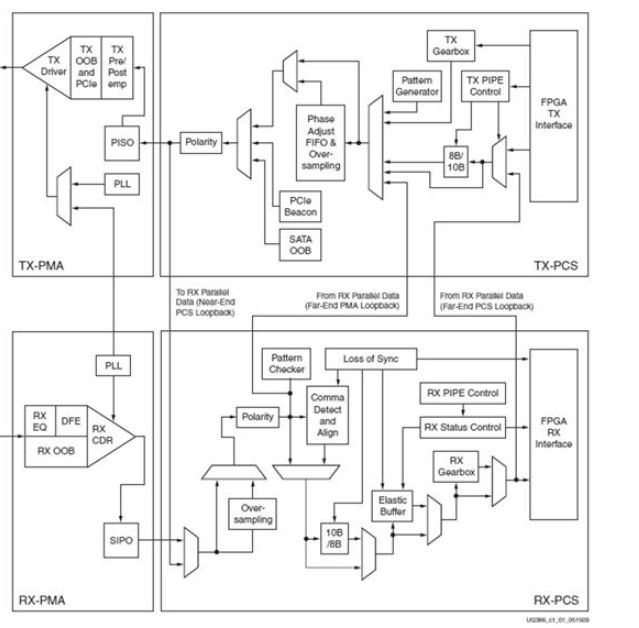

2.GTP/GTX

一些Virtex和Spartan FPGA中的嵌入式收发器模块。 它是一个复杂的模块,高度可配置,并与FPGA逻辑资源紧密集成。

下图显示了Virtex-6 GTX收发器的框图。

3.Aurora

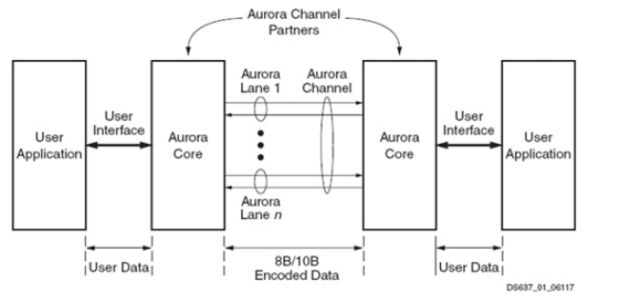

Aurora 是一个很高效的低延迟点对点的串行协议,它使用了GTP收发器。它旨在隐藏GTP的接口细节和开销。Xilinx 提供一个拥有执行aurora协议的用户友好接口的ip核。核心提供的功能包括不同数量的GTP通道,单工和双工操作,流量控制,可配置线路速率和用户时钟频率。

下图展示了使用了aurora核的点对点通信。

-

【米尔-Xilinx XC7A100T FPGA开发板试用】+04.SFP之Aurora测试(zmj)2024-11-14 3261

-

基于FPGA的Aurora 8b10b光通信测试方案2023-10-01 10767

-

如何实现点对点数据通讯,物联网网关远程组网技术(点对点通信)2023-04-23 4261

-

如何实现模块与模块之间点对点的通信2022-02-28 5361

-

Xilinx平台Aurora IP介绍(一)Aurora基础知识2022-02-19 9327

-

Aurora 8B/10B IP核(一)—Aurora概述及数据接口2022-02-16 11484

-

如何通过nrf24l01实现点对点通信?2021-12-17 1339

-

基于STM32+LoRa的点对点通信源代码2021-09-09 2002

-

如何去设计一种点对点通信协议PPPoE模块?2021-06-03 1767

-

探究Aurora协议的高速通信技术2021-05-05 12010

-

基于西门子1200PLC的点对点通信实例分享2020-12-21 6567

-

AURORA_8b10b核中RX_SRC_RDY_N信号2017-05-17 3830

-

aurora使用问题2015-03-06 5036

-

一种点对点高速通信控制器的设计与实现2012-10-10 1193

全部0条评论

快来发表一下你的评论吧 !