简单数字钟仿真电路图大全(五款数字钟仿真电路图)

数字时钟电路图

描述

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。

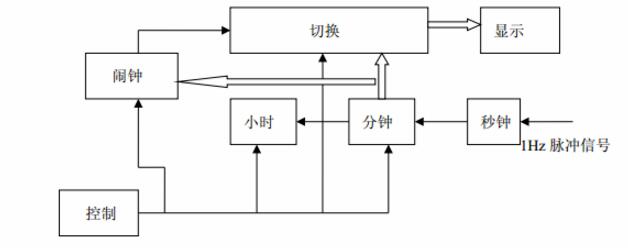

简单数字钟仿真电路图(一)

将时钟信号输给秒模块,秒模块的进位输给分模块,分模块进位输入给时模块,切换的时候使用2选1数据选择器进行切换,电路框图如下:

该方案的优点是模块内部简单,基本不需要额外的电路,但缺点也很明显,该方案结构不清晰,模块间关系混乱,模块外还需使用较多门电路,不利于功能扩充,且使用了异步电路,计数在59的时候,高一级马上进位,故本次设计不采用此方案。

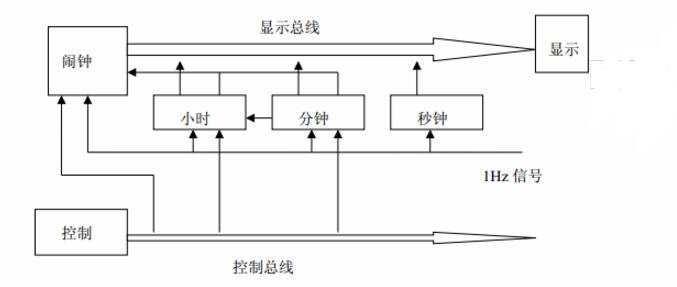

简单数字钟仿真电路图(二)

时钟信号分别加到各个模块,各个模块功能相对独立,框图如下:

该方案用总线结构,主要功能集中在模块内部,模块功能较为独立,模块间连线简单,易于扩展,本次设计采用此方案。

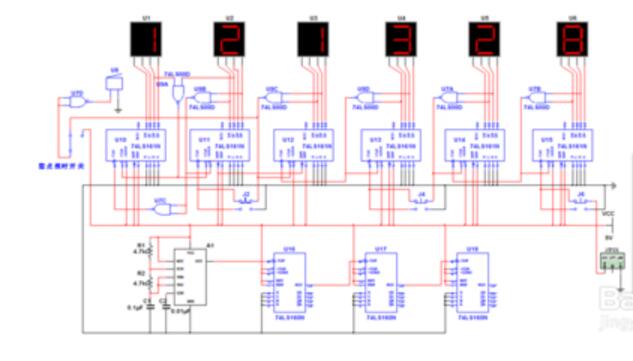

简单数字钟仿真电路图(三)

显示数码管能够正常跳动并进位,当整点报时开关打开时,在达到整点是蜂鸣器响;当按下校时开关时,数码管会跳动加“1”。

简单数字钟仿真电路图(四)

用电路元件符号表示电路连接的图,叫电路图。电路图是人们为研究、工程规划的需要,用物理电学标准化的符号绘制的一种表示各元器件组成及器件关系的原理布局图。由电路图可以得知组件间的工作原理,为分析性能、安装电子、电器产品提供规划方案。

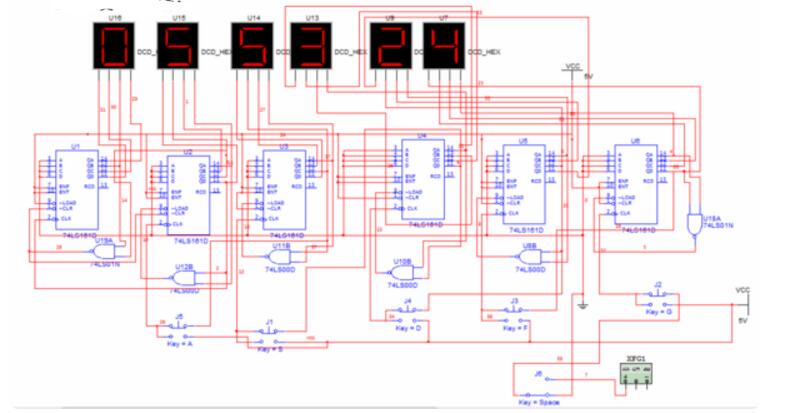

简单数字钟仿真电路图(五)

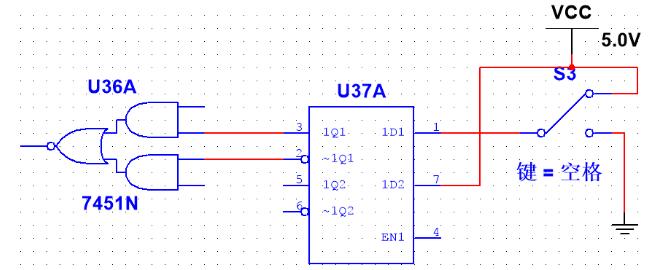

校时电路由两个相同的模块构成,分别校正时和分,下面以校正时的校时电路为例来阐述它的电路原理。它主要是由7451与或非门和74LS375四位双稳态锁存器两部分组成的控制电路。开关S1合到1端时,74LS375置1,时脉冲信号通过7451N与或非控制门电路,而秒脉冲信号此时不可通过,数字钟正常工作;开关S1和到2端时74LS375置0,此时秒脉冲信号通过7451N与或非控制门电路,而正常计时的时脉冲信号却不能通过,这样一来,时计数器成为秒计数器实现快速校准。

-

jf_32201489

2022-09-19

0 回复 举报有更清晰的图吗 收起回复

jf_32201489

2022-09-19

0 回复 举报有更清晰的图吗 收起回复

-

数字时钟设计电路图汇总(七款数字时钟电路图)2018-01-26 166234

-

数字钟打点报时电路图2009-07-29 1782

-

数字钟整点名曲报时电路图2009-05-30 1358

-

LCD数字钟整点语言报时电路图2009-05-19 3892

-

新颖的集成电路数字钟电路图2009-05-18 1305

-

数字钟定时控制器电路图2009-04-13 1526

-

数字钟兼电容测量电路图2009-04-11 1252

-

单片机数字钟电路图2008-01-12 636

-

最简单数字钟电路图2008-01-08 1449

全部0条评论

快来发表一下你的评论吧 !