74ls164内部结构及其应用(74ls164引脚图及功能_工作原理)

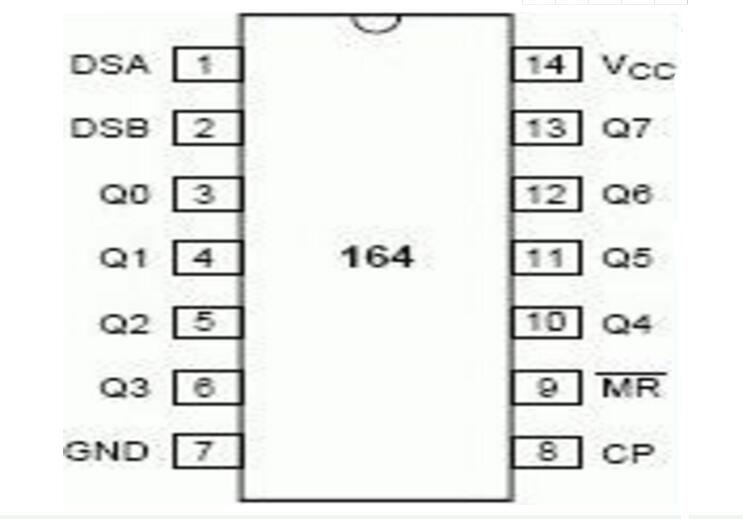

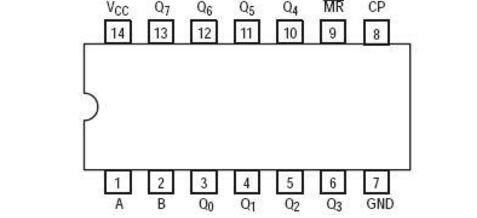

芯片引脚图

描述

74ls164特性

门控串行数据输入;

异步中央复位符合JEDEC标准no.7A;

静电放电(ESD)保护;

HBMEIA/JESD22-A114-B超过2000V;

MMEIA/JESD22-A115-A超过200V;

多种封装形式;

额定从-40°C至+85°C和-40°C至+125°C。

74ls164引脚及功能说明

引脚功能说明:

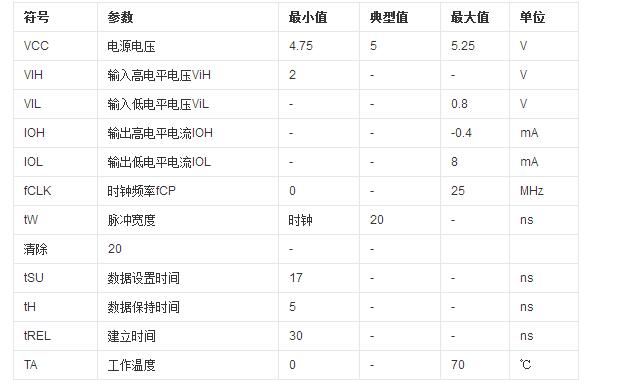

74ls164电气特性

74ls164功能表

H=HIGH(高)电平

h=先于低-至-高时钟跃变一个建立时间(set-uptime)的HIGH(高)电平

L=LOW(低)电平

l=先于低-至-高时钟跃变一个建立时间(set-uptime)的LOW(低)电平

q=小写字母代表先于低-至-高时钟跃变一个建立时间的参考输入(referencedinput)的状态

↑=低-至-高时钟跃变

74ls164工作条件

[1]对于DIP14封装:Ptot在超过70°C时以12mW/K的速度线性降低。

[2]对于SO14封装:Ptot在超过70°C时以8mW/K的速度线性降低。

[3]对于SSOP14和TSSOP14封装:Ptot在超过60°C时以5.5mW/K的速度线性降低。

[4]对于DHVQFN14封装:Ptot在超过60°C时以4.5mW/K的速度线性降低。

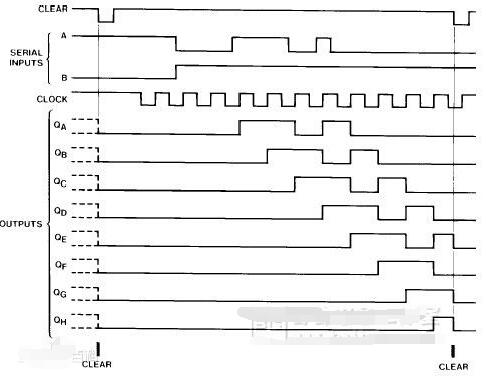

74ls164时序图

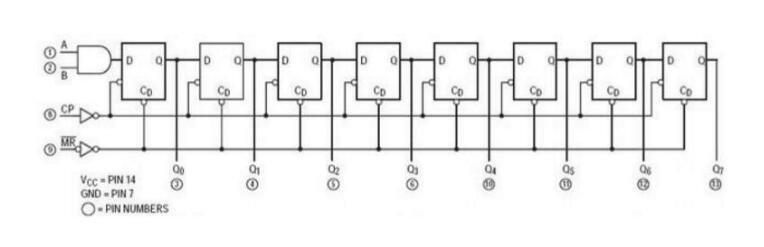

74ls164内部结构与工作原理

74ls164内部电路图

该8位移位寄存器具有与门使能控制串口输入和一个异步复位输入的特点。使能控制输入端能控制不需要的输入数据信号使其为低电平。当复位信号为低电平时,不管其他信号为何状态,其输出均为低电平;复位信号为高电平时,寄存器从第一位开始在每个时钟信号的上升沿对输入数据依次移位存储。

74LS164封装图

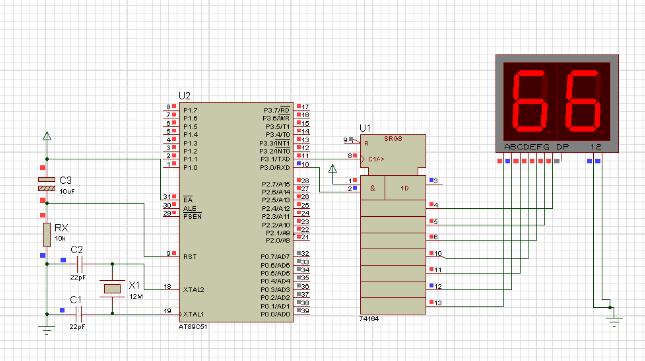

74LS164的应用

74LS164串入并出;基于单片机仿真,附有测试程序。

#include《REGX52.H》

#defineuintunsignedint

#defineuchar

unsignedchar

sbitdate=P3^0;

sbitclock=P3^1;

ucharcodetable[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

uinti,temp,aa;

voiddelay(uinttt)

{uintz;

for(;tt》0;tt--)

for(z=400;z》0;z--);

}voidmain()

{

while(1)

{

for(aa=0;aa《16;aa++)//依次显示16个数

{

temp=table[aa];

for(i=0;i《8;i++)

{

clock=0;//升上沿移位数据

date=temp&1;//每次穿入一位数据

clock=1;

temp》》=1;

//将次低位的数据移

至最低位

}

delay(200);

}

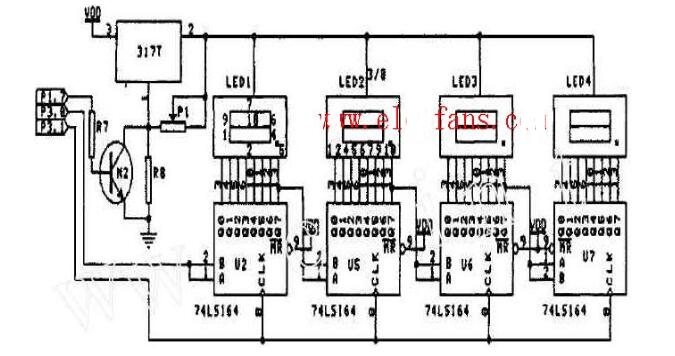

采用了74LS164这个串入并出的移位寄存器,很好地解决了2051与LED的显示接口电路。

2051余下的并行I/O口线不足8根,数据的并行输出已不可能,但可以考虑串行输出方法,图1给出串行口扩展的4位LED显示接口电路。该电路只使用2051的3个端口,配接4片串入并出移位寄存器74LS164与1片三端可调稳压器LM317T

- 相关推荐

- 热点推荐

- 74LS164

-

74LS164芯片是什么?有何作用2022-01-25 2821

-

74LS164高速的硅栅CMOS器件芯片学习参考手册2021-05-24 1168

-

两个74ls164怎么连?74ls164联级应用电路2018-05-08 19930

-

74LS164在2051单片机LED显示电路中的应用2018-01-29 6164

-

74LS164驱动数码管动态显示(74LS164工作条件_电气特性)2018-01-27 16187

-

74ls164功能及工作原理2017-12-01 29450

-

74LS164英文手册2016-11-21 846

-

74LS1642016-04-29 1065

-

如何用74LS164驱动24064液晶屏2013-10-24 2393

-

74ls164 c程序2008-07-14 10522

-

74ls164引脚图 74ls164管脚图 74ls164真2008-04-28 10237

全部0条评论

快来发表一下你的评论吧 !