面向信号处理与通信系统的下一代设计流程

模拟技术

描述

在复杂信号处理与通信技术的开发中,设计流程的不连续越来越具有破坏性,并且代价越来越高昂。同时,缩短设计和验证周期的需求使设计不连续的影响被进一步被放大。本文通过介绍算法设计、系统架构和硬件设计中的几个用例,来展示最近在建模、仿真和代码生成工具及方法上的重要技术发展。

流系统的算法设计

现在越来越多的工程师开始用MATLAB中的浮点运算来开发信号处理与通信系统算法。这些算法开发人员可以利用MATLAB强大的信号采集和分析功能,以及多个工具箱的内置算法库。但是,在有些团队中,为了算法的优化实现,工程师会用C代码重写这些算法,将其转换为定点或整数运算,或将它们与其他设计元素集成。该重写步骤就是设计流程中一个潜在的,成本高昂且具有破坏性的典型不连续。

MATLAB提供的数百个用于信号处理、通信、图像和视频处理的新组件,都可作为System对象库。在MATLAB中,System对象库是为设计实时系统设计的,是即用型打包的算法实现。它们隐式地处理着流、索引、缓冲和状态管理,使编写、调试和维护代码变得更简单。

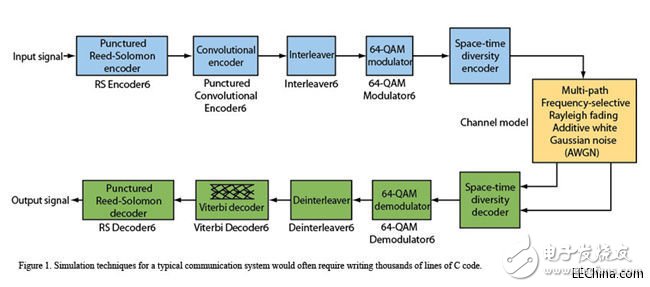

图1显示的是带发射器、信道和接收器组件的基本通信系统的框图表示形式。为了对这样一个系统进行建模和仿真,工程师需要写数千行的C代码,然后,寻找各种方法,以便将设计与测试设备进行集成,或者分析仿真结果。

图1:典型通信系统物理层的框图。

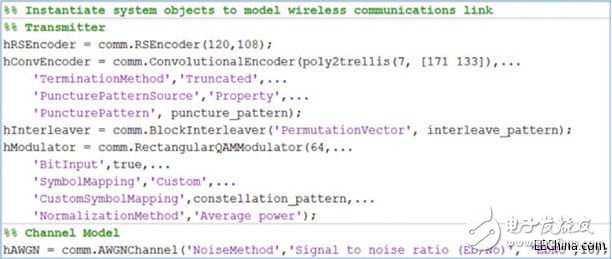

与这数千行C代码(一般情况下为实施此通信系统而写入的)相比,图2中显示的MATLAB代码使用了来自DSP System Toolbox和Communications System Toolbox的若干个System对象。

图2:部分MATLAB代码,展示来自DSP System Toolbox和Communications System Toolbox的System对象的使用。

例如,要对发射器进行建模,工程师可以按顺序实例化和调用Communications System Toolbox中的Reed-Solomon编码器、卷积编码器、区块交织器、矩形QAM调制器和正交空时分组码System对象(如图2所示)。这种代码结构让工程师可以轻松地将其与原始规格或框图进行对比。算法设计师则可以快速地将此代码与其现有的MATLAB代码相结合,并使用从测试仪器获取的实时流数据来测试这些算法。

MATLAB与C/C++相结合

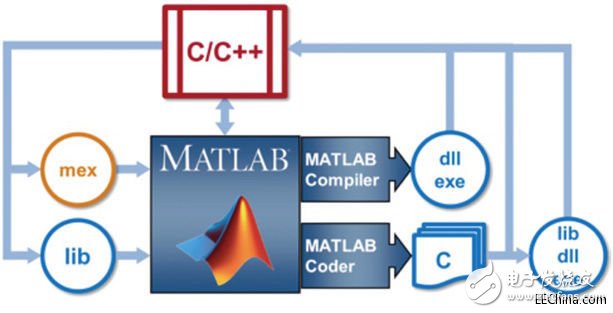

使用System对象编码的算法可促进系统设计流程中的代码重用。浮点或定点型的MATLAB代码可以作为系统架构、建模和设计流程的一部分直接包含在Simulink模型中。工程师也可以使用MATLAB Coder从MATLAB代码自动生成C代码,这包括System对象,在正确验证后,使用该C代码进行仿真,或与其他C/C++设计元素进行集成。

图3展示的是工程流程中使用MATLAB与C/C++的集成而实现的几个重要用例。例如,工程师可以从C程序直接触发MATLAB,以利用MATLAB的信号处理库或可视化功能;可以在MATLAB中将现有的C/C++设计直接用作外部库;也可使用MATLAB Compiler部署MATLAB算法, 甚至可使用MATLAB Coder从MATLAB自动生成C代码。

图3:将MATLAB与C/C++相结合为信号处理应用提供了强大而灵活的算法及系统设计平台。

RF和数字系统架构

在基于LTE 、蓝牙、ZigBee、Wi-Fi或其他技术规范的RF设计中,第一个步骤通常是静态链接预算计算。这些计算提供了良好的起点,但是它们未将输入信号调制、镜像效应、干扰以及其他真实的现象考虑在内。为了对通信系统的RF损失效果进行有效的建模和仿真,系统架构师会同时采用多个不相关联的工具,它们可支持数字或模拟/RF设计,但不能同时支持两者。

SimRF工具箱与Simulink集成,为 RF收发器中的多频动态系统的仿真提供电路包络引擎。SimRF工具箱包含非线性放大器、三端口混频器、S参数模块和其他基本模块的行为模型,用于设计含任意拓扑的架构,并对RF前端进行系统级仿真。借助SimRF,您可以仿真RF放大器以预估增益、噪声、奇偶阶互调失真。混合器的仿真使您可以预测镜像抑制、倒易混频(Reciprocal mixing)、本地振荡器相位偏移和DC转换。您也可以在时域和频域,对线性与非线性组件之间的频率相关失配进行仿真。

SimRF与Simulink相结合,为在统一设计设计中对RF及基带子系统进行建模和仿真提供了通用环境。通过结合使用这些工具,系统架构师可以在开发过程的早期完成真实的仿真,并在包含数字和模拟/RF组件的设计中做出合理的权衡决策。

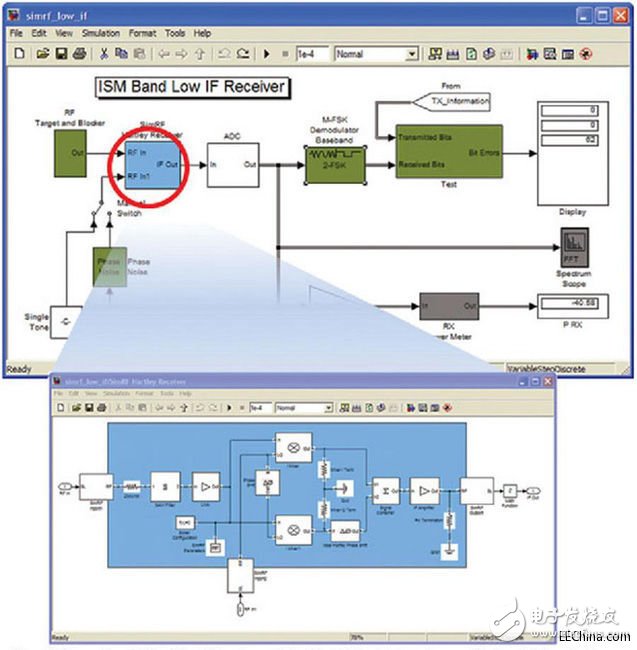

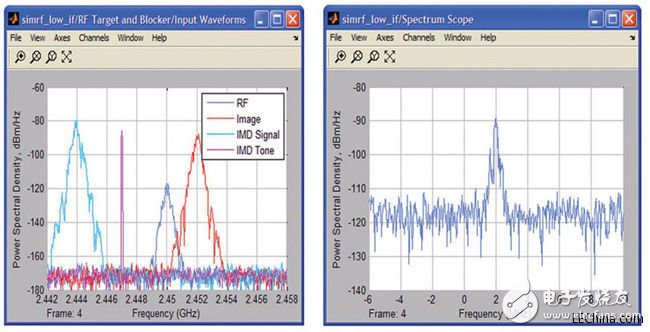

图4显示工作在ISM频段上的低IF接收器的整体系统模型,包含数字信号处理组件和RF接收器子系统。图中也显示了采用Hartley IF接收器的RF子系统的详细信息。与使用两端口单元相级联以及单频近似值的传统建模方法不同,使用三端口单元可简化接收器模型。该模型也会使用电路包络仿真技术,并支持多频建模来估算干扰器和镜像信号对非线性接收器的影响。

图4:一个统一模型中的ISM频段低IF接收器(含数字和RF子系统)(上图),以及在SimRF中建模的Hartley接收器RF子系统的详图(下图)。

系统架构师还可以在这统一的环境下来研究诸如超外差接收或直接变频这样的镜像抑制方法的可行性和性能提升价值。除了对RF损失效果进行仿真外,系统架构师还可以使用设计中使用过的相同模型,来执行仿真中的验证任务,而这些任务通常需要在试验台才能完成。

图5:显示低IF镜像抑制结果的输入(左侧)和输出(右侧)功率谱密度图形。

硬件设计

在完成算法设计和系统架构后,许多开发周期的下一步是FPGA实现和数字部分的验证,有时候会作为ASIC进入最终开发。FPGA原型和实现中低效率的主要原因是耗时的设计迭代(这是寻求功耗、性能和区域达到恰当平衡所必需的)。

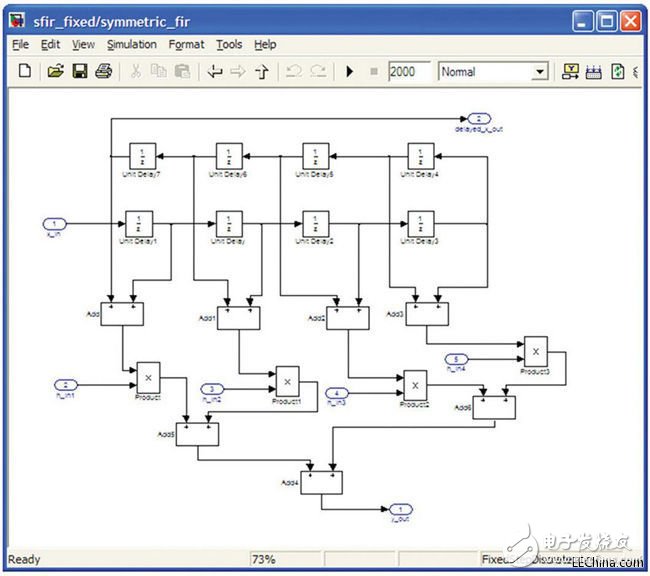

图6显示的是一个以定点算法来实现的对称FIR滤波器。为实现硬件中的滤波器,工程师必须谨慎地平衡吞吐能力和延迟,并监控所用的硬件资源量。“关键路径突出显示”是一项新功能,能针对系统中的潜在瓶颈提供可操作的信息。

图6:在Simulink中建模的对称定点FIR滤波器。

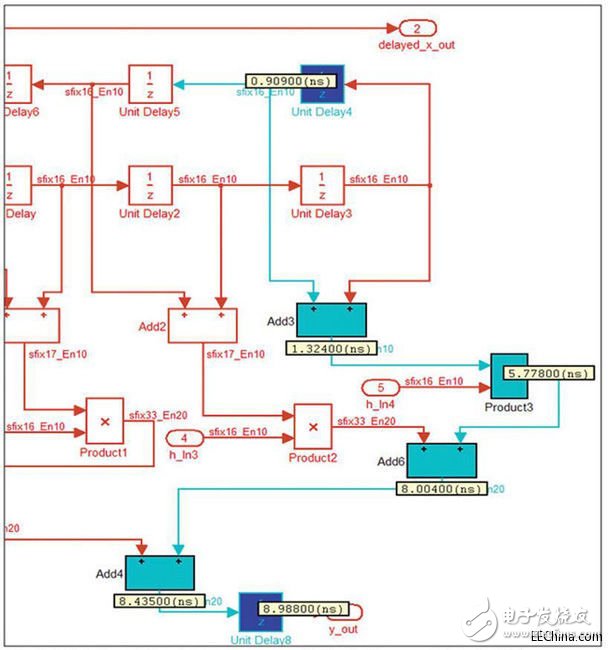

使用综合工具生成的后综合信息,HDL Coder可以在Simulink模型中对关键路径时间进行注释。工程师可以利用该信息与流水线技术,对他们的设计进行划分,以减少关键路径延迟,并推断出大部分FPGA上专用DSP可用资源的使用情况。图7展示了关键路径自动突出显示和针对每个路径段估算延迟的相同的滤波器设计。

图7:对称的定点FIR滤波器,展示关键路径和估算的延迟。

如上所述,流水线技术是工程师用来解决关键路径延迟的主要技术之一。对于流水线技术,众所周知的挑战之一是并行路径可能存在不匹配延迟,这会导致意外的系统行为。令人高兴的是,用以解决这一问题的分布式流水线技术现在已实现了自动化。通过选择该方案,工程师可以自动重定时模型,并在相关的并行路径中平衡流水线寄存器所引入的延迟。

在过去,这些类型的设计迭代和权衡评估要求我们投入大量的时间和精力。最近,包括Workflow Advisor控制台在内的增强,使工程师能够以直观的方式更快地完成设计迭代。对于那些不是特别熟悉HDL编程却需要利用FPGA处理的人员来说,这特别有帮助。

除了使用关键路径突出显示和分布式流水线技术外,工程师还可以查看一份自动生成的资源使用报告,来监控所用的关键硬件组件的类型和数量,并通过对多个可行的设计方案进行快速迭代,为给定的情况确定最佳架构选择。

加速跨团队的设计

今天的工程经理面临协调处理整个系统不同部分的团队的挑战,这些团队位于不同地方、使用不同的工具。在许多情况下,系统级设计最好在图形环境中完成,而某些较低级别的细节设计最好在MATLAB或C中最好以文本的形式表示。本文展示了一些提升跨设计流程各个阶段的效率的最新技术发展。

对于算法设计,在建模、仿真信号处理,以及通信系统中,System对象库是一个重要的新开发工具。现在,MATLAB中可提供数百个即用型信号处理与通信System对象。此外,System对象支持定点算法,它们可以与Simulink集成或用于自动生成C代码。SimRF采用电路包络仿真技术,是面向更高效系统架构流程的重要新工具。它使工程师可以在一个统一的环境中对RF和基带系统组件进行建模,并执行真正的多频仿真。

为了缩短硬件设计的设计迭代循环时间,HDL Coder中有多个最新的开发工具,包括Workflow Advisor、关键路径突出显示、分布式流水线技术、回注及资源利用情况报告,这提供了有关系统性能的可操作信息,并为硬件开发人员简化工作流框架。

无论团队是小是大,地理位置分散还是位于同一个办公室,工程部门可以应用部分这些技术来消除其工作流程中的不连续,并借此简化和加速复杂信号处理与通信系统的开发。

-

下一代通信系统:面向语义通信的模分多址技术2023-06-06 3703

-

下一代广电综合业务网上营业厅的特点与功能2010-04-23 2316

-

下一代定位与导航系统2012-08-18 2722

-

下一代SONET SDH设备2019-09-05 2637

-

单片光学实现下一代设计2019-09-20 3599

-

下一代测试系统:用LXI拓展视野2019-09-26 1887

-

下一代测试系统:用LXI推进愿景2019-10-09 2480

-

面向下一代电视的低功耗LED驱动IC是什么?2021-06-04 1959

-

无线中继在下一代移动通信系统中的应用2010-09-30 1022

-

ADI最新SoundMAX音频解决方案,面向下一代HDTV设2008-09-28 1007

-

下一代宽带无线通信网络信令体系结构2011-05-24 1318

-

下一代信号处理与通信系统怎样设计2017-09-13 958

-

UltraScale如何支持下一代Ultra系统2019-01-08 3282

-

下一代军事通信挑战2022-12-22 1957

-

面向下一代导弹驱动系统的无刷直流电机概述2023-11-22 528

全部0条评论

快来发表一下你的评论吧 !