基于ARM7内核的SWI软中断功能设计方案详解

嵌入式技术

描述

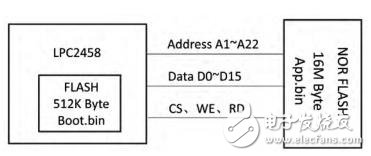

笔者在设计一项目时采用LPC2458。此CPU为ARM7内核,带512K字节的片内FLASH,98k字节的片内RAM,支持片外LOCAL BUS总线,可从片外NOR FLASH启动CPU.由于代码量较大,程序放在片外的NOR FLASH中。且存在片外NOR FLASH在运行程序时,需对片外的NOR FLASH擦写的需求。

图1存储部分原理框图

在设计中,片外NOR FLASH的大小为16M字节。其中2M规划为存放运行程序,剩余的空间用于产品运行日志,告警灯存储空间。因此存在着在程序运行时对片外NOR FLASH擦写的需求。如果程序正在正常运行的片外FLASH中去擦写FLASH,会存在总线冲突的问题,无法实现此功能。我们采用ARM7内核的SWI软中断功能来实现。

ARM软中断原理(SWI)

软中断(SWI)目前没有找到任何官方的正式定义。笔者尝试与硬中断对比定义如下:

1.软中断发生的时间是由程序控制的,而硬中断发生的时间是随机的。

2.软中断是由程序调用发生的,而硬中断是由外设引发的。

3.硬中断处理程序要确保它能快速完成它的任务,这样程序执行时才不会等待较长的时间。

在C程序中调用软件中断需要用到编译器的扩展功能,使用关键字“_SWI”来声明中断函数。注意软中断号码同时在函数定义时指定。

_swi(0x24) void my_swi(void);

这样当调用函数my_swi的时候,就会用“SWI 0X24”来代替普通的函数调用“BL my_swi”。

可以发现软件中断同样存在着中断分支的问题,即需要根据中断号码来决定调用不同的处理程序。软中断号码只存在于SWI指令码当中,因此需要在中断处理程序中读取触发中断的指令代码,然后提取中断号信息,再进行进一步处理。下面是软中断指令的编码格式:

ARM状态下的SWI指令编码格式,32位长度,其中24位是中断编号。

Thumb状态下的SWI指令编码格式,16位长度,其中低8位是中断编号。

为了在中断处理程序里面得到SWI指令的地址,可以利用LR寄存器。每当响应一次SWI的时候,处理器都会自动保存并调整LR寄存器,使里面的内容指向SWI下一条指令的地址,所以把LR里面的地址内容上溯一条指令就是所需的间隔不一样,如果进入SWI执行前是在ARM状态下,需要通过LR-4来获得SWI指令地址,如果是在Thumb状态下进入,则只有LR-2就可以了。

下面是一段提取SWI中断号码的例程:

MRS R0,SPSR;检查进入SWI响应前的状态

TST R0,#T_bit;是ARM还是Thumb?#T_bit=0x20

LDRNEH R0,[LR, #-2];是Thumb,读回SWI指令码

BICNE R0, R0, #0xff00;提取低8位

LDREQ R0, [LR, #-4];是ARM,读回SWI指令码

BICEQ R0, #ff000000;提取低24位;

寄存器R0中的内容是正确的软中断编号了。

-

NXP的ARM7带ucos中硬中断与软中断响应详细分析2011-12-02 5237

-

ARM SWI中断2012-12-04 2678

-

ARM7你们都还使用吗2014-04-23 3292

-

ARM7/ARM9内核的控制器复位2021-08-20 1659

-

软中断SWI怎么使用?2021-11-16 1810

-

ARM Cortex-M3嵌入式内核与ARM7的区别在哪2022-04-13 4759

-

ARM指令集中SWI中断指令实现2022-04-29 8490

-

在SWI软中断指令中LR中放的是异常模式下的返回地址求解2023-02-27 1186

-

ARM内核的中断技术2009-04-09 636

-

ARM7内核上的uCOS II嵌入式系统移植2009-11-12 679

-

采用ARM7网络型汽车防盗系统的设计方案2010-03-07 1291

-

ARM7内核的中断屏蔽方法2011-06-27 8365

-

ARM7嵌入式系统的中断设计与中断处理优化2011-08-16 1342

-

ARM7软中断设计分析2017-10-15 728

-

ARM Cortex-M3内核微控制器与ARM7的区别资料下载2021-04-17 1351

全部0条评论

快来发表一下你的评论吧 !