加法器内部电路原理

数字电路图

描述

一、加法器

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。 加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

加法器的类型

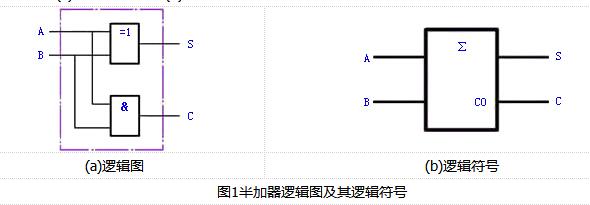

以单位元的加法器来说,有两种基本的类型:半加器和全加器,半加器有两个输入和两个输出,输入可以标识为 A、B 或 X、Y,输出通常标识为合 S 和进制 C。A 和 B 经 XOR 运算后即为 S,经 AND 运算后即为 C。

全加器引入了进制值的输入,以计算较大的数。为区分全加器的两个进制线,在输入端的记作 Ci 或 Cin,在输出端的则记作 Co 或 Cout。半加器简写为 H.A.,全加器简写为 F.A.。

半加器:半加器的电路图半加器有两个二进制的输入,其将输入的值相加,并输出结果到和(Sum)和进制(Carry)。半加器虽能产生进制值,但半加器本身并不能处理进制值。

全加器:全加器三个二进制的输入,其中一个是进制值的输入,所以全加器可以处理进制值。全加器可以用两个半加器组合而成。

注意,进制输出端的最末个OR闸,也可用XOR闸来代替,且无需更改其余的部分。因为 OR 闸和 XOR 闸只有当输入皆为 1 时才有差别,而这个可能性已不存在。

二、加法器电路原理图图解

在计数体制中,通常用的是十进制,它有0,1,2,3,…,9十个数码,用它们来组成一个数。但在数字电路中,为了把电路的两个状态(1态和0态)和数码对应起来,采用二进制较为方便,二进制只有0和1两个数码。

十进制是以10为底数的计数体制,例如

二进制是以2为底数的计数体制,例如

二进制数11011相当于十进制数27。

二进制加法器是数字电路的基本部件之一。二进制加法运算同逻辑加法运算的含义是不同的。前者是数的运算,而后者表示逻辑关系。二进制加法是“逢二进一”,即1+1=10,而逻辑加则为1+1=1。

1、半加器

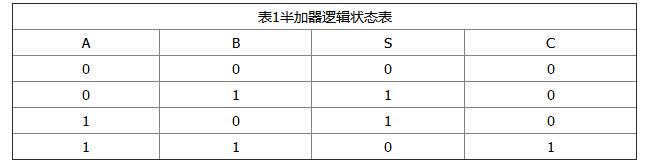

所谓“半加”,就是只求本位的和,暂不管低位送来的进位数。半加器的逻辑状态表见表1。

其中,A和B是相加的两个数,S是半加和数,C是进位数。

由逻辑状态表可写出逻辑式:

并由此画出图1(a)的逻辑图。图1(b)是半加器的逻辑符号。

2、全加器

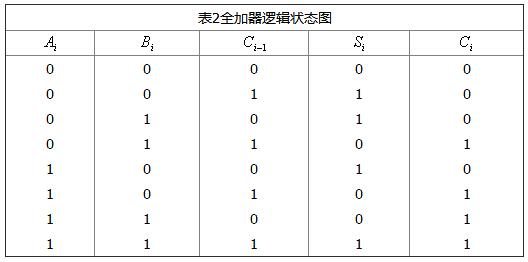

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数 ,还有一个来自低位送来的进位数

,还有一个来自低位送来的进位数 。这三个数相加,得出本位和数(全加和数)

。这三个数相加,得出本位和数(全加和数) 和进位数

和进位数 ,这就是“全加”,表2是全加器的逻辑状态表。

,这就是“全加”,表2是全加器的逻辑状态表。

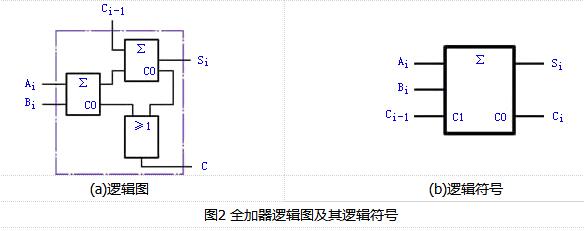

全加器可用两个半加器和一个或门组成,如图2(a)所示。 在第一个半加器中相加,得出的结果再和

在第一个半加器中相加,得出的结果再和 在第二个半加器中相加,即得出全加和

在第二个半加器中相加,即得出全加和 。两个半加器的进位数通过或门输出作为本位的进位数

。两个半加器的进位数通过或门输出作为本位的进位数 。图2(b)是全加器的逻辑符号。

。图2(b)是全加器的逻辑符号。

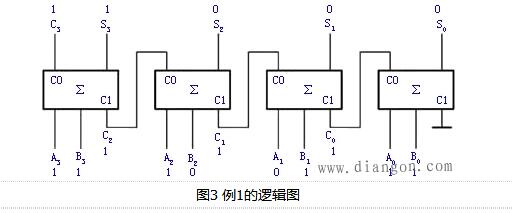

例1、用4个全加器组成一个逻辑电路以实现两个4位的二进制数A—1101(十进制为13)和B—1011(十进制为11)的加法运算。

解:

逻辑电路如图3所示,和数是S—11000(十进制数为24)。根据全加器的逻辑状态表自行分析。

这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行。这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速度要求不高的设备中,仍不失为一种可取的全加器。T692集成加法器就是这种串行加法器。

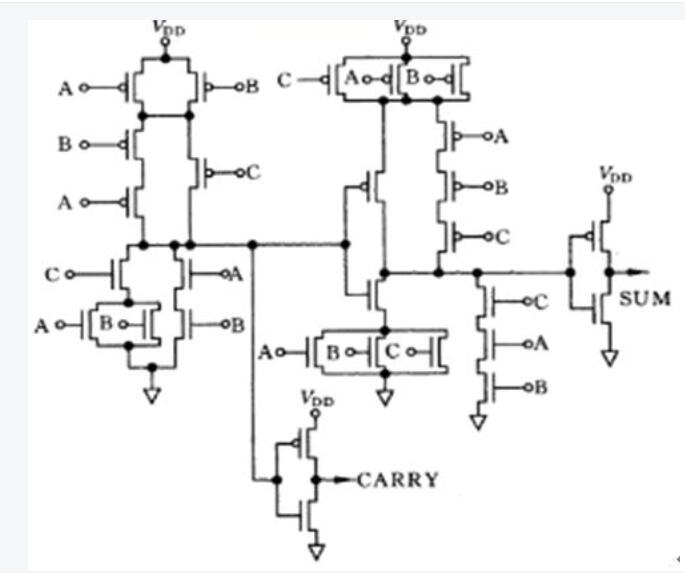

三、加法器内部电路图

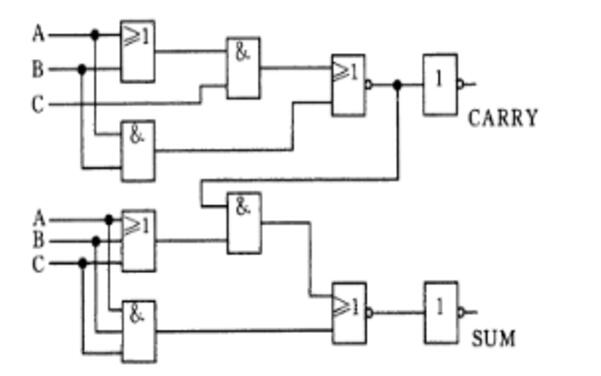

四、加法器内部原理图

- 相关推荐

- 热点推荐

- 加法器

-

同相加法器和反相加法器的区别是什么2024-05-23 5800

-

镜像加法器的电路结构及仿真设计2023-07-07 5560

-

加法器的原理及采用加法器的原因2023-06-09 6884

-

超前进位加法器是如何实现记忆的呢2022-08-05 2662

-

加法器设计代码参考2021-05-31 1264

-

什么是加法器?加法器的原理是什么 ?2021-03-11 5227

-

加法器工作原理_加法器逻辑电路图2021-02-18 35286

-

同相加法器电路原理与同相加法器计算2016-09-13 59054

-

FPU加法器的设计与实现2012-07-06 1298

-

十进制加法器,十进制加法器工作原理是什么?2010-04-13 14596

-

加法器,加法器是什么意思2010-03-08 5968

-

4位并行的BCD加法器电路图2009-03-28 14746

全部0条评论

快来发表一下你的评论吧 !